¿Qué es un entorno de diseño integrado para electrónica?

El descubrimiento tardío de restricciones mecánicas es una causa común de retrasos en el cronograma y retrabajo en proyectos de electrónica.

Considere un escenario típico: tres meses después de iniciado un diseño, el esquemático está completo y el layout de la PCB está prácticamente terminado. Solo entonces el cliente menciona que una segunda PCB va montada unos pocos milímetros por encima de la placa principal, algo que asumía que era evidente a partir de fotos anteriores. En ese momento, los conectores y componentes seleccionados previamente son demasiado altos, lo que obliga a volver a seleccionar piezas que ya son difíciles de conseguir debido a los requisitos de voltaje y corriente. Se pierden varias semanas de trabajo resolviendo una restricción que nunca se documentó formalmente.

Este tipo de problema no es inusual. Es una consecuencia predecible de flujos de diseño desconectados.

Conclusiones clave

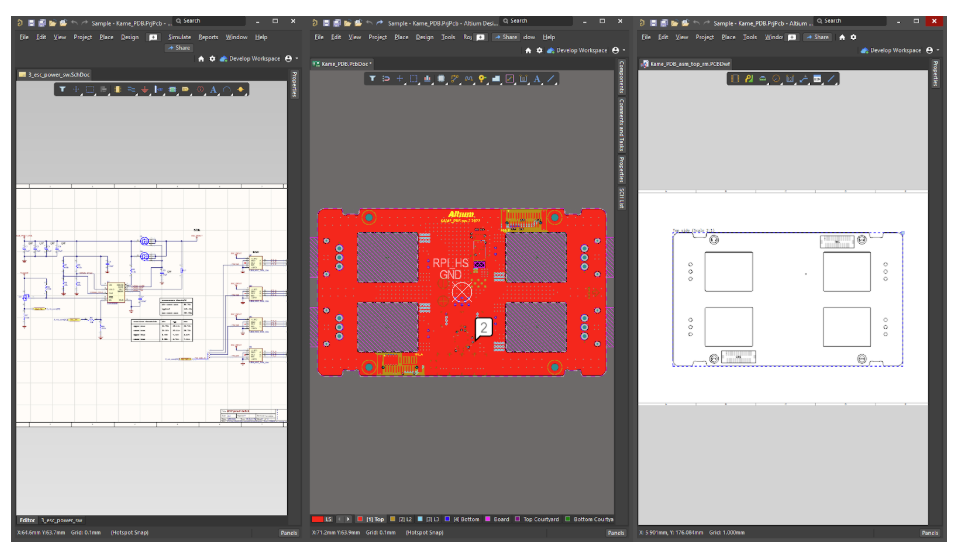

- Un entorno de diseño integrado combina captura esquemática, layout de PCB, simulación, colaboración MCAD y gestión de datos para que los ingenieros no se vean obligados a pasar de una herramienta desconectada a otra.

- Las reglas y restricciones de diseño (como separación, espaciamiento y altura de componentes) deben verificarse en tiempo real durante el diseño, no después de que los archivos se liberen para fabricación.

- Las restricciones mecánicas y de firmware deben introducirse al comienzo de un proyecto. Descubrirlas después de la selección de componentes conduce a retrabajo y demoras innecesarias.

El problema: seis herramientas para construir una sola placa

En muchos equipos de hardware, el flujo de diseño está repartido entre múltiples herramientas desconectadas. Las definiciones de pad stack pueden estar en una aplicación. Los símbolos esquemáticos y las bibliotecas se gestionan en una herramienta aparte y a menudo se almacenan en distintas carpetas locales o de red. El layout de PCB se realiza en otro lugar. La integración del sistema, la integridad de señal y el análisis EMI suelen llevarse a cabo en aplicaciones adicionales y especializadas. El seguimiento de proyectos y la gestión de tareas suelen estar basados en web y no siempre son accesibles cuando los ingenieros trabajan sin conexión.

Como resultado, los ingenieros deben aprender y mantener competencia en al menos cinco herramientas diferentes solo para llevar un diseño desde la captura esquemática hasta una PCB fabricable.

En equipos pequeños, esta fragmentación genera una sobrecarga adicional. Pasar de una herramienta a otra requiere exportaciones e importaciones frecuentes de archivos, con el riesgo de errores de traducción en cada paso. Las bibliotecas y footprints deben colocarse en estructuras de directorios específicas para seguir siendo utilizables; un archivo mal ubicado puede impedir que un componente se transfiera correctamente del esquemático al layout.

Se pierde un tiempo considerable localizando símbolos esquemáticos, footprints de PCB y las versiones correctas de los archivos, una tarea que debería ser trivial pero que a menudo consume días o semanas a lo largo de un proyecto.

A pesar de la cantidad de herramientas involucradas, la coordinación final sigue dependiendo de correos electrónicos y hojas de cálculo. Las propias herramientas permanecen en gran medida desconectadas, ofreciendo poca visibilidad compartida a lo largo del proceso de diseño.

Qué significa realmente un entorno de diseño integrado

Un entorno de diseño integrado para electrónica es una sola aplicación, o un conjunto de herramientas estrechamente acopladas, que admite todo el flujo de diseño de hardware:

- Captura esquemática para el diseño de circuitos

- Layout de PCB para colocación de componentes y ruteo

- Simulación para validación previa a la fabricación

- Colaboración ECAD-MCAD para que los equipos eléctricos y mecánicos trabajen con los mismos datos

- Gestión de datos para bibliotecas de componentes, archivos de proyecto y requisitos de diseño

En un entorno integrado, los mismos datos subyacentes se utilizan en todas las etapas del diseño. Los cambios realizados en el esquemático se propagan directamente al layout de la PCB. Las restricciones mecánicas, como los contornos de la placa o las holguras del gabinete, son visibles en el entorno de diseño eléctrico a medida que se actualizan.

Esto elimina las exportaciones manuales, las importaciones de archivos y los desajustes de versiones que son comunes en cadenas de herramientas construidas en torno a aplicaciones desconectadas.

- Para una explicación detallada de cómo funciona esto en la práctica entre equipos eléctricos y mecánicos, consulte la colaboración ECAD-MCAD en Altium Develop.

Cómo la integración cierra el ciclo de retroalimentación

Aquí tiene un escenario común en un proyecto de electrónica de potencia. El layout de la PCB se crea en una herramienta, la captura esquemática se realiza en otra y el gabinete se diseña por separado en PTC Creo por el ingeniero mecánico. Ninguno de estos entornos comparte datos de diseño en vivo.

En este caso, el gabinete apenas acomodaba la PCB y los conjuntos de cables incumplían los requisitos de espaciamiento. Estos problemas no eran errores de diseño de forma aislada. Ocurrieron porque ningún entorno único proporcionaba visibilidad del contexto mecánico y eléctrico completo. Resolver los conflictos requirió múltiples idas y vueltas entre los equipos eléctricos y mecánicos y añadió de dos a tres semanas al cronograma.

Cuando las herramientas ECAD y MCAD están integradas, este ciclo de retroalimentación se cierra. El ingeniero mecánico define el contorno de la placa y las restricciones directamente desde el modelo del gabinete, y esas restricciones se propagan al layout de la PCB. El ingeniero eléctrico ve de inmediato el área disponible de la placa, las ubicaciones validadas de los orificios de montaje y los límites de altura de los componentes antes de comprometerse con la selección de piezas o decisiones de ruteo.

Esta sincronización bidireccional reduce iteraciones, evita conflictos en etapas tardías y acorta los ciclos generales de diseño.

- Para obtener detalles adicionales sobre la colaboración ECAD-MCAD, consulte la documentación de MCAD CoDesigner.

La validación en tiempo real de reglas de diseño salva sus placas

Las vías de retorno, las violaciones de separación y los errores de espaciamiento para diseño para fabricación o diseño para ensamblaje son causas comunes de retrabajo y nuevas iteraciones de PCB. Estos problemas suelen pasar desapercibidos cuando las reglas de diseño solo se verifican después de completar el layout.

La validación en tiempo real de reglas de diseño marca las infracciones en el momento en que se introducen. Si se viola una restricción de separación, esto es visible de inmediato. Si el ancho de una pista no cumple los requisitos de su clase de red asignada, el error se resalta directamente en el layout.

Este enfoque difiere de las verificaciones de reglas de diseño por lotes, que identifican problemas solo después de que el trabajo de diseño está completo. Las verificaciones por lotes revelan problemas que pueden haberse introducido horas o días antes. La verificación en tiempo real evita que estos errores se propaguen al aplicar las restricciones durante el layout.

El costo real de “funciona bien”

“Nuestra cadena de herramientas actual funciona bien” a menudo significa que el proceso es frágil.

En un proyecto, se utilizó software de captura esquemática para el diseño de cables y arneses. Aunque era técnicamente posible, la herramienta no estaba diseñada para ese propósito. Como resultado, los cambios eléctricos no se propagaban automáticamente a los planos, y cada etiqueta y campo de texto tenía que actualizarse manualmente.

Esto generó fallas previsibles. Se fabricaron varios conjuntos de cables con cableado incorrecto porque la documentación no estaba sincronizada con el diseño real. Los ingenieros dedicaron un tiempo considerable a revisar, volver a comprobar y corregir errores que la propia herramienta debería haber evitado. La productividad individual cayó a un estimado del 40-50% debido a la sobrecarga constante de actualizaciones manuales y verificación.

El sistema funcionaba, pero solo en el sentido de que no fallaba de inmediato. El costo real de “funciona bien” se pagó en retrabajo, demoras y menor capacidad de ingeniería.

Cuando firmware y mecánica aparecen tarde

En un proyecto reciente, el diseño de la PCB principal estaba terminado, la lista de materiales finalizada y el diseño listo para liberarse a fabricación.

En ese momento surgió una nueva restricción: una placa LED secundaria se montaría encima de la placa principal, con solo 10 mm de holgura vertical.

Este requisito tardío obligó a rediseñar el área afectada. Los conectores existentes excedían la altura permitida. No había componentes con suficiente capacidad de corriente disponibles en encapsulados de bajo perfil. Las piezas alternativas que cumplían el requisito de altura tenían cantidades mínimas de pedido poco prácticas o ya estaban obsoletas.

Se dedicaron aproximadamente cuatro semanas a evaluar alternativas, lo que resultó en $2,000 en costos adicionales de consultoría (aproximadamente el 10% del presupuesto total del proyecto) solo para determinar que el enfoque de diseño original no era viable.

Agravando el problema, los cierres por el Año Nuevo chino retrasaron la fabricación. Las placas que deberían haberse enviado en octubre o noviembre no se entregaron hasta marzo.

La causa raíz no fue una falla técnica, sino una falla de proceso. Las restricciones mecánicas no se comunicaron al inicio del proyecto, y no existía un entorno compartido donde los equipos eléctricos, mecánicos y de firmware pudieran ver y validar los requisitos a nivel de sistema al principio del ciclo de diseño.

Por qué todo necesita funcionar en conjunto

Los sistemas de software a menudo pueden tolerar fallas parciales. Si una función se rompe, otras partes de la aplicación pueden seguir ejecutándose, lo que permite corregir los problemas de forma incremental.

Los sistemas de hardware no se comportan de esta manera.

Si la arquitectura de potencia es incorrecta, si los level shifters se aplican incorrectamente o si fallan interfaces fundamentales, grandes partes de la placa no funcionarán, o el sistema puede no encender en absoluto. El hardware requiere un alto grado de corrección en todos los subsistemas antes de que pueda comenzar una prueba significativa.

Debido a que el hardware es inherentemente integrado, el proceso de desarrollo también debe estar integrado. Los requisitos no pueden vivir en hilos de correo electrónico. Las reglas de diseño no pueden verificarse solo al final del proceso de layout. Las restricciones mecánicas no pueden descubrirse meses después de iniciado el desarrollo sin introducir retrabajo y demoras.

Las herramientas de diseño deben reflejar esta realidad. Los datos eléctricos, mecánicos y de componentes deben estar conectados, visibles y accesibles durante todo el ciclo de diseño, no gestionados como archivos desconectados y transferencias manuales.

Para los equipos listos para dejar atrás la cadena de herramientas desconectada, Altium Develop es un buen punto de partida.

Tanto si necesita desarrollar electrónica de potencia confiable como sistemas digitales avanzados, Altium Develop une cada disciplina en una sola fuerza colaborativa. Libre de silos. Libre de límites. Es donde ingenieros, diseñadores e innovadores trabajan como uno solo para cocrear sin restricciones. ¡Experimente Altium Develop hoy mismo!

Preguntas frecuentes

¿Qué es un entorno de diseño integrado para electrónica?

Un entorno de diseño integrado reúne la captura esquemática, el layout de PCB, la simulación, la colaboración ECAD-MCAD y la gestión de datos en un único flujo de trabajo conectado. En lugar de mover archivos entre herramientas separadas, los ingenieros trabajan con datos compartidos para que los cambios se propaguen automáticamente entre las etapas del diseño.

¿Cómo reduce un entorno integrado el retrabajo y los retrasos en el cronograma?

Al validar en tiempo real las restricciones eléctricas, mecánicas y de fabricación, problemas como violaciones de separación, límites de altura de componentes o conflictos de ruteo se detectan en el momento en que ocurren, no semanas después. Esto evita rediseños en etapas tardías que normalmente provocan incumplimientos del cronograma y costos adicionales.

¿Por qué es crítica la integración ECAD-MCAD al inicio de un proyecto?

Las restricciones mecánicas, como la geometría de la carcasa, el apilado de placas y la alineación de los conectores, afectan directamente la selección de componentes y las decisiones de disposición. Cuando estas restricciones son visibles desde el principio, los equipos evitan elegir piezas o arquitecturas que más adelante resultan inviables.

¿En qué se diferencia la comprobación de reglas de diseño en tiempo real de las comprobaciones por lotes tradicionales?

La comprobación en tiempo real señala los errores de inmediato cuando se infringe una regla, lo que permite a los ingenieros corregir los problemas antes de que se propaguen. Las comprobaciones por lotes solo identifican los problemas una vez completada la disposición, lo que a menudo requiere un retroceso significativo y retrabajo.