Domínio do Controle de EMI em Design de PCB: Estratégias de Desacoplamento para PDN

Bem-vindo ao quinto artigo da nossa série, Dominando o Controle de EMI em Design de PCB. Neste artigo, vamos aprofundar nas estratégias de distribuição de energia e discutir como otimizá-las para um melhor desempenho de Interferência Eletromagnética (EMI) em seus projetos de PCB.

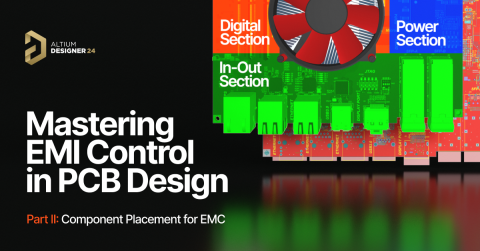

Figura 1 - Exemplo de uma estratégia de desacoplamento no Altium Designer®

Um fator chave no controle de EMI e na melhoria da integridade do sinal em uma placa de circuito impresso digital é a implementação de estratégias eficazes de desacoplamento. Essas abordagens garantem um fornecimento de energia limpo e estável para os Circuitos Integrados (ICs) na sua placa.

Para alcançar isso, os projetistas de PCB precisam criar uma forte Rede de Entrega de Energia (PDN) que atenda às necessidades energéticas de ICs de comutação rápida, garantindo que eles recebam a quantidade certa de corrente da fonte de alimentação. Projetar uma PDN que entregue energia de forma eficiente e no tempo certo pode ser desafiador. Isso requer a redução de perdas e o atendimento às necessidades de impedância para alto desempenho.

À medida que as taxas de dados e as velocidades dos sinais continuam a aumentar, projetar uma Rede de Entrega de Energia (PDN) com baixa impedância torna-se mais importante e também mais difícil. Isso acontece porque o perfil de impedância está intimamente relacionado à frequência dos sinais transmitidos. Equilibrar esses fatores é essencial para manter seus projetos de PCB funcionando bem e minimizar problemas de EMI. Quando se trata de projetar uma PDN eficaz, várias técnicas comuns são utilizadas, como incorporar capacitores de desacoplamento ou usar planos de energia e polígonos de cobre na pilha.

Contudo, alguns métodos amplamente aceitos e mitos provaram ser não apenas ineficazes, mas também prejudiciais ao desempenho da placa.

Antirressonância

Uma técnica popular envolve o uso de múltiplos capacitores de diferentes tamanhos, tipicamente variando de 10nF a 1µF. A ideia é que capacitores maiores fornecem energia aos Circuitos Integrados (ICs), enquanto capacitores menores filtram o ruído de alta frequência. Embora essa abordagem pareça lógica, ela pode realmente ter o efeito contrário ao tentar reduzir a impedância geral da PDN. O motivo pelo qual pode ser contraproducente é que capacitores reais não se comportam idealmente; eles têm efeitos parasitas que se tornam significativos em frequências mais altas.

Os capacitores exibem uma impedância capacitiva apenas até a sua frequência de ressonância. Além deste ponto, os parasitas no pacote do capacitor começam a afetar a impedância, fazendo com que os capacitores se comportem de maneira mais indutiva. Usar capacitores de tamanhos variados na tentativa de alcançar uma capacitância geral mais alta e uma impedância mais baixa pode apresentar desafios significativos. Isso ocorre porque cada capacitor tem seu próprio perfil de impedância distinto, que é influenciado por suas características únicas. Cada capacitor também possui uma frequência de ressonância diferente, levando a uma situação em que esses perfis de impedância se sobrepõem uns aos outros. Essa sobreposição de perfis de impedância resulta em picos de impedância mais altos em frequências específicas. Esses picos ocorrem devido à interação entre as várias frequências de ressonância dos capacitores.

Figura 2 - Anti-ressonância — Efeito de colocar capacitores de diferentes tamanhos com diferentes perfis de impedância em paralelo. Fonte: fresuelectronics.com

Como resultado, o efeito combinado dessas diferentes frequências de ressonância pode criar regiões de impedância aumentada, o que pode impactar negativamente o desempenho geral da PDN e a eficácia da estratégia de desacoplamento.

Para abordar esta questão, é melhor usar capacitores de Dispositivo de Montagem Superficial (SMD) do mesmo tipo e pacote, com a menor indutância de condução possível. Colocar esses capacitores em paralelo ajuda a atender aos requisitos de capacitância enquanto minimiza a indutância em altas frequências. Além disso, alternar as polaridades dos terminais dos capacitores pode reduzir a indutância mútua e diminuir a indutância total da Rede de Distribuição de Energia (PDN).

Posicionamento do Capacitor

Quando se trata do posicionamento de capacitores de desacoplamento, é essencial abordar a questão da indutância, que se torna cada vez mais significativa à medida que as frequências dos sinais aumentam. Para mitigar isso, os capacitores devem ser posicionados o mais próximo possível dos pinos de alimentação dos Circuitos Integrados (CIs) que consomem corrente para sua operação. Colocando os capacitores perto dos CIs, podemos minimizar a distância que a corrente tem que percorrer, reduzindo assim os efeitos indutivos que podem prejudicar o desempenho em altas frequências.

Neste contexto, a principal preocupação do projetista não deve se limitar à distância física que a corrente deve percorrer, mas sim, ele deve considerar cuidadosamente o caminho exato que a corrente segue. Embora seja importante reduzir a distância entre o capacitor de desacoplamento e o pino ao qual está conectado, a razão subjacente para isso é minimizar a indutância parasita associada às trilhas. Esta colocação próxima ajuda a garantir que os capacitores possam fornecer eficazmente a carga necessária aos ICs, ajudando a estabilizar a fonte de alimentação e manter a integridade do sinal.

Figura 3 - Exemplo de colocação do capacitor de desacoplamento ao lado do IC com Altium Designer

Otimizando o caminho, em vez de apenas focar em encurtá-lo, o projetista pode garantir que a corrente flua da maneira mais eficiente possível, reduzindo o potencial para interferência eletromagnética (EMI) e melhorando o desempenho geral do circuito.

Portanto, um planejamento adequado do caminho pode ser tão crítico quanto minimizar a distância em si, pois ambos afetam diretamente os efeitos parasitas que poderiam comprometer a estabilidade e funcionalidade do circuito.

Além de garantir que os capacitores estejam colocados em proximidade próxima aos circuitos integrados (ICs), é altamente recomendável escolher capacitores com a menor Resistência Série Equivalente (ESR) possível. A ESR é um parâmetro crítico porque afeta diretamente a eficiência do capacitor em filtrar ruídos de alta frequência. Uma ESR mais baixa reduz a impedância total entre o capacitor e os pinos de alimentação dos ICs, permitindo uma supressão mais eficaz das flutuações de tensão e ruídos nas linhas de alimentação. Adicionalmente, capacitores com ESR mais baixa tendem a exibir melhor desempenho em uma faixa de frequência mais ampla, contribuindo ainda mais para a redução da interferência eletromagnética (EMI) e melhorando a integridade de potência geral do design.

Planos de Potência

Ao projetar uma placa de circuito impresso (PCB) multicamada, é altamente aconselhável posicionar um par de planos de potência e de referência de retorno, frequentemente referidos como planos de “terra”, próximos um do outro dentro do empilhamento. Colocar esses planos em proximidade aumenta a capacitância distribuída entre eles, o que, por sua vez, reduz a impedância geral da rede de distribuição de potência (PDN).

A configuração ideal envolve posicionar as camadas de sinal adjacentes ao plano de referência de retorno, comumente referido como “Terra de Sinal”. Esse posicionamento estratégico permite que a corrente de retorno flua com área de loop mínima, o que ajuda a confinar os campos eletromagnéticos gerados pelos sinais, controlando assim a interferência eletromagnética (EMI) e reduzindo ruídos. Essa configuração melhora significativamente a integridade do sinal, pois minimiza o acoplamento cruzado e o acoplamento eletromagnético entre as trilhas, garantindo maior qualidade de sinal e comunicação confiável através da PCB. No lado oposto do plano de referência de retorno, o plano de alimentação deve ser colocado. Esse layout garante que o plano de alimentação possa fornecer energia de forma eficaz aos circuitos integrados (CIs) sem interferência do ruído causado por sinais de comutação rápida. Ao separar o plano de alimentação das camadas de sinal, mantendo ao mesmo tempo uma proximidade com o plano de referência de retorno, é possível mitigar o acoplamento de ruído e criar um ambiente estável para a entrega de energia, contribuindo assim para a operação eficiente de todo o circuito. Esse arranjo melhora tanto a integridade da alimentação quanto a integridade do sinal, tornando-se uma prática de design fundamental para PCBs multicamadas de alto desempenho.

Figura 4 - Exemplo de um empilhamento otimizado de 6 camadas com Altium Designer®

Usando tanto capacitores localizados, colocados próximos aos pinos de alimentação dos ICs, quanto tendo planos de alimentação e terra próximos um do outro, fornece uma solução completa. Essa combinação melhora a Rede de Entrega de Energia, reduz a Interferência Eletromagnética (EMI) e mantém uma melhor qualidade de sinal em toda a placa. Além disso, essa abordagem ajuda a distribuir a energia de forma mais uniforme por toda a PCB e reduz a indutância que ocorreria se um método tradicional de roteamento de energia fosse usado.

Ao combinar capacitores bem posicionados com planos de alimentação e terra próximos, você cria um sistema de distribuição de energia mais confiável e eficiente, garantindo que sua PCB tenha um bom desempenho e fique livre de interferências.

Olhando para o futuro, nosso próximo artigo abordará o tema da prevenção de diafonia. Exploraremos estratégias para minimizar a interferência entre sinais e garantir uma comunicação mais limpa e confiável em seus projetos de PCB, com um foco particular nas melhores práticas de EMI. Você pode garantir que não vai perder isso seguindo as páginas e as redes sociais da Altium, assim você fica atualizado com insights valiosos e dicas práticas para aprimorar seus projetos.

Conclusão

Ao trabalhar em projetos avançados de PCB, o Altium Designer® oferece um conjunto abrangente de ferramentas que podem simplificar muito o processo para os designers de PCB e ajudá-lo a criar uma Rede de Entrega de Energia (PDN) eficiente. Uma das principais características do Altium Designer® é o Gerenciador de Empilhamento de Camadas. Esta ferramenta ajuda você a selecionar a configuração de empilhamento ideal para sua PCB com base nas necessidades específicas do seu sistema.

Além disso, o Altium Designer® inclui ferramentas integradas poderosas que permitem realizar simulações detalhadas da sua PDN. Essas simulações ajudam você a analisar e tomar decisões informadas sobre como melhorar o design da sua placa de forma eficaz.

Para elevar seus projetos de design de PCB e aproveitar essas ferramentas avançadas, incentivamos você a iniciar seu teste gratuito do Altium Designer® e do Altium 365™.

Isso lhe dará a oportunidade de experimentar em primeira mão como essa ferramenta CAD completa pode aprimorar suas capacidades de design e levar a designs de PCB mais eficientes e eficazes.