EASY, MODERN AND EVEN MORE POWERFUL

# FEATURES AND BENEFITS

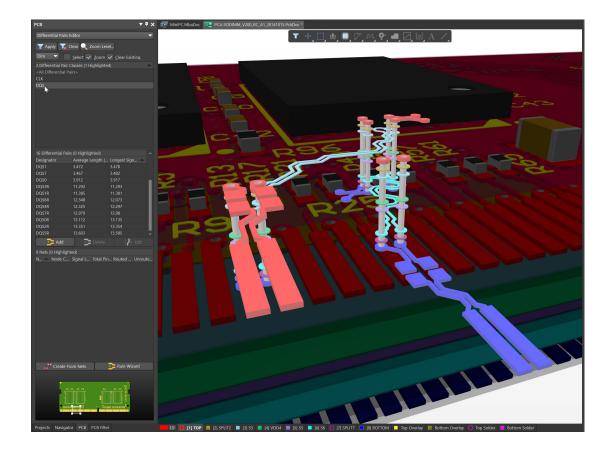

- Superior 3D modeling and collaboration.

- True integrated tool suite for PCB level electronics design.

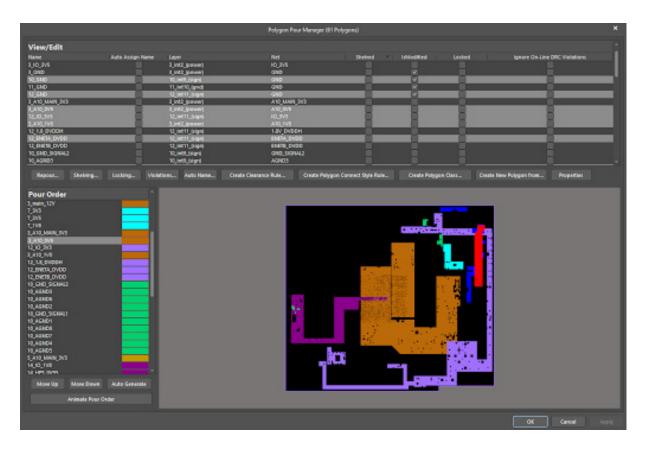

- Visually manage copper pours and pour ordering.

- Streamline PCB pre-routing setup with dynamic smart object placement.

- Accurate materials library and solver-based impedance profiles for high speed and RF design.

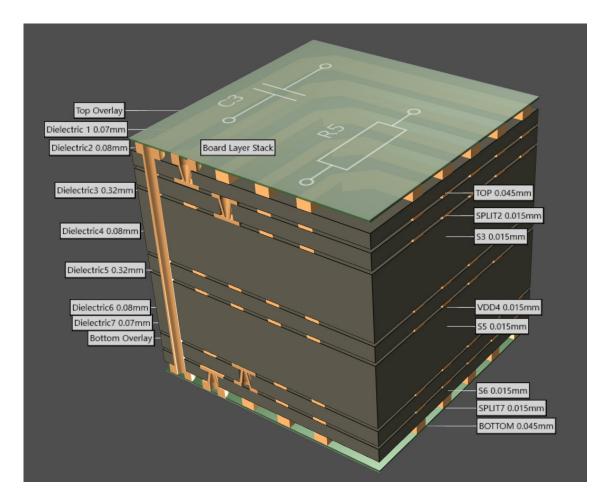

- Advanced layer stack manager for Rigid-Flex, Embedded Components, and Printed Electronics.

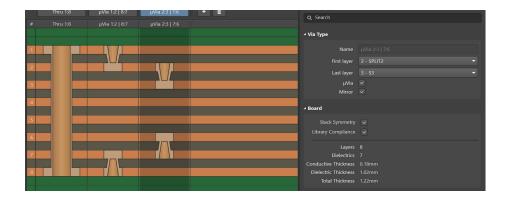

- HDI μVia, SkipVia, blind/buried and back-drills all made easy for modern high-speed designs.

# **BOARD LAYOUT**

Altium Designer® board layout tools addresses the challenges you encounter when laying out even a dense large-component-count designs. It makes shaping your board, organizing and placing components simple and easy, whether it is rigid or flex. With the ability to place and drag components that push, avoid, and snap-to alignment with other objects and pads on your board layout, your boards are always efficiently prepared for routing with minimal clicks and keystrokes.

Without any design limitation to the board size, number of layers, or the complexity of your vias, rest assured your high density interconnect (HDI) or high speed board requirements will always be met. Furthermore, your signal integrity disturbances are reduced on high-speed PCBs with complete control over every drill hole with hole tolerances and back drilling capabilities.

### Native3D™

Altium NATIVE 3D technology gives stunning, realistic 3D modelling with real time clearance checking. Electrical / Mechanical collaboration is simple using the popular STEP / Parasolid mechanical models directly in the design environment.

Users import 3D models and mechanical enclosures from SOLIDWORKS® and other MCAD systems to have the most realistic, accurate, and data-rich 3D models for an exact representation of a physical board without the need for costly prototypes. The IPC-compliant PCB Component Wizard handles any other 3D model needs with a guided process for custom component creation. Reduced prototyping costs resulting in reduced time to market and manufacturing/repin costs.

#### **Visual Layer Stack Management**

Layer stack management allows users to define the material composition and specialized regions on the board. For flex, rigid-flex and rigid PCB designs, the user can control the entire stackup, including all rigid and flex portions with bending angles and individual layer definitions. They can visualize layer stacks anywhere from 2 plus layers using subsets of materials used in the primary layer stack. Each layer has an individual definition and corresponding parametric data.

Complex boards with multiple stackups can be defined side by side to facilitate board construction. Users define and manage all of the layer stackups in a central location to facilitate tracking of layer stack details and minimizing errors and miscommunication on layer details.

Most modern rigid PCBs require multiple layers, often including High Density Interconnects (HDI) for fine-pitch breakout of dense integrated circuits such as CPUs and Memory. Couple the need for high density with the need for high speed signals and PCB designers can have a tough time balancing all the complex design requirements against cost and manufacturing yield. The powerful layer stack manager makes this balancing act much easier.

#### **Layer Stack Impedance Profiles**

Not only are PCB designs becoming smaller, with much greater density. They are continually increasing in signalling edge rates, data throughput, and clock speeds. Accurate impedance profiles are a necessity for maintaining signal integrity in modern designs within the necessary tolerance bands.

From the Layer Stack Manager Materials Library, accurate electrical conductor and dielectric parameters are used with a powerful 2D electromagnetic field solver to calculate width from the target impedance for single-ended and differential pairs, or to calculate accurate impedance from target trace widths and spacing. Users can select any electrical layer in the stack as a reference plane, whether it's a plane layer or not - allowing much greater flexibility and more accuracy in impedance controlled routing. The Design Rules and Constraints for the PCB can then reference any impedance profile to apply the width, spacing and gaps (for diff pairs) rules during interactive routing, ActiveRoute execution, Glossing, and layer changes during PCB design.

### **Materials Library**

The Layer Stack Materials library allows designers to add the characteristics, edit, create and import or export any data from materials manufacturers used in the production of PCBs. User parameters, as well as information such as conductivity, dielectric constants, and other information can be added and used by the Layer Stack Manager and Impedance Profiles.

In addition to traditional cores, prepregs, and copper foils used in PCB product, other materials and conductors can be added to meet any user concept - platings, pastes, dielectric films, and conductive inks for printed electronic devices can all be added, used and maintained in the materials library, and contribute to the Layer Stack Reports for fabrication.

| Altium Material Library                                                                                                                                                                                                                                               |   |      |          |                |              |             |        | × |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----------|----------------|--------------|-------------|--------|---|

| ະ່ກ (≓ r mil in µm mm III)                                                                                                                                                                                                                                            |   |      |          |                |              |             |        |   |

| <ul> <li>Copper plating process</li> </ul>                                                                                                                                                                                                                            |   | Туре | Source T | Process T      | Material     | Color       | T      |   |

| ENIG<br>HASL<br>IAu<br>ISn<br>OSP<br>PCB layer material<br>Conductive layer material<br>Foil<br>Dielectric layer material<br>Core<br>Prepreg<br>Surface layer material<br>Flex Coverlay<br>Soldermask<br>Printed Electronics material<br>Conductive<br>Non-Conductive | 1 | HASL | Altium   | HASL           | PbSn         | #FFF2F2F2F2 |        | - |

|                                                                                                                                                                                                                                                                       |   | HASL | Altium   | HASL Lead-Free | Lead-Free    | #FFF2F2F2   |        |   |

|                                                                                                                                                                                                                                                                       |   | ENIG | Altium   | ENIG           | Nickel, Gold | #FFFFC400   |        |   |

|                                                                                                                                                                                                                                                                       |   | IAu  | Altium   | IAu            | Gold         | #FFFFB200   |        |   |

|                                                                                                                                                                                                                                                                       |   | OSP  | Altium   | OSP            | ENTEK        | #0000000    |        |   |

|                                                                                                                                                                                                                                                                       |   |      | Altium   |                |              | #FFBFBFBF   |        |   |

|                                                                                                                                                                                                                                                                       |   |      |          |                |              |             |        |   |

| Load Save                                                                                                                                                                                                                                                             |   |      |          |                |              |             | Cancel |   |

### HDI µVia, SkipVia Modeling

Advanced layer stack design with µVia, SkipVia and Backdrill modeling and output generation allows you to design modern, dense boards with the latest high-speed devices and packages. Along with the ability to create and support multiple HDI µVia, SkipVia, Blind/Buried and Back Drilled via profiles, the interactive layer stack visualizer allows the designer to explicitly see what is to be fabricated and accurately communicate this manufacturing intent into the design and to the PCB manufacturer.

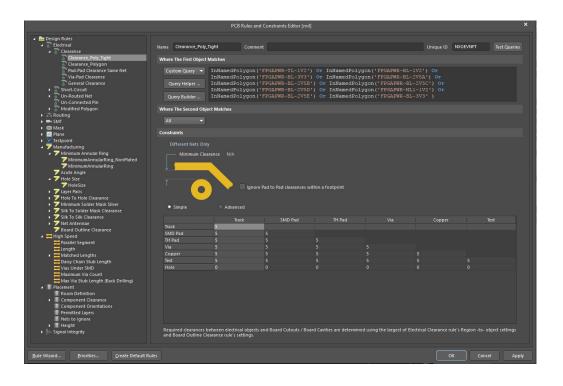

### **Rules Driven Design**

Altium Designer's PCB editor uses design rules to define the requirements of a design. These rules collectively cover every aspect of the design, and form an instruction set for the PCB editor to follow. They cover routing widths, clearances, plane connection styles, routing via styles, and so on. Many of these rules can be monitored in real-time by the online design rule checker (DRC). Altium Designer rules are not attributes of the objects, but rather they are defined independently of the objects, with each rule having a scope that defines which objects it must target.

Altium Designer rules are applied in a hierarchical fashion, For example, the highest-order rule would be a clearance rule for the entire board, then perhaps a clearance rule for a class of nets, then perhaps another for one for the pads in a class. Using the rule priority and the scope, the PCB editor can determine which rule applies to each object in the design. With this flexibility, you can define various design rule sets with varying stringent design requirements, and save them into templates. Taking the time to set up these templates will enable you, and your colleagues, to effectively get on with the job of designing safely, knowing that the rules system is working hard to ensure you are designing against a set of approved requirements.

### Copper/Polygon Pour Management

Copper polygon pours are used to create a solid or hatched (lattice) areas on a PCB layer, using either Region objects, or a combination of Track and Arc objects. They are commonly used to create power planes and signal planes to connect to components and can be used to help with heat distribution. PCB designers generally use filled copper regions to cover the remaining area outside those tracks, pads, and stand-off regions.

In Altium Designer, areas of copper can be defined using three different design objects: Fills, Solid Regions and Polygon Pours. You can interactively place a polygon, or it can be created from a set of existing track and arc objects that define a closed shape. The advantage of a polygon pour is that it automatically creates stand-off regions to copper objects that belong to another net based on design rules. Furthermore, it can fill irregularly shaped areas of a board as they automatically pour around existing objects, connecting only to objects on the same net as the polygon pour.

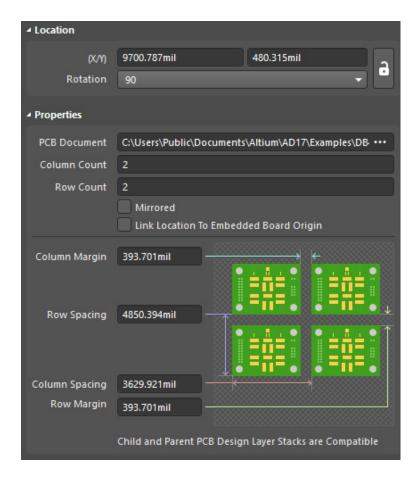

## Panelization

Panelization, also known as step-and-repeat, is the method of placing two or more PCBs onto one panel, which allows boards to be secured during manufacturing, shipping, and assembly. Since your PCB is priced per panel, your cost will be directly impacted by how many PCBs can be fabricated on a panel. Altium Designer panelization feature makes it easy to define a panel, of the same or different board designs. And with the source boards being linked rather than copied, any design change made on the source board, is immediately reflected across the entire panel.

#### **Precise Object Placement**

When designing a PCB, you need to use a variety of objects. Most objects placed in a PCB document will define copper areas or voids. Altium Designer gives you control over two types of objects to work with: **Primitive Objects** and **Group Objects**. Primitive objects are the most basic elements, and include: tracks, pads, vias, fills, arcs, and strings. Anything that is made up of primitives and identified as a design object is a group object. Examples of group objects include: components, dimensions, coordinates, and polygon pours.

Altium Designer makes placing any object the easy and identical, regardless of the object being placed. Simply select an object and use the mouse to define the location of where you want it placed, and right click (or <Esc>). Altium Designer also streamlines placing components with its smart component placement. It makes the effort to align objects easy by dynamically aligning them as they are being dragged. Clear green indicators lines appear when the component is aligned, either with adjacent components or with the pads of adjacent components. Designers can cycle through multiple modes to ensure the component placement process is efficient: Ignore Obstacles, Push Obstacles, and Avoid Obstacles.