Design for Test: Determining the Value of the JTAG Interface During the Schematic Stage

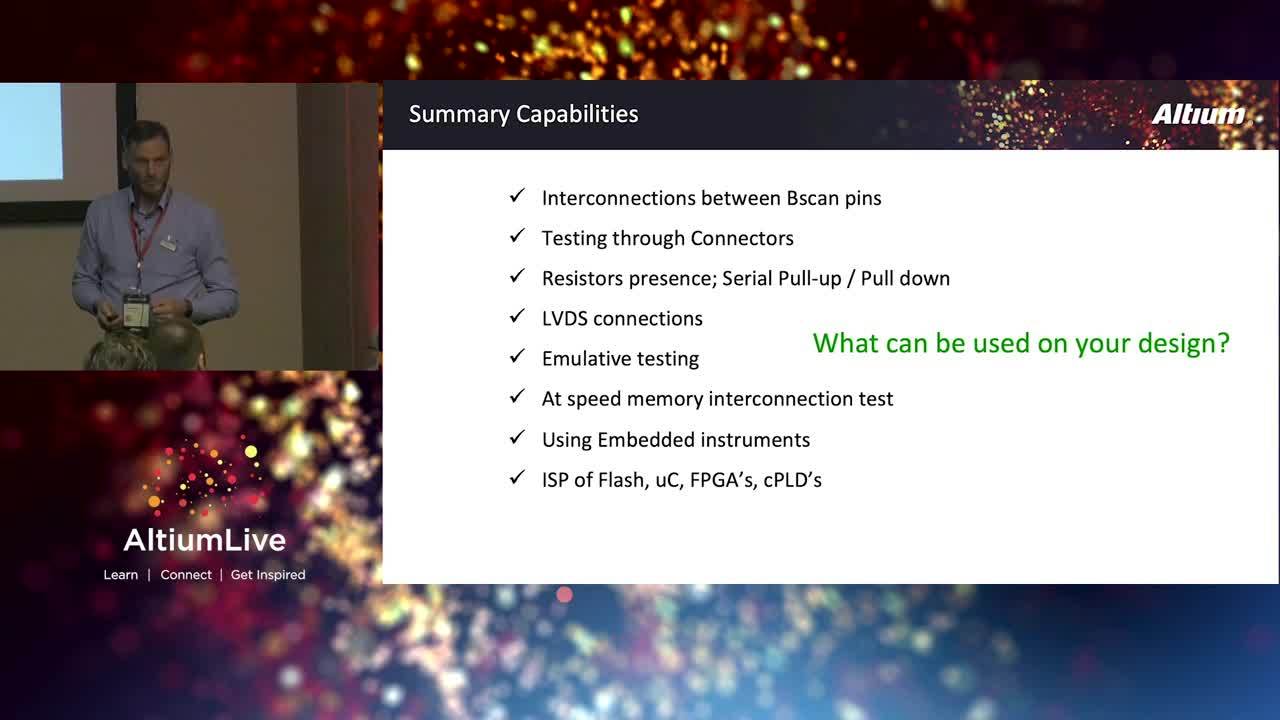

After a brief explanation about modern test methodologies and in-system programming capabilities via the JTAG interface on chip, board, and system level, the focus of this presentation will be on the necessity and ways for improving your design for testing (DFT) and fast in-system programming. This is best done during the schematic stage. Studies and experience show that if you do, your company will substantially save engineering time and build more reliable products.

View the presentation slides:

Sign up to pre-register for AltiumLive next year or try Altium Designer today.

Related Resources

Thank you, you are now subscribed to updates.