Recover Conductor Losses By Clearing Your PCB Ground Layer

Controlled impedance routing at high frequencies is difficult enough, and it's important to make sure that you stay within your loss budget on long routes or in lossy media. When you have to route a long trace or a long differential pair to a connector or another component, what can you do if you're reaching the end of your loss budget?

Most designers will tell you to just use an alternative low-loss/RF material that has a lower-loss tangent whenever losses are excessive on high-speed/high-frequency interconnects. What else can you do if losses are a problem on these long interconnects?

There's one trick that you can use with microstrip lines that are implemented by 5G equipment/handset designers. This is a technique that was described to me as skip reference routing, or just skip routing. The name refers to skipping reference layers at the load end of an interconnect, thereby modifying the field distribution around a microstrip trace and reducing total losses. In this article, we’ll take a look at this routing method and explain how it can help recover some loss budget in a lossy interconnect.

What is Skip Routing?

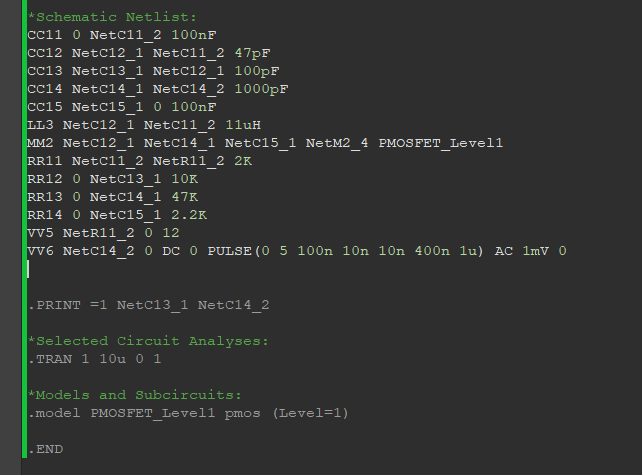

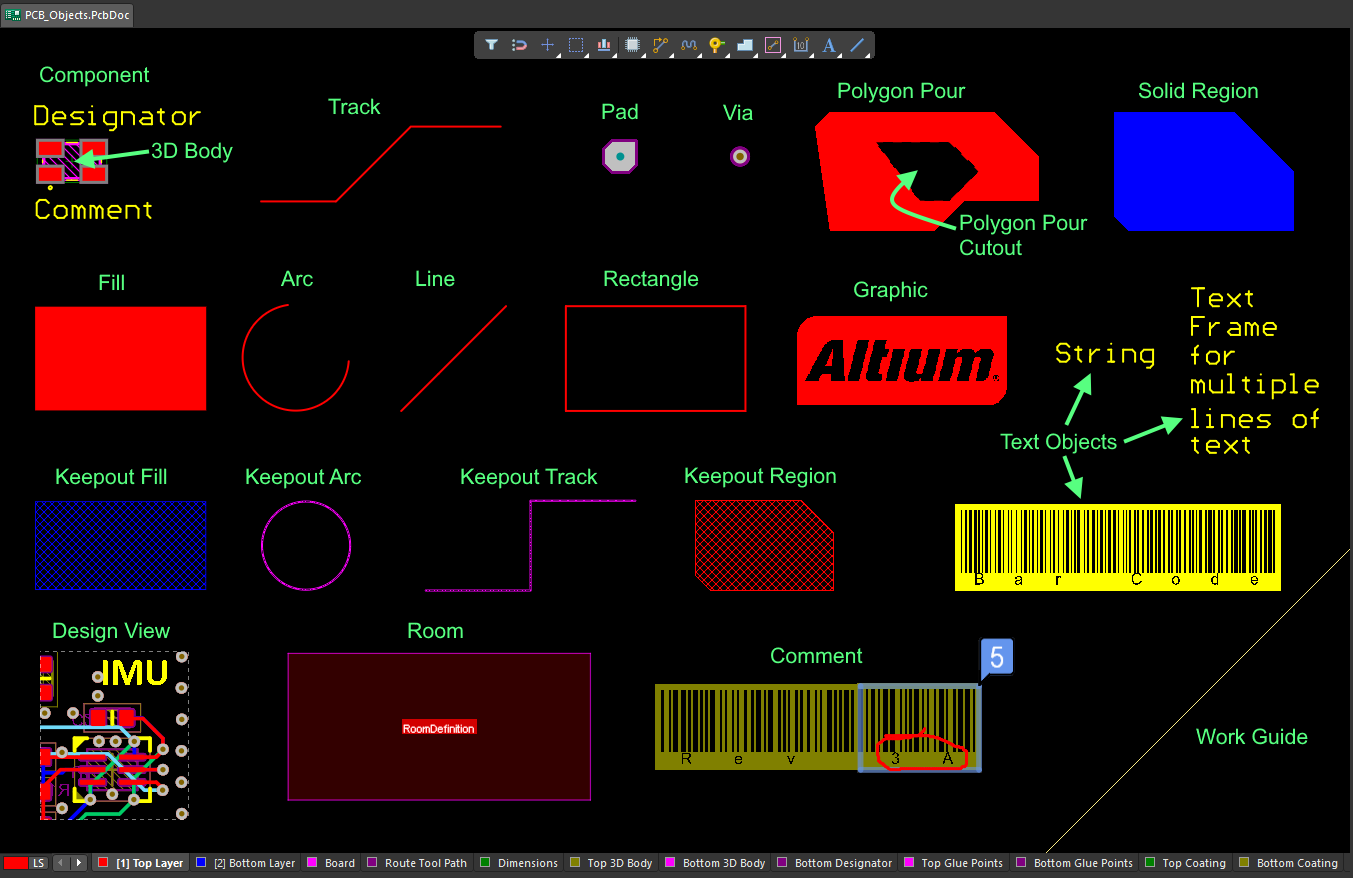

Skip routing involves clearing out some PCB ground layer in the reference layer for a microstrip transmission line at the load end of a route. Once the signal travels into the region with the ground clearance, the signal will experience lower losses. This occurs because the act of shifting the PCB ground layer plane away from the trace modifies the field distribution around the microstrip transmission line. In this way, the transmission line impedance is now referenced to the next nearest layer in the stack-up as long as the two ground regions are set to the same potential. The image below shows how this works.

When clearing out some ground in the region below the destination component, you now have to adjust the width of the microstrip trace on the surface layer so that you can maintain consistent impedance. When the trace enters the region with the cleared ground layer, the trace width needs to be widened within the cleared region to set the impedance in both regions to be equal. This allows you to reduce total insertion losses in the cleared region without creating new return losses at the interface between these regions. I’ve included a small taper in the transition region, which ideally should be electrically short (about 10% of the operating wavelength for RF signals).

Using a Ground Cutout to Reduce Conductor Losses

The loss experienced by the signal will depend on the density of field lines around the microstrip line, but it is not necessarily because the loss tangent changes. Once the nearest ground layer is cleared below the microstrip and the trace is referenced to the next ground layer, the width of the trace can be comfortably increased as this will help the trace hit its impedance target.

How can we get some loss reduction in this trace without somehow changing the loss tangent? The answer lies in the skin effect in the conductor. By widening the conductor to ensure impedance control in the cleared ground layer region, the skin effect losses will be reduced. We can see this if we look at an approximate formula for the skin effect resistance of a conductor with a rectangular cross-section:

Since this is just a resistance value, we should be able to see that increasing the trace width (W) will increase the cross-sectional area, and thus the resistance will decrease. This helps recover a small amount of resistive and reactive losses in the region where the trace width is larger.

Going Coplanar Instead of Using Ground Cutouts

So far, I’ve only discussed what happens when we have regular microstrip lines. What happens if you’ve designed with a grounded coplanar waveguide? The difference is that the width-to-dielectric thickness ratio will be smaller for a coplanar waveguide when the trace-to-ground pour spacing is lower. However, you have another lever you can pull: the spacing between the trace and its nearby ground routing.

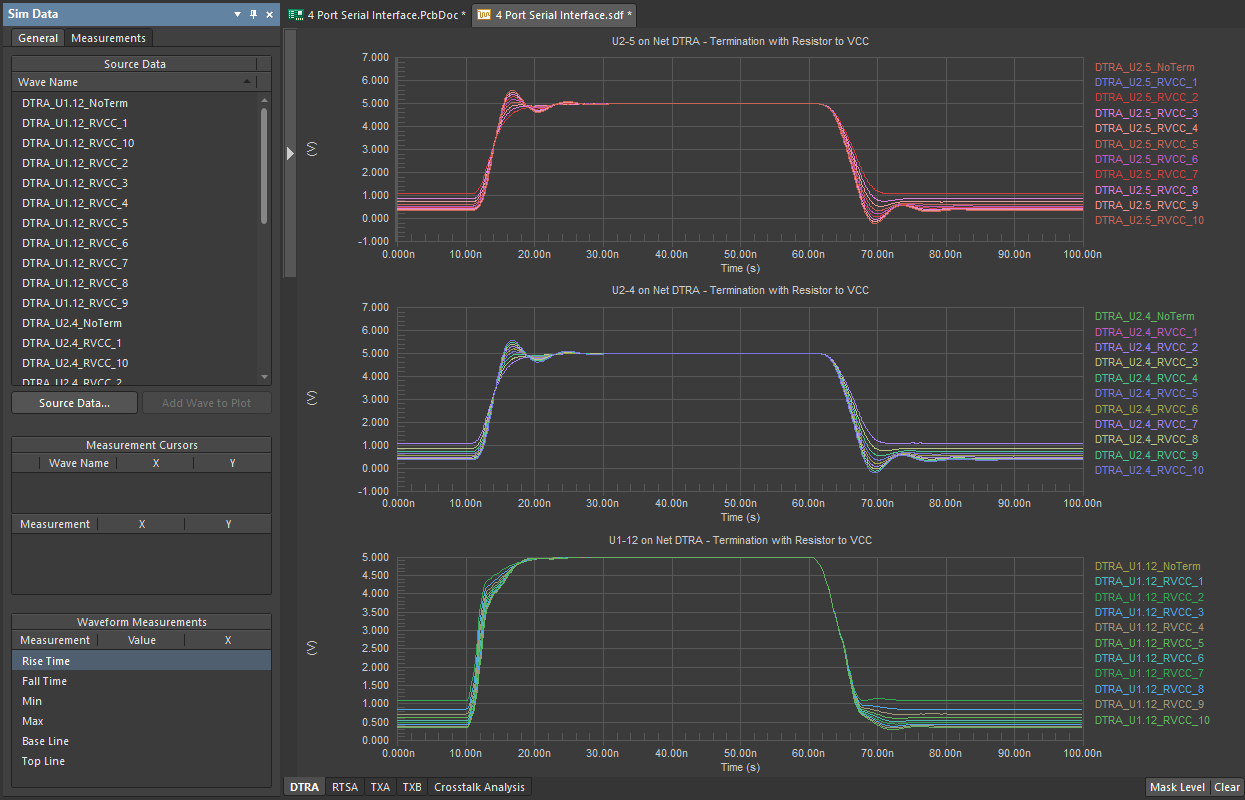

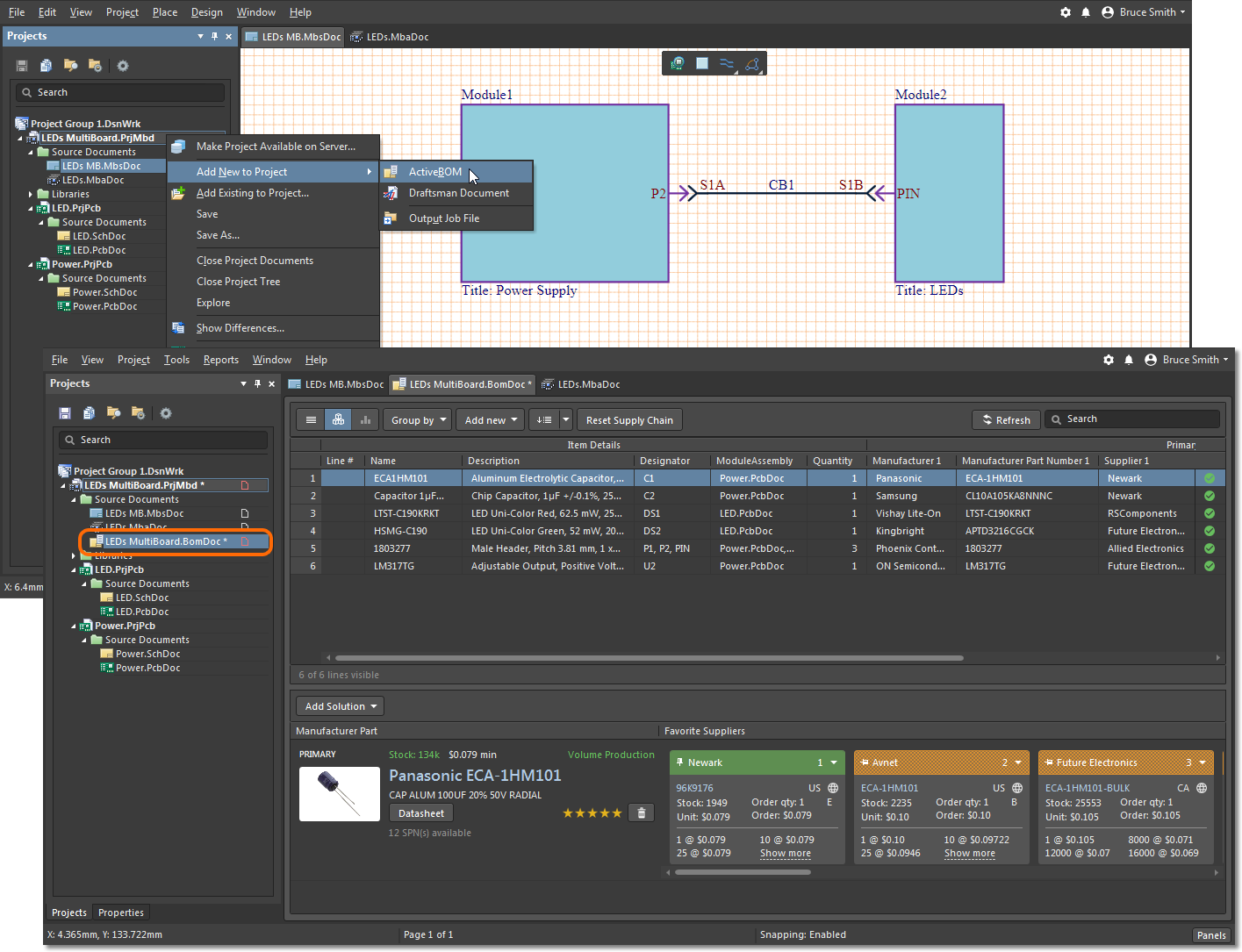

Here, we have another version of skip routing: where we change the spacing coming out of the coplanar waveguide and a microstrip. If you remember an earlier article on microstrip clearances to ground, you’ll notice that bringing ground routing to pour near a microstrip reduces its impedance, which is why we can use a thinner trace in a coplanar waveguide than a microstrip for the same substrate thickness.

The example below shows another way we can recover some losses by transitioning to a wide microstrip from a narrow coplanar waveguide. If you recall my earlier article on microstrip vs. coplanar waveguide losses, you’ll notice that the coplanar trace will have larger PCB conductor losses for a typical rough plating like ENIG. This is (in part) due to the modification of the microstrip line’s losses by roughened plating, which increases the magnitude of the skin effect. By transitioning out of the coplanar line into a microstrip with a taper, the microstrip will have lower losses than the coplanar section.

In this example, we haven’t cleared any of the ground on the next layer. Instead, we just cleared the ground on the same layer and then widened the trace to maintain impedance, Some additional losses would be reduced by going with immersion silver plating instead of ENIG, as well as pulling the solder mask off of these lines as LPI solder mask materials have high loss tangent.

What About Effective Dk?

When the distance from the trace to the ground layer is increased, the field distribution will change and thus the effective Dk value seen by the signal traveling on the trace will also change. One might rightfully ask: what happens to the effective Dk value, and does it change the total losses along the interconnect?

While it is true that changing the trace width modifies the field distribution around the trace, it only slightly changes the effective dielectric constant. This is because the width-to-dielectric thickness ratio required for controlled impedance is only slightly nonlinear for a microstrip, so doubling the dielectric thickness requires very nearly doubling the trace width to reach the same impedance. This gets you back to the same effective Dk value for your microstrips. This should explain why the loss tangent doesn’t need to change in order to get some losses back in your interconnects.

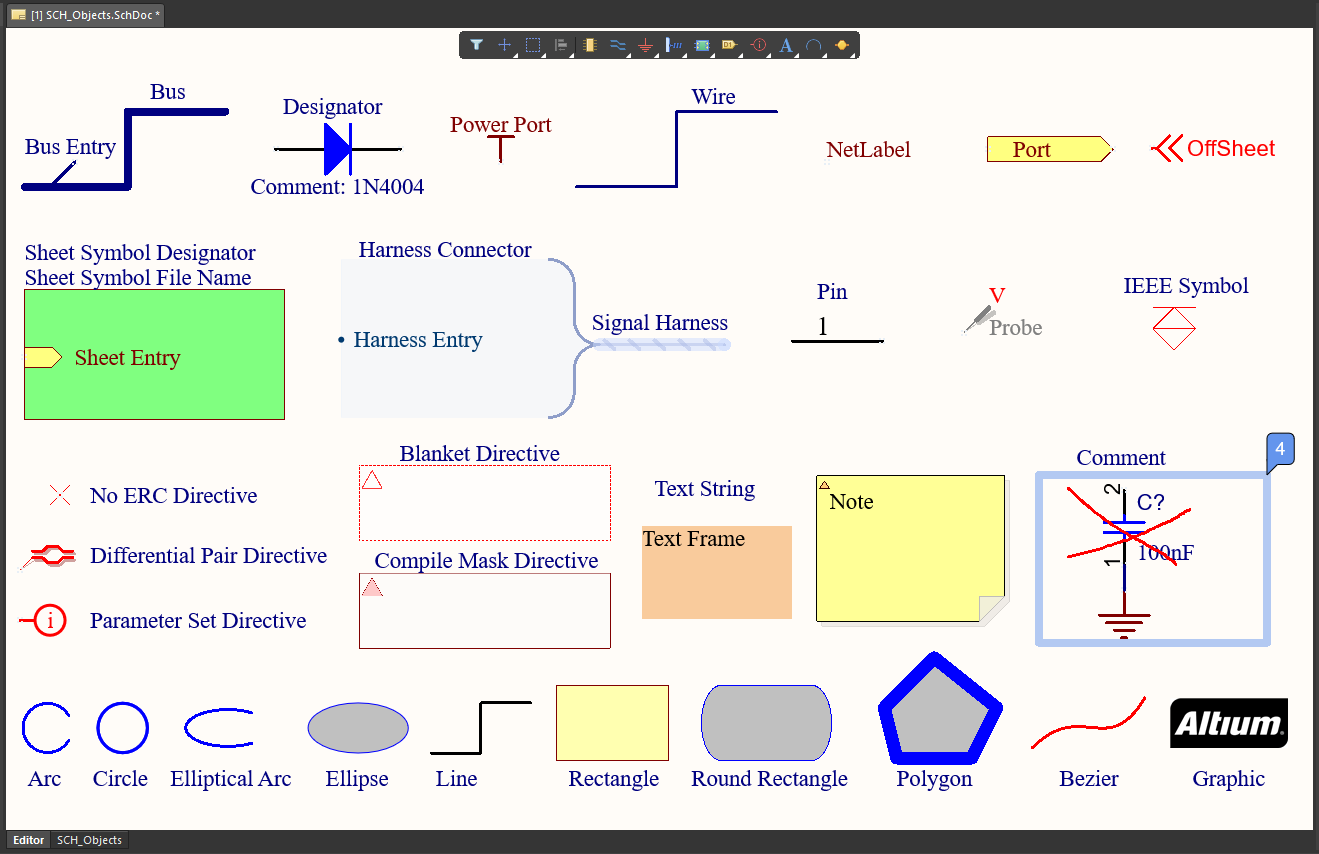

When you need to design and route high-speed and high-frequency interconnects while accounting for PCB conductor losses, use the best set of PCB routing features in Altium Designer®. The integrated design rules engine and Layer Stack Manager give you everything you need to calculate the trace width needed to reach a specific impedance and account for copper roughness in your PCB material system. When you’ve finished your design, and you want to release files to your manufacturer, the Altium 365™ platform makes it easy to collaborate and share your projects.

We have only scratched the surface of what’s possible with Altium Designer on Altium 365. Start your free trial of Altium Designer + Altium 365 today.