### **HDI PCB Design and Manufacturing Guide**

An in-depth look at HDI PCB design

#### **Table of Contents**

Design Basics for HDI and the HDI PCB Manufacturing Process *p3*

What's Different in HDI? p13

Introduction to High Density Interconnects p22

11 HDI Materials You Need to Know p31

HDI Quality and Acceptability Requirements p41

#### Design Basics for HDI and the HDI PCB Manufacturing Process

As the world of technology has evolved, so has the need to pack more capabilities into smaller packages. PCBs designed using high-density interconnect (HDI) techniques tend to be smaller as more components are packed in a smaller space. An HDI PCB uses blind, buried, and micro vias, vias in pads, and very thin traces to pack more components into a smaller area. We'll show you the design basics for HDI and how Altium Designer® can help you create a powerful HDI PCB.

High density interconnect (HDI) printed circuit design and fabrication started in 1980 when researchers started investigating ways to reduce the size of vias in PCBs. The first production build-up or sequential printed boards appeared in 1984. Ever since that time, designers and component manufacturers always look for ways to pack more functions on a single chip and a single board. Today, HDI design and fabrication are codified in the IPC-2315, IPC-2226, IPC-4104, and IPC-6016 standards.

When planning an HDI PCB design, there are some design and manufacturing challenges to overcome. Here is a short list of challenges you may run into when designing an HDI PCB:

- > Limited board workspace area

- Smaller components and tighter spacing

- > Larger number of components on both sides of PCB stackup

- $\blacktriangleright$  Longer trace routes creating longer signal flight times

- > More trace routes required to complete the board

With the right set of layout and routing tools built on a rules-driven design engine, you can violate the normal rules in PCB design and create powerful PCBs with very high interconnect density. Working with high-density PCB routing and fine pitch components is easy when you use advanced PCB design software that is built for HDI PCB design. You can create your new HDI design and plan for the HDI manufacturing process with the world-class design features in Altium Designer.

# What's Different About HDI PCB Design and Manufacturing?

The HDI manufacturing process differs from the traditional PCB manufacturing process in a few simple yet important ways. An important point here is that fabricator limitations will constrain design freedom and will set limits as to how the board can be routed. The use of thinner traces, smaller vias, more layers, and smaller components can still be accommodated in your design software, but accommodating design for manufacturing (DFM) requirements means taking advantage of automation in your design software. The exact DFM requirements depend on the manufacturing process and materials used to build the board. DFM requirements also become important when we consider reliability requirements.

Material selection needs to answer these questions:

- Will the dielectric use chemistry compatible with current chemistry used by core substrate material?

- Will the dielectric have acceptable plated copper adhesion? (Many original equipment manufacturers [OEMs] want >6 lb./in. [1.08 kgm/cm] per 1 oz. [35.6 Qm] copper.)

- > Will the dielectric provide adequate and reliable dielectric spacing between metal layers?

- > Will it meet thermal needs?

- > Will the dielectric provide a desirable "high" Tg for wire bonding and rework?

- Will it survive thermal shock with multiple SBU layers (i.e., solder floats, accelerated thermal cycles, multiple reflows)?

- > Will it have plated, reliable microvias?

There are nine different general dielectric materials used in HDI substrates. IPC slash sheets like IPC-4101B and IPC-4104A cover many of these, but many are not yet specified by IPC standards. The materials are:

- > Photosensitive liquid dielectrics

- > Photosensitive dry film dielectrics

- > Polyimide flexible film

- > Thermally cured dry films

- > Thermally cured liquid dielectric

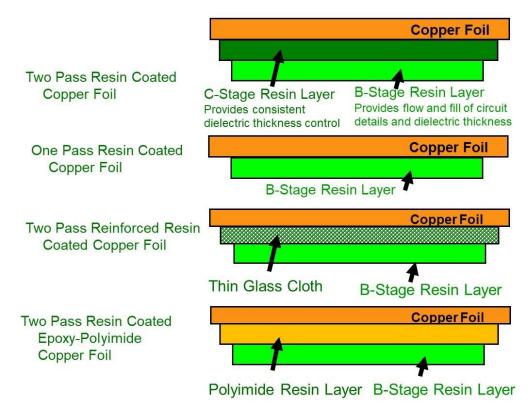

- Resin-coated copper (RCC) foil, dual-layer and reinforced

- Conventional FR-4 cores and prepregs

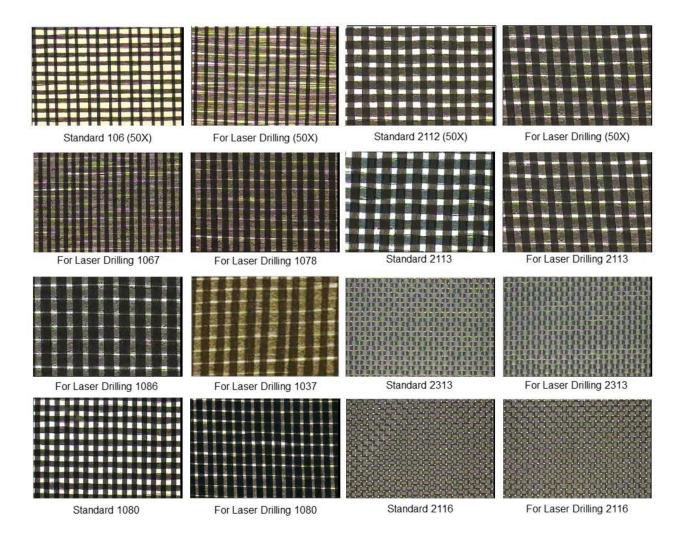

- New 'spread-glass' laser-drillable (LD) prepregs

- > Thermoplastics

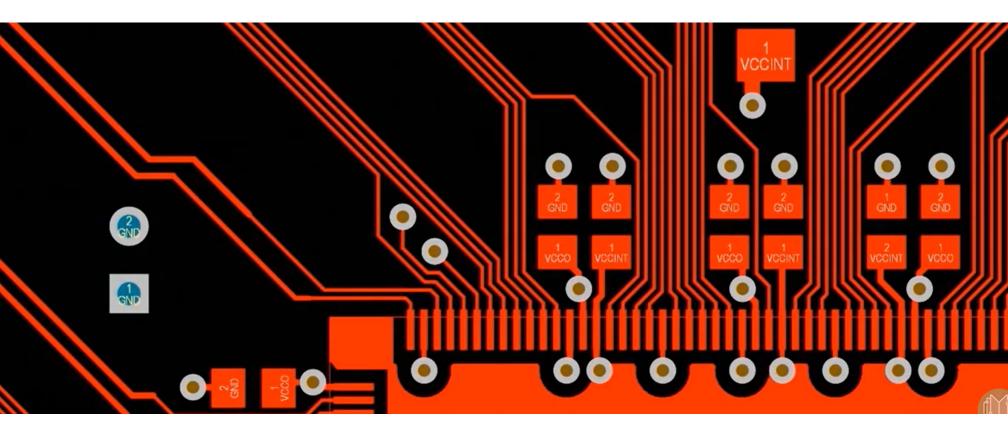

The HDI PCB design process is shown below. Routing efficiencies for HDI are dependent on stackup, via architecture, parts placement, BGA fanout, and design rules. The most important parts of planning your HDI layout are to consider your trace width, via size, and placement/ escape routing for BGA components.

| Plan Design                | Simulate High Speed Geometries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Create Area Fills     |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ļ                     |

| Input Schematic / Netlist  | Adjust Sequence & Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Back Annotate Scemati |

| •                          | The second secon |                       |

| Create Component List      | Test Routability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Compare Netlist       |

| Create Component Libraries | Set-up Routing Rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Design Check          |

| 4                          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                     |

| Enter Mechanical Data      | Route Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Create Test Points    |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                     |

| Set-up Placement Rules     | Check Routings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Generate MFG. Files   |

| Place Components           | Add Planes for PWR & GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Audit Design          |

| T                          | The second secon | +                     |

| Sequence Nets              | Split Plane Generation?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Archive Design        |

General overview of the HDI PCB design and layout process.

Always check with your board house to determine their fabrication methods for HDI PCB manufacturing. You'll need to determine the limits of their fabrication methods as this will influence the feature sizes you can place in your layout. The ball pitch on BGA components will determine the via size you need to use, which then determines the HDI manufacturing process required to create the board. A central feature of your HDI PCB is microvias, which need to be precisely designed to accommodate routing between layers.

HDI PCB Design and Manufacturing Guide | 6

#### **Overview of HDI PCB Design and Manufacturing Processes**

There are a number of steps involved in the typical PCB manufacturing process, but HDI PCB manufacturing uses some particular steps that may not used in other boards. The HDI design process starts like many other processes, where the

- Determine the layer count required to route all signals, either by using the largest BGA component on the board or by using the interface + direction count from the largest IC on the board.

- 2. Contact your fabrication house to select materials and obtain dielectric data to create your PCB stackup.

- 3. Based on layer count and thickness, determine the via style that will be used to route signals through inner layers.

- 4. Perform a reliability assessment if relevant, to verify that the materials will not stress interconnects to fracture during assembly processing and operation.

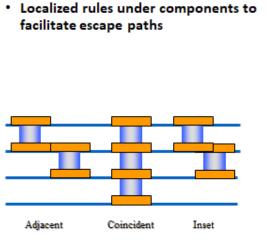

- 5. Determine design rules based on fabricator capabilities and reliability requirements (need for tear drops, trace widths, clearances, etc.) to ensure reliable manufacturing and assembly.

Stackup creation and determination of design rules are the critical points as they will determine ability to route the board and reliability of the end product. Once these points are completed, a designer can implement their fabricators DFM requirements and reliability requirements as design rules in their ECAD software. Doing this on the front-end is very important and it will help ensure the design is reliable, routable, and manufacturable.

.

Altium

#### Design Your Feature Size to Satisfy HDI DFM Requirements

Although DFM requirements relating to clearances in an HDI PCB are quite stringent, these can be accommodated by taking advantage of your design rules in your PCB design software. Some of the important DFM requirements to gather before layout and routing include:

- > Trace width and spacing limits

- Annular ring and aspect ratio limits, especially for high reliability designs

- > Material system used in the board to ensure controlled impedance in the required stackup

- > Impedance profiles for the desired stackup or layer pairs if available

Your design tools are critical for designing your HDI circuit board to satisfy these DFM requirements. Routing impedance controlled traces in your HDI PCB is quite easy with the right set of design tools. You simply create an impedance profile and define your desired trace width while keeping your manufacturer's DFM guidelines in mind. The online DRC engine in your routing software will check your routing as you create your HDI layout. Make sure you get a complete set of specifications for your fabricator's process to ensure you've taken into account all the relevant HDI DFM rules.

### **Types of Vias in HDI PCB Routing**

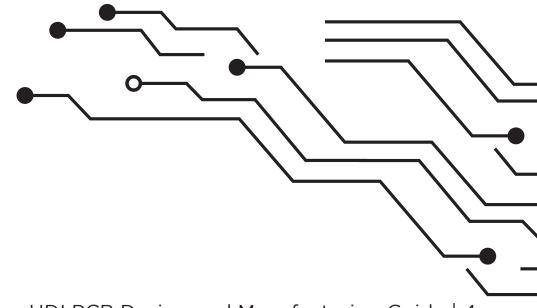

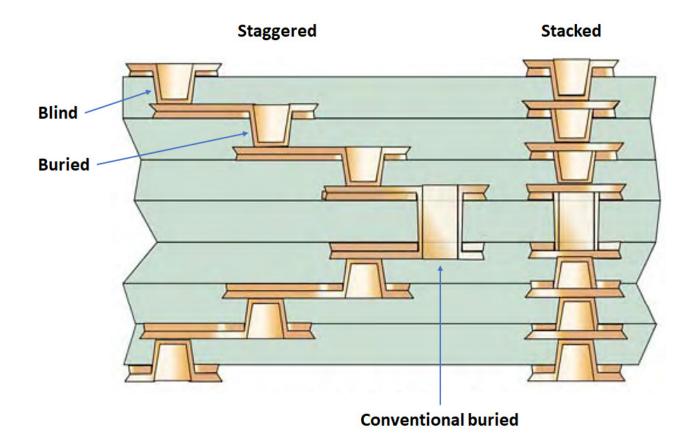

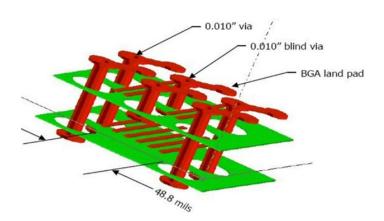

The image below shows the typical via styles that are used in HDI PCB layout and routing. These via styles have low aspect ratio of )(ideally) less than 1, although some manufacturers may provide reliability claims up to aspect ratios of 2, including for stacked microvias. In the center of the PCB stackup is a conventional buried via to provide a connection through the thicker core layer; this inner layer buried via can have a larger aspect ratio as will be mechanically drilled with somewhat . Once the layer count and dielectric thicknesses are determined, the designer can design vias against the aspect ratio limits listed above. Obeying these aspect ratio limits on microvias is an important part of reliability, particularly as these boards pass through reflow, or when deployed in an environment with repeated thermal/ mechanical shocks and cycling.

#### **Sequential Buildup**

The sequential lamination process is predominantly used to build an HDI stackup construction in a layer-by-layer manner. In general, this technique can be used for any multilayer PCB, but it is particularly important for HDI. This is because the high density, very thin dielectrics are formed in individual layers around a thick core, so lamination will happen in multiple steps to build the stackup. The sequential lamination process. This consists of the following steps:

- > Photoresist deposition and exposure: This is used to define areas to be etched, which will leave behind a pattern of conductors on the laminate.

- > Etching and cleaning: The current industry standard etchant is a ferric chloride solution. After etching, the leftover photoresist can be reclaimed and the resulting conductor pattern is cleaned.

- > Via formation and drilling: Vias need to be defined using mechanical or laser drilling. For high via density, the via holes can be removed chemically.

- > Via metallization: Once vias are defined, they are metallized to form a continuous conductive interconnect.

- **Buildup:** Layers are stacked in multiple lamination cycles to build the stackup before outer layer processing.

A flow chart showing the buildup process can be found in the Metalization section below.

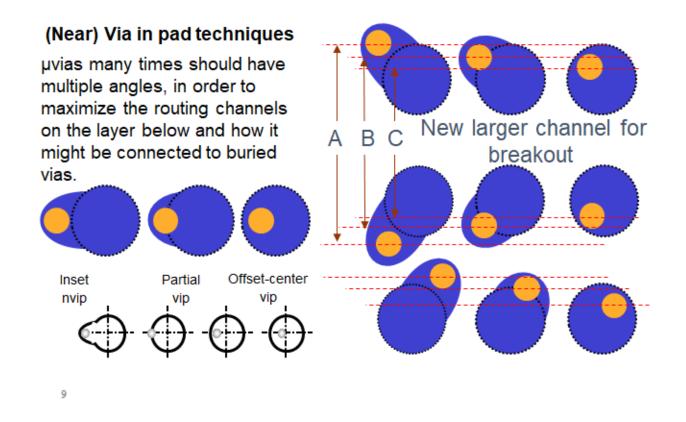

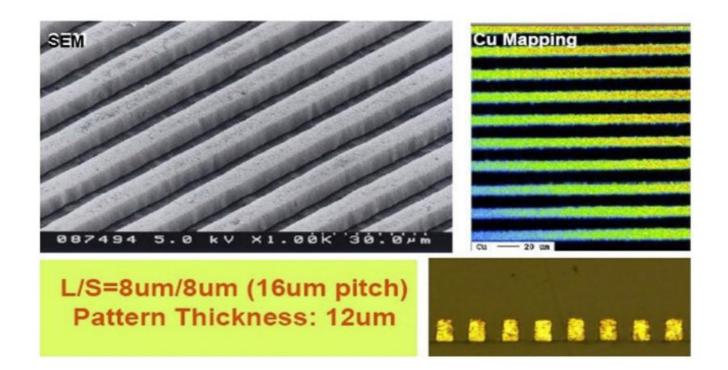

# Via Formation in HDI

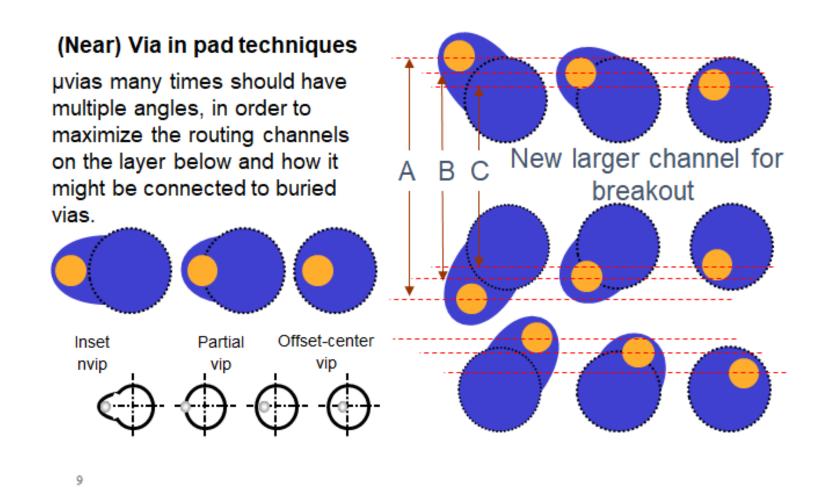

HDI PCBs will require interconnects that typically hit the lower limit of the via size that can be placed in a PCB with mechanical drilling. Once via holes get smaller than 6 mils, an alternative via formation process is needed to place microvias between layers. As filled plated microvias are a standard feature on HDI PCBs, they can be used in a via-in-pad design approach to help increase density. Using via-in-pad is an easy way to pack more components into a design as they provide a direct connection from a component lead into an internal layer.

Whenever there are reliability concerns regarding microvias, a near-pad technique can also be used, where a very small trace section comes off from a pad and touches the microvia. This completes the connection to an internal layer and provides a larger breakout channel should drill wander create some deviation from the desired drill hit location.

Learn more about laser-drilled via-in-pad technology

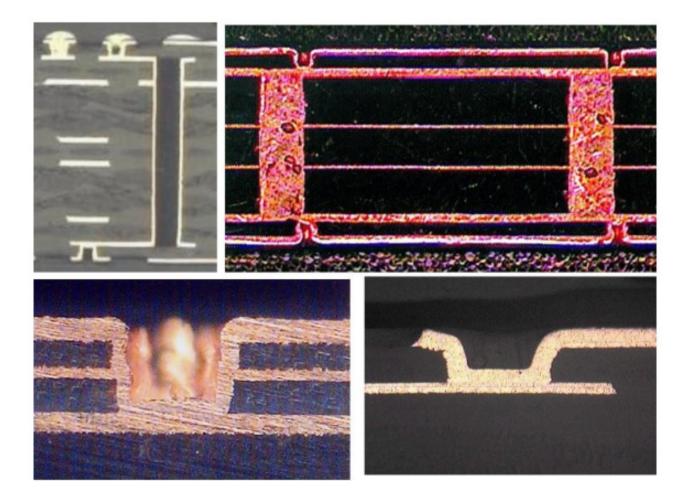

Via-in-pad design styles for HDI PCBs.

# **Metalization**

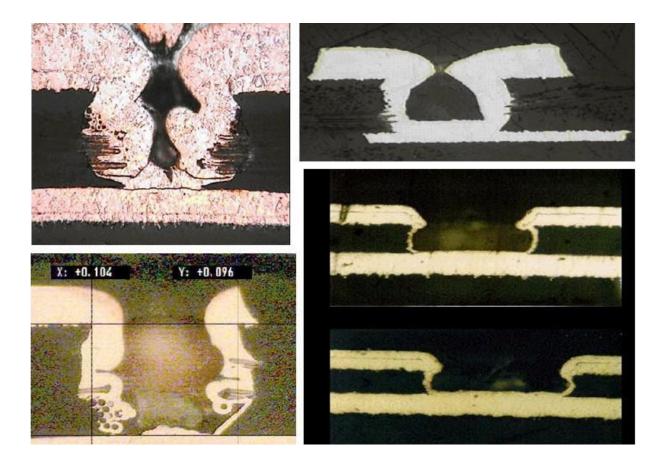

During the sequential lamination process, each layer in an HDI PCB will go a via metalization, fill, and plating process. The resulting vias must be void-free in the internal body with sufficient wrap plating around the neck so that cracking can be avoided during reflow cycles and during operation. There are four via metallization processes that are used in HDI manufacturing. These methods are:

- > Conventional electroless and electroplating copper

- > Conventional conductive graphite or other polymers

- > Fully and semi-additive electroless copper

- > Conductive pastes or inks

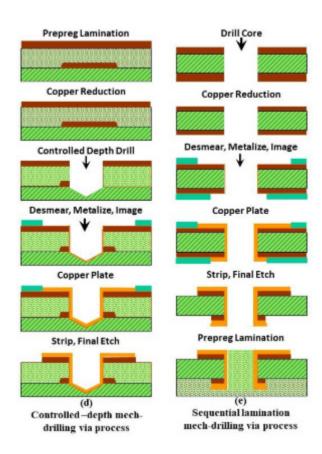

Larger vias can be drilled, but the costs eventually exceed laser drilling costs with lower throughput as a slower drilling speed is required. Laser drilling is by far the most popular microvia hole formation process, but it is not the fastest via formation process. The chemical etching of small vias is the fastest, with an estimated rate of 8,000 to 12,000 vias per second. This is also true of plasma via formation and photovia formation.

In laser drilling, a high fluence beam is used to place a hole in a PCB laminate. Lasers are capable of ablating dielectric material and stopping when intercepting the copper circuitry, so they are ideally suited for creation of depth-controlled blind vias. The wavelengths for laser energy are in the infrared and ultraviolet region. A beam spot size as small as approximately 20 microns

#### Learn more about microvia manufacturing techniques in the HDI manufacturing process

If the vias in the board are wide enough to drill, a controlled drilling step may be used to place vias. This requires an intermediate sequential lamination step to bond two layers of the board, followed by drilling and plating to define the via barrel, connection to the inner layer, and landing pad on the upper layer. These vias might also be filled before the next sequential lamination step (if they are on the inner layers), or they could be left un-filled if kept on the outer layers.The overall drilling and sequential process is shown below.

Learn more about HDI manufacturing processes on standard materials

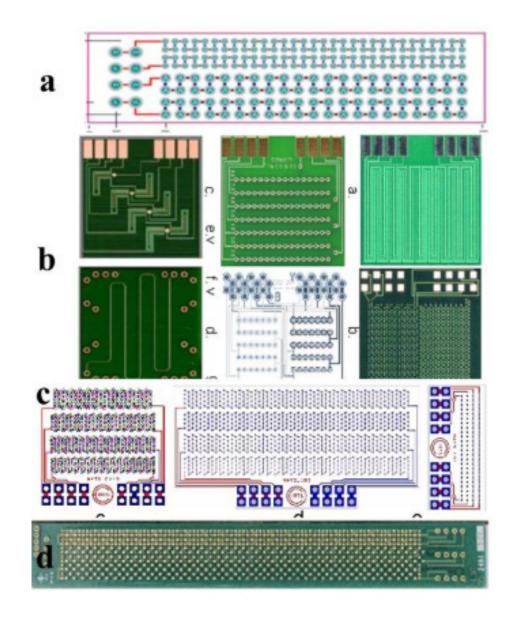

Microvia drilling and metalization processes in an HDI manufacturing process.

#### Getting Your Board into the HDI Manufacturing Process

HDI PCB processes are more advanced than traditional rigid PCB processing steps, but they still use the same set of fabrication data you use for a typical rigid PCB. Once you've finished your HDI PCB layout and it's passed a DFM review, it's time to prepare deliverables for your fabricator and assembler. The unified design environment in Altium Designer takes all your design data and uses it to create Gerbers/ODB++/IPC-2581 fabrication files, drill tables, a bill of materials, and assembly drawings for your new HDI PCB.

When you're looking for the best software package for HDI PCB design, layout, and manufacturing, use the complete set of design tools in Altium Designer®. The integrated design rules engine and Layer Stack Manager give you everything you need to create your bare HDI circuit board, calculate impedance values, and account for copper roughness in your PCB material system. When you've finished your design, and you want to release files to your manufacturer, the Altium 365<sup>™</sup> platform makes it easy to collaborate and share your projects.

#### **Defining Interconnect Density**

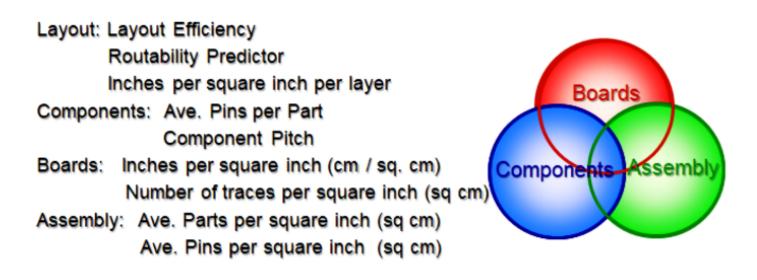

When planning an HDI design, there are measures of performance or metrics for the HDI process. Like the triangle in Figure 1, these three vital chains of the HDI Process are elements of interconnection density.

FIGURE 1. HDI Design Metrics

#### **Assembly Complexity**

Two measures of the difficulty to assemble surface mounted components, Component Density (Cd), measured in parts per square inch (or per square centimeter.) and Assembly Density, (Ad), in leads per square inch or per square centimeter.

#### **Component Packaging**

The degree of sophistication of components, Component Complexity, (Cc), measured by its average leads (I/Os) per part. A second metric is component lead pitch.

### **Printed Wiring Board Density**

The amount of density (or complexity) of a printed circuit, Wd, as measured by the average length of traces per square inch of that board, including all signal layers. The metric is inches per square inch. or cm per square centimeter. A second is the number of traces per linear inch or per linear cm. The PWB density was derived by assuming an average of three electrical nodes per net and that the component lead was a node of a net. The result was an equation that says the PWB density is times the square root of the parts per square inch times the average leads per part. ? is 2.5 for the high analog/discrete region, 3.0 for the analog/digital region and 3.5 for the digital/ASIC region:

PWB Density (Wd) = ? ffl [Cd] x [Cc]

= ? ffl [parts per sq. in.] x [ave.leads per part]

Where: p = Number of components (parts)

I = Number of leads for all the components

a = Area of the top surface of the board (square inches)

HDI PCB Design and Manufacturing Guide | 14

## **Packaging Technology Map**

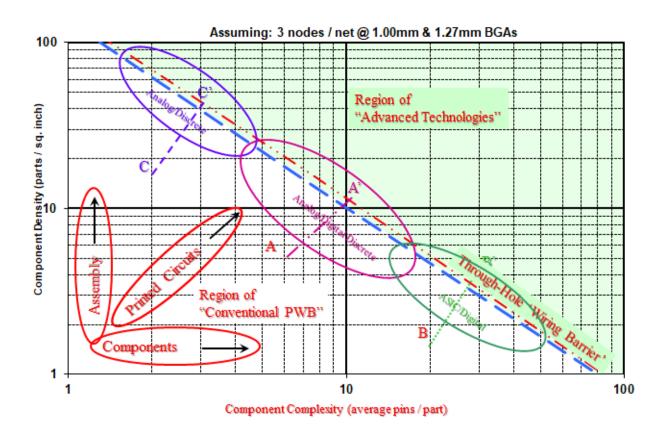

Figure 2 is what I call a Packaging Technology Map. The Packaging Technology Map was first displayed by Toshiba in January of 1991. [1].

A second valuable feature of the map is the area of upper-right. This is the "Region of Advanced Interconnections". This is where it is necessary to have an HDI Structure. The dashed lines indicate the barrier or wall of HDI! Cross this and it now becomes cost effective to use HDI. Move too far and it becomes a necessity.

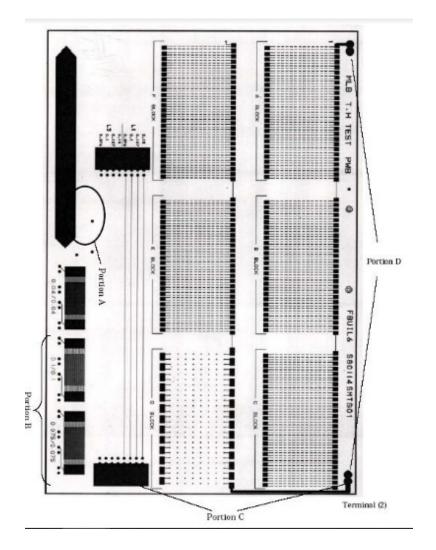

FIGURE 2. The through-hole (TH) wiring barrier as a function of a typical assembly

The packaging map is created by measuring an assembly size, number of components and the leads those components have. The components include both sides of an assembly as well as edge fingers or contacts. By the simple division of leads by parts and parts by area of the assembly, the X and Y-axis are known. Plotting the components per square inch (or components per square centimeter) against average leads per component on a log-log graph the PWB wiring density in inches per square inch (or centimeters per square centimeters) and Assembly Complexity (in leads per square inch or leads per square centimeter) can be calculated. The Assembly density is just the X-axis times the Y-axis.

# **Through-Hole Wiring Barrier**

When the chart (Fig. 2) is used to analyze surface mount assemblies, three major zones show up on the packaging chart, which is why I call it a Map. The first is products with a high content of analog devices and discrete components. Typical products are camcorders, pagers and cellular telephones (C-C'). They have the highest assembly complexity. Up to 300 to 400 leads per square inch (47 leads per square centimeter). The second group is products with a high degree of digital components and some mixed discretes. Notebook computers, desk tops, instruments, medical equipment and telecom routers are examples (A-A'). The last group has a highly integrated use of ICs. PCMCIA, flash memory, SiPs and other modules are typical of this group (B-B'). This group has the highest PWB wiring density of over 160 inches per square inch (25 centimeters per square centimeters). The Figure loosely shows the three regions.

When you look at the Figure, the Assembly Complexity lines cross the Wiring Density lines. At high discreet levels, less wiring is required for the amount of assembly density. At high ASIC (and low discreet) levels, much more wiring is required to connect the components. This makes assembly metrics like leads per square inch a good indicator, but not adequate to substitute for the PWB wiring density.

#### **The General Process of PCB Design**

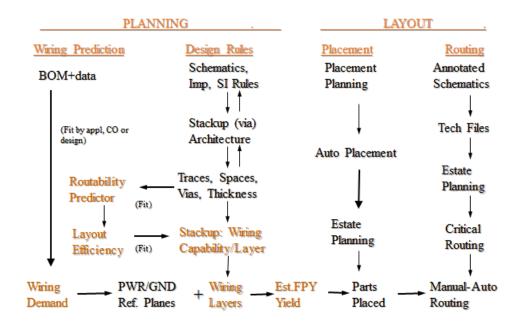

The process of PCB design utilizing HDI technology is shown in Figure 3. When designing with HDI technologies, the first step - [Plan Design] is the most important. Routing efficiencies for HDI is dependent on stackup, via architecture, parts placement, BGA fanout and design rules, as seen in Figure 4. But the entire HDI Value Delivery Chain must be taken into consideration, including fabrication yields, assembly considerations and in-circuit test. Working with your PWB fabricator and assembler is essential for a successful design.

| Plan Design                | Simulate High Speed Geometries | Create Area Fills     |

|----------------------------|--------------------------------|-----------------------|

| Input Schematic / Netlist  | Adjust Sequence & Placement    | Back Annotate Scemat  |

| Create Component List      | Test Routability               | Compare Netlist       |

| Create Component Libraries | Set-up Routing Rules           | Design Check          |

| Enter Mechanical Data      | Route Board                    | Create Test Points    |

| Set-up Placement Rules     | Check Routings                 | Generate M.F.G. Files |

| Place Components           | Add Planes for PWR & GND       | Audit Design          |

| S equence Nets             | Split Plane Generation?        | Archive Design        |

FIGURE 3. A general overview of the PCB design and layout process

#### HDI Standards, Guidelines, Specifications and References

When approaching HDI design, the place to start is with the IPC Guidelines and Standards. Four apply specifically to HDI design, as seen in Figure 5.

(➤) IPC/JPCA-2315: This is an overview of HDI and provides models for estimation design density. (>) IPC-2226: This specification educates users in microvia formation, selection of wiring density, selection of design rules, interconnecting structures, and material characterization. It is intended to provide standards for use in the design of printed circuit boards utilizing microvia technologies. [2] > IPC-4104: This standard identifies materials used for high-density interconnection structures. The IPC-4104 HDI Materials Specifications contain the slash sheets that define many of the thin materials used for HDI. The slash sheets of materials characteristics are divided into three main materials types: Dielectric Insulators (IN); Conductors (CD) and Conductor and Insulators (CI). (>) IPC6016: This document covers the performance and qualification for high-density structures.

# What's Different in HDI Design

Three (3) New Principles

There are three (3) new principles for HDI-microvia design that don't exist in TH design:

Microvias must replace TH vias, not just used "in addition to" TH vias.

- Oconsider new layer stackups that allow the elimination of TH vias.

- > Place microvias in such a way that they create channels and boulevards for improved routing. (see Table 1)

## **Microvias Replacing Through Holes (TH)**

The main idea is that microvias replace or allow the removal of TH vias, thus allowing the routing density on inner layers to improve by 2X or 3X, using the space the TH vias used to occupy. This will allow fewer signal layers and fewer reference layers for those signal layers.

This principal is more profound than it first appears. This is because there are three dimensions on how the microvias are placed, see Figure 6):

- Use of Microvias in Place of Through-Holes

- Layer Stackup Changes to Eliminate Drilled Holes

- Using the Blind Vias to Form Channels

- Placing the Blind Vias to Open Up Boulevards

TABLE 1. New principles for HDI design not used for TH multilayers

- The blind-vias can be "shifted or swung" in the X-Y or theta () angle to create more routing space

- > The blind-vias can be placed on inner layer (3D) to further create more breakout spaces

- > The center-to-center distance can be altered on inner layers to provide additional space for traces.

- If all of this is happening on or near the Primary Side, then there will be space created under the BGA on the Secondary Side for traces or more important, for discretes like decoupling capacitors.

FIGURE 6. Illustration of the benefits for routing by using blind vias

## **Layer Stackup Alternatives**

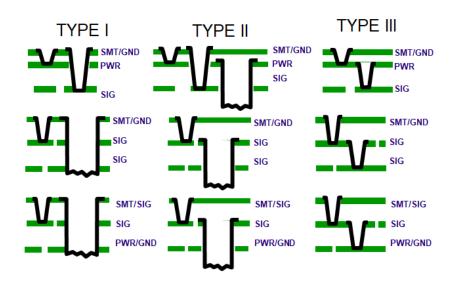

If you study the first Principle and ask yourself, "What jobs do my vias do?". The answer is that the most common via on a PWB are the vias to GND. "The second most common via?", the answer is obvious, it's the vias to PWR. Thus, moving the GND plane that usually is Layer-2 up to the surface provides the opportunity to eliminate all those vias to GND. In the same vein, moving the most used PWR plane up to Layer-2 will replace those THs with blind vias. These provide four (4) advantages over the conventional 'microstrip' stackup, as seen in Figure 7:

- There are no fine-lines to plate or etch on the surface.

- The surface can be an unbroken GND pour to reduce EMI and RFI (faraday cage)

- The closer Layer-2 (PWR) is to Layer-1 (GND) the more planar capacitance is available and the lower is the PDN planar inductance.

- The energy stored in the planar capacitance can be delivered to components with the lowest series inductance available, providing for the elimination of most of the decoupling capacitors.

Figure 7. shows some of the most common HDI stackups to reduce the number of TH vias. The three common HDI stackups are shown with the IPC-Type structures (I, II & III).

The possible dielectrics available between Layer-1 and Layer-2 can be conventional prepregs, laser-drillable prepregs, RCCs, reinforced RCCs or BC cores. These materials are described in Chapter 2 -HDI Materials. If the dielectric is thin, then it is practical to also utilize a 'skip-via' from Layer-1 to Layer-3, thus saving the cost of not having to utilize a IPC-Type III structure. Even if a thin dielectric is not employed, any dielectric thickness less than 0.005 inch (<0.125mm) will couple GND to PWR and provide a lower power supply (PS) impedance, as well as reducing PS resonances and noise.

FIGURE 7. Three alternative surface layer stackups compared to IPC-Type I, II & III structures

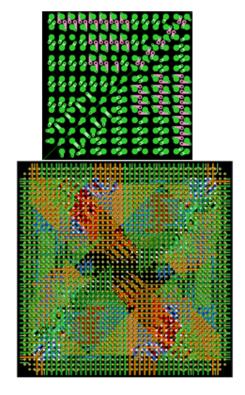

# Placing blind vias to open larger boulevards

One useful HDI design technique is to use blind vias to open up more routing space on the inner layer. By using blind vias between the through-vias, the routing space effectively doubles on the inner layers,

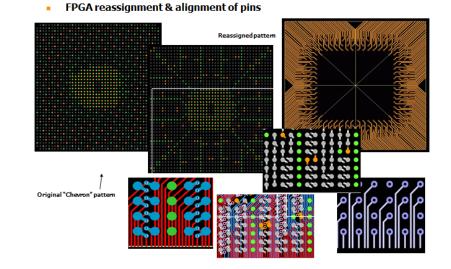

FIGURE 8. Near-via-in-Pad definition and swinging the ViP to create channels for routing

allowing for more traces to connect pins on the inner rows of a BGA. As seen in Figure 6, for this 1.0 mm BGA, only two traces can escape between vias on the surface. But beneath the blind vias, now six traces can escape, increasing the routing by 30%. With this technique, one fourth the number of signal layers is required to connect a complex, high-I/O BGA. Blind vias are arranged to form boulevards either in a cross, L-shaped or diagonal formation. Which formation to use is driven by the power and ground pin assignment. This is why, for a FPGA, reprogramming the placement of power and ground pins can be so productive.

FIGURE 9. Blind vias can be used to form boulevards in inner layers allowing 30% more routing out of the BGA

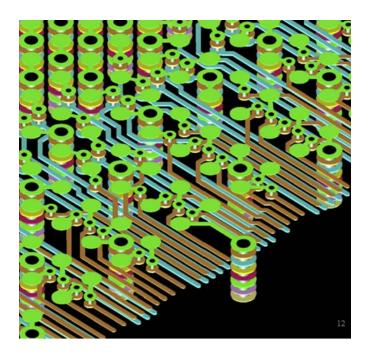

The microvia used for BGA fanout was shown in Figure 9. The microvia can be placed outside the BGA land (inset), partially in/out of the land (partial vip) or completely in 'the pad' (vip)-see Figure 10.. If placing the via-in-pad, then the via should always be 'off-center' and not placed in the direct center of the land. This is to minimize any trapped air 'voids' during soldering. If the via is placed in the center of the BGA land, and it is not-filled, when the solder paste is applied on the land, and the BGA placed on the paste-land, during reflow, as the solder melts, the BGA ball drops and traps any air that may be there, much like a 'cork in a bottle'. By placing the via 'off-center', the air has a chance to escape as the solder melts and flows into the microvia.

- Escape from complex BGA packages

- Via structure

- Stacked, adjacent

- Combo with vias through laminate

FIGURE 10. blind-via alternatives

FIGURE 11. Fancy 3D view of 'swing-vias' connecting to buried-vias and through-holes

#### **Introduction to High Density Interconnects**

This article outlines the advanced design approaches and manufacturing processes needed to design the most complex of these PWBs, the high-density interconnects (HDI).

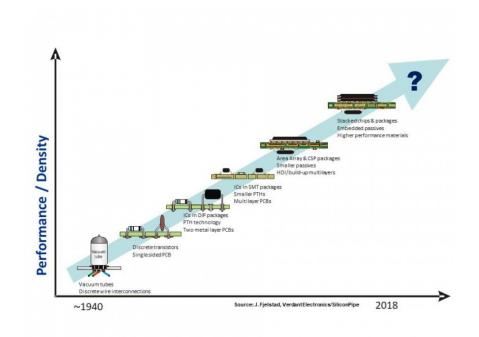

#### The Evolution of Electronics

Electronics is a relatively new industry since it has been only 65 years since the transistor was invented. The radio tube was developed nearly 100 years ago but blossomed in WWII, with communications, radar, ammunition fusing (especially the radar-altimeter electronic fusing for the first atom bomb) and has evolved into the world's largest industry. All electronic components must be interconnected and assembled to form a functioning unit. Electronics packaging is the technology where we integrate the design and manufacturing of these interconnections. Since the early 1940s, the basic building platform of electronic packaging is the printed circuit board (PCB). This Guidebook outlines the advanced design approaches and manufacturing processes needed to design the most complex of these PWBs, the high-density interconnects (HDI), as illustrated in Figure 1.

This chapter introduces the basic considerations, the main advantages, and the potential obstacles that must be accounted for in the selection of the high-density interconnection methods. Its main emphasis is on the interconnections and wiring of components. The focus is on density and the potential effects that the selection of various HDI board types and design alternatives could have on the cost and performance of the complete electronic assembly.

As printed circuits became more commonplace since the early 50s, the density and complexity of interconnects have increased quickly, but not as much as the last ten years. Conventional printed circuit technology is capable of meeting most of today's requirements. Yet, there is a growing group of products referred to as "High Density Interconnects" (HDI for short) that are used to create still denser interconnect, and it is these that are the subject of this Guidebook.

# **Interconnect Trends**

Drivers for higher-density interconnection come under three headings; platforms, performance, and parts:

#### Platforms

With fast-growing markets for products such as mobile phones, digital appliances, and wearable computers, all of which represent new opportunities. HDI makes possible electronics becoming smaller and lighter.

#### Performance

With decreased semiconductor rise-times, and more RF and microwave communications, at frequencies up to 80 GHz in some telecom's areas.

#### Parts

The evolving silicon technology of smaller transistors and its faster rise-times leads to the challenge to provide more leads in a smaller footprint, which equates to more connections per unit area.

All these trends create a demand for denser interconnects, with smaller trace and gap dimensions, smaller vias, and more buried vias. While this is not necessarily accompanied by a change in board design practices, conventional constructions can reach their limits and the design of HDI constructions require rethinking of design strategies.

FIGURE 1. Electronics have evolved in density from the 1940s to the current state of high-density interconnects that include 3D stacking and embedded components.

#### **HDI Multilayer Platforms**

HDI is such a large and growing PWB application market, that there are at least three (3) different HDI Platforms that make it up. These four platforms are 1. Substrates & Interposers modules; 2. Portables; and 3. High performance.

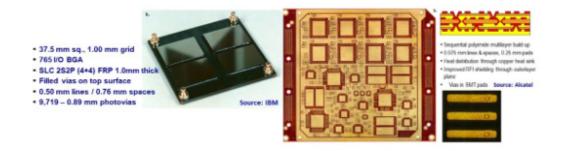

#### **Substrates & Interposers Modules**

This technology is used for flip chip or wire bondable substrates. Microvias allow the increased density needed to escape from the high-density flip chips. The dielectric materials are the newer engineered films. A typical example is seen in Figure 2. The modules are small substrates that may have their ICs wire bonded, flip-chipped or TAB mounted or may use fine-pitch CSPs. The discrete components are typically very small, like 0201 or 01005s, and may even be embedded. The design rules are usually coarser than the single IC substrate, since the module may be larger than a single IC package.

#### **Portables**

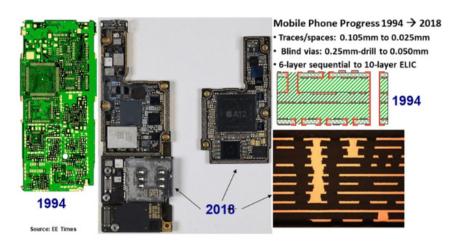

Portables and miniaturized consumer products are the leading edge in HDI Technology. The dense designs offer small form factors and very dense features including micro-BGA and flip chip footprints. The largest application is currently mobile phones. A typical mobile phone product (Motorola MicroTack and the Apple iPhoneX) is seen in Figures 3.

# **High performance**

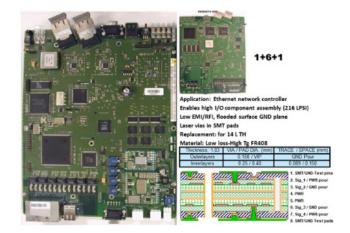

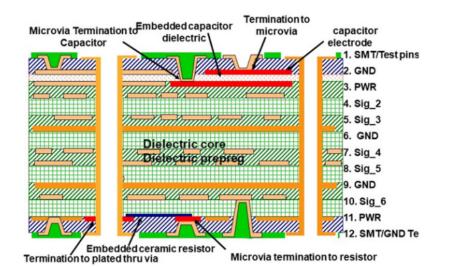

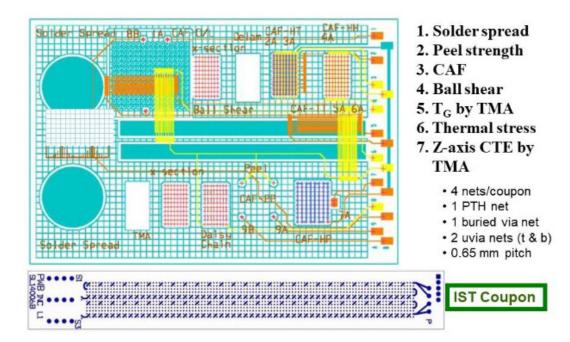

This technology is used for high layer count boards with high I/O or small pitch components. A buried via board is not always necessary. The microvias are used to form the escape area of dense components (high I/O, micro BGA). Dielectric is reinforces-resin coated foil, reinforced prepregs and cores and high-performance laminates. A typical example is seen in Figure 4. A possible 4th platform to be developed is 'embedded components' seen in Figure 5.

FIGURE 2. High-density modules for a. Flip chip substrates and b. Telecom

FIGURE 3. Ever increasing complexity and density characterize the HDI boards used in mobile phones from 1994 through the present day.

FIGURE 4. A high reliability telecom board for a triple OC-192 (10 Gb/s) optical network controller. Construction is of low-loss laminates and uses a 1+6+1 HDI structure.

FIGURE 5. The typical usage of microvias to connect various embedded capacitors and Resistors

#### **Performance Improvements**

When performance improvements are required for PWBs, HDI is the leading contributor. In addition to making the PWB smaller, lighter, and thinner, it will have superior electrical performance. Some of these improvements are:

- Order of magnitude lower via electrical parasitic

- Ninimal stubs

- Stable voltage rail

- Removal of decoupling capacitors

- > Lower crosstalk and noise

- Much lower RFI / EMI

- Closer ground planes

- Opportunities for distributed capacitance (PWR/GND)

- Surface ground planes w/via-in-pads cut emissions and radiation

As semiconductor fabs reduce the size of their devices, the physics allows faster rise / fall times. This manifests itself in higher-frequency performance. But with smaller devices comes many more on a chip and higher heat dissipation. With a reduction in power supply voltage to minimize the power dissipation, what results is to increase the sensitivity of circuits to various forms of noise and loss of signal strength. High-performance laminates have always been one of the requirements. Additionally, improved processes for microvias fabrication also improve high-frequency performance.

Microvias have nearly 1/10 the parasitics of THs. Test Vehicle structures can validate the lower inductance in microvias, and when combined with low-inductance decoupling capacitors, and via-in-pads, show the merits of noise reduction, especially for high-speed logic.

HDI PCB Design and Manufacturing Guide | 26

## Access to Advanced Components (parts)

The semiconductor industry is the primary driver for electronics. Smaller gate geometries and greater total gates allow more functions to be performed – and faster. With larger wafers, the prices continue to tumble.

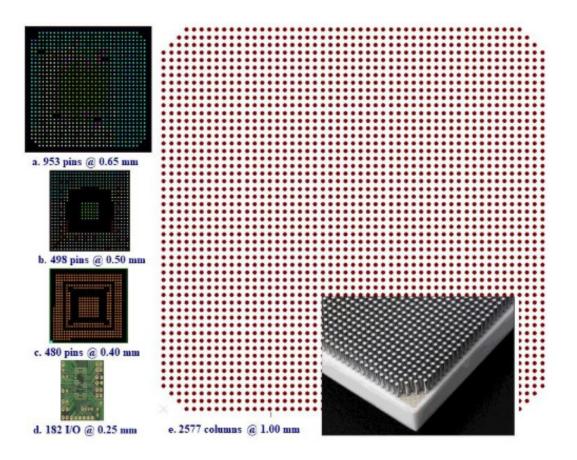

IC packaging, say a 0.80- and 0.65-mm. pitch device, benefit from PCB technologies like HDI, but the use of 0.8 mm pitch and smaller devices is where HDI really begins to provide advantages. The blind vias save room on inner layers and have reduced via lands, as well as making possible via-in-pads. Typical of these devices is the 953 pins, 0.65mm pitch, Digital Signal Processor (DSP) seen in Figure 6a or the 498 pins DSP shown in Figure 6b. The other new components becoming more widespread are ones with very high pin counts of around 600 to 2500 pins, even at 1.00- and 0.8-mm pitches. Although some of these are telecom digital switches (Figure 6c), the vast majority are the new field programmable gate arrays (FPGAs). Current products from Actel, Infineon, Xilinx and Altera have packages with 456, 564, 692, 804, 860, 996, 1020, 1164, 1296, 1303, 1417, 1508, 1696 and 1764 pins. FPGAs of greater than 2000 pins are being designed!

FIGURE 6. a. Fine-pitch devices such as these 953 pins - 0.65 mm pitch microprocessor, b. the 498 pin 0.5mm DSP device or c. the 480 pin @ 0.4 mm controller, even the d. 182 pins @ 0.25 mm require microvias. e. The 2577 pin - 1.0 mm pitch digital switch now require microvias in order to connect them on a printed circuit.

# The HDI Opportunities

Other benefits of using HDI technologies can come from the ease of design resulting in Faster Time-to-Market and its Improved Reliability.

#### **Faster Time-to-Market**

The faster time-to-market comes about because of easier placement of components using blind vias or via-in-pads. Other design efficiencies come about because

of smaller spacing, improved BGA breakouts, boulevards routing (see Chapter 4), and ease of auto-routing using blind/buried vias over through-hole vias. The overall system design times can be reduced because of the improved electrical performance of blind vias instead of TH vias, fewer respins will be required because of signal integrity and noise reduction.

# **Improved Reliability**

Extensive reliability testing was performed by the IPC-ITRI in the late 1990s about the reliability of microvias. [1] Other groups (like HDPUG & NASA-JPL) have also produced reports on the superior reliability of small-blind vias over TH vias. [2] Understanding 'WHY' is quite simple! The via aspect ratio (AR-depth to diameter ratio) is less than (6:1 (+) that go as high as 20:1. This is a result of the thin materials and low Z-Axis TCE materials used in HDI (see Chapter 2). HDI materials are numerous and exceed multilayer laminate in variety, thus they are covered by the IPC Standard IPC-4104A and not IPC-4101B. If the blind vias are properly drilled and plated, then they will perform with many times the thermal cycle like typical THs (see Chapter 6)

The thin HDI materials are thus well suited for thermal heat transfer and this is also covered in the IPC HDI Design Standards, IPC-2226.

#### **Lower Cost**

Chapters 4 and 5 will discuss in detail, the improved design process for HDI PWBs. Properly planned and executed, an HDI multilayer can be less expensive than the TH board alternative. As illustrated in Figure 4, the Benchmark of a high-speed, controlled impedance 14-layer TH multilayer to an 8-layer HDI multilayer. By fully utilizing the Secondary Side of the PWB, 40% less area was required to connect all the components, in addition to 6 fewer layers.

# Predictability or "What Will It Cost?" and the Need For Design Models

#### Predictability

Customers need to know the HDI stackup, design rules, and PRICE, BEFORE starting the project or board design.

Fabricators can quote the design AFTER it is designed, but without the numbers up front - no one can afford the time to run down a blind alley. The concept that "Microvias cost more!" is one of not knowing how to properly design an HDI board.

One of the benefits of Benchmarking HDI for the last 37 years, was the TH versus HDI Trade-Off chart seen in Figure 7. The Price / Density Comparison. The two key variables are RCI, a comparison currency, normalized to the actual price of an 8-layer multilayer and DEN, the average number of pins on a board divided by the length and width of the board.

|        |                     | A B C  |        |       |           |                | E         | -              | F     |                       | 3         |         |                      |      |

|--------|---------------------|--------|--------|-------|-----------|----------------|-----------|----------------|-------|-----------------------|-----------|---------|----------------------|------|

| N      | THRU-HOLE HDI BLIND |        |        | HDIE  | BL/BU     | 1BU 8          | BLIND     | 2BU 8          | BLIND | 2BU                   | BL.BU     | 2BU 8   | BL.BU                |      |

| Layers |                     | N      | 1+N+1  |       | 1+bN+1    |                | 1+N+1     |                | 2+N+2 |                       | 2+bN+2    |         | 2+bN+2               |      |

| Layers |                     | d via* | -      | L1-L2 |           | L1-L2          |           |                |       | staggered L1-L2, L2-L |           | a L1-L3 | staggered L1-L2, L2- |      |

|        | buried via          |        | none   |       | L2-L(N-1) |                | L2-L(N-1) |                | no    | ne                    | L2-L(N-1) |         | L3-L(N-2)            |      |

|        |                     |        | V      |       |           |                |           |                |       |                       | Ĩ         |         |                      |      |

|        | RCI                 | DEN    | RCI    | DEN   | RCI       | DEN            | RCI       | DEN            | RCI   | DEN                   | RCI       | DEN     | RCI                  | DEN  |

| 4L     | 0.62                | 20     | . 0.83 | 40    | 1.05      | 80             | 1.26      | 135            | 1.38  | 135                   |           |         |                      |      |

| 6L     | 0.78                | 20 /   | . 0.99 | 60    | 1.24      | 160            | 1.46      | 200            | 1.60  | 200                   | 1.74      | 260     | 1.91                 | 280  |

| 8L     | 1.00                | 30     | 1.21   | 120   | 1.49      | 180            | 1.74      | 240            | 1.90  | 240                   | 2.06      | 300     | 2.25                 | 320  |

| 10L    | 1.30                | 40     | 1.51   | -200  | 1.83      | 210            | 2.11      | 260            | 2.30  | 260                   | 2.50      | 400     | 2.73                 | 440  |

| 12L    | 1.70                | 60 /   | 1.92   | 210   | 2.31      | 230            | 2,62      | 300            | 2.85  | 300                   | 3.10      | 600     | 3.37                 | 650  |

| 14L    | 2.24                | 70     | 2.48   | 220   | 2.95      | 250            | 3.32      | .360           | 3.61  | 360                   | 3.91      | 800     | 4.25                 | 860  |

| 16L    | 2.97                | 80     | 3.22   | 260   | 3.81      | 300            | 4.25      | 420            | 4.61  | 420                   | 5.00      | 1000    | 5.43                 | 1100 |

| 18L    | 3.92                | 100    | 4.21   | 300   | 4.95      | 400            | 5.47      | 480            | 5.93  | 480                   | 6.42      | 1250    | 6.96                 | 1350 |

| 20L    | 5.14                | 105    | 5.48   | 360   | 6.41      | 500            | 7.04      |                | 7.62  |                       | 8.23      |         | 8.90                 |      |

| 22L    | 6.67                | 110    | 7.08   | 400   | 8.23      | 600            | 8.99      | and the second | 9.70  |                       | 10.45     |         | 11.27                |      |

| 24L    | 8.53                | 125    | 9.03   | 460   | 10.41     | 700            | 11.32     | and the second | 12.17 |                       | 13.07     |         | 14.04                |      |

| 26L    | 10.68               | 130    | 11.30  | 500   | 12.92     | and the second | 13,96     |                | 14.96 |                       | 16.00     |         | 17.11                |      |

| 28L    | 13.09               | 135    | 13.83  | - 540 | 15.65     | 1              | 16.82     |                | 17.93 |                       | 19.09     |         | 20.32                |      |

| 30L    | 15.63               | 140    | 16.50  | 580   | 18.47     | and a second   | 19.73     |                | 20.94 |                       | 22.18     |         | 23.48                |      |

| 32L    | 18.17               | 145    | 19.17  | 620   | 21.21     |                | 22.53     |                | 23.79 |                       |           |         |                      |      |

| 34L    | 20.59               | 150    | 21.69  | 660   | 23.73     |                | 25.09     |                |       |                       |           |         |                      |      |

| 36L    | 22.79               | 160    | 23.9.6 | 700   | 25.94     |                |           |                |       |                       |           |         |                      |      |

| 38L    | 24.68               | 180    | 25.91  | 740   |           |                |           |                |       |                       |           |         |                      |      |

| 40L    | 26.26               | 200    |        |       |           |                |           |                |       |                       |           |         |                      |      |

FIGURE 7. TH versus HDI Price / Density Comparison. The Relative Cost Index (RCI) and DENsity predictor (pins/sq. inch) provides a quick comparison of TH layers (column A) to equivalent HDI structures (columns B - G).

The RCIs in the matrix is the 'Basis' numbers (or minimums) for costs. But the 'Ceiling' number for a range is out of our ability to calculate or set up at this time. It all depends on the various factors in the design. Yields are very sensitive to min. diameter, annular rings, min. trace and spacing, material thicknesses, total number of holes and their density. Other cost factors such as final finish, hole filling, and tolerances will affect the price. I have added a column for "Density" (DEN). This is the Maximum Number of Electrical Connections (called 'pins') per square inch of surface (for both sides). The dashed lines are "Equivalent" PCBs. So, as an example, an 18-Layer TH (through-hole-column A) board with an average of 100 'pins' per sq. in could have been designed as a 10-layer HDI board (1+8+1-column C) because it can handle 210 'pins' per sq. in (p/si). Or, it could have been designed as a 6-layer HDI board with 2+2+2 (column E, also 200 p/si).

The RCI does not show the "Absolute" cost savings in this example. The "Relative" cost saving is 28.1% for the 10-layer and 20.5% for the 6-layer HDI 'equivalents'. But a smaller board could result in more boards per panel and the 'PRICE" would be even lower than the above numbers. In the range of 8L to 18L, the HDI boards, especially the 2+N+2 are NOT the equivalent of 8L to 18L TH boards, they represent boards with 12X- 20X the density of TH boards.

This Matrix is based on FR-4. This has two important implications. The TH RCI scale (from 4L – 16L) represents competitive pricing set by China. This scale is depressed compared to the HDI pricing. So the HDI pricing, if equal or lower, is very competitive. If the material of construction is NOT FR-4, but a more expensive, low Dk or low Dj material, then the savings from HDI will be MUCH LARGER as you reduce layers!

### **11 HDI Materials You Need to Know**

In this article we will discuss the materials used to manufacture HDI circuits. Several good resources exist on the subject of materials for PCBs (such as the Printed Circuit Handbook edited by Holden & Coombs) so we will concentrate on those materials that are specific to HDI.

#### **Materials for HDI**

The current HDI materials market worldwide was estimated by BPA Consulting Ltd. to be 83 million square meters. The breakdown by BPA Consulting of the eleven (11) HDI materials used, in order of usage:

- Laser-Drillable Prepregs-40.4%

- **RCC-28.3%**

- Conventional Prepregs-17.2%

- ABFilm-5.0%

- Epoxy-3.3%

- > Other-3.2%

- 🗩 BT-1.8%

- > Aramid-0.4%

- Polyimide-0.3%

- > Photo Dry film-0.1%

- 🕥 Photo Liquid-~0.0%

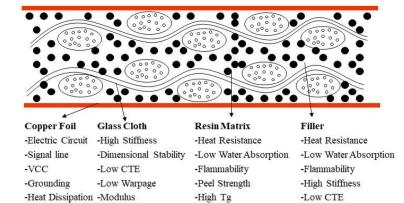

The major material components of PCBs are the polymer resin (dielectric) with or without fillers, reinforcement, and metal foil. A typical construction is shown in Figure 1. To form a PCB, alternate layers of dielectric, with or without reinforcement, are stacked in between the metal foil layers.

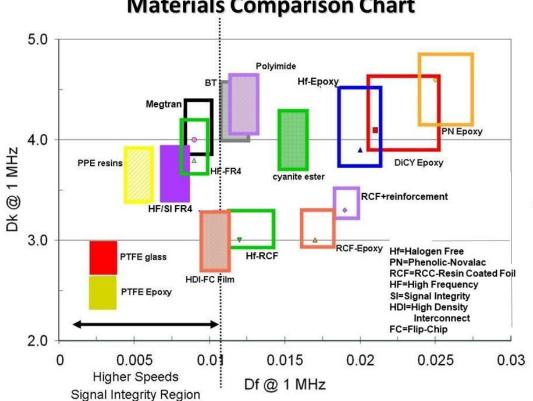

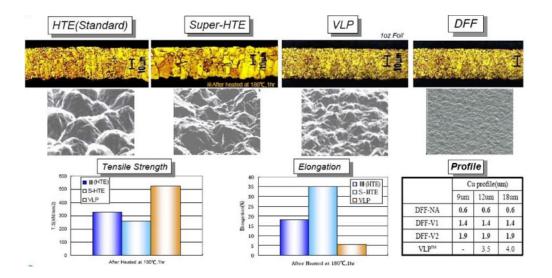

The majority of the materials are epoxy, but some are BT, PPE, cyanate ester, and modified acrylates. The newest materials are the growing number of laser-drillable prepregs.

-Toughness

-Dielectric Properties

FIGURE 1. Construction of a PWB laminate [Source: PC Handbook,7th Ed]

-Dimensional Stability

-Low Warpage

-Modulus -Heat Dissipation

### **Dielectrics and Insulators**

The backbone resin of the industry has been the epoxy resin. Epoxy has been a staple due to its relatively low cost, excellent adhesion (both to the metal foils and to itself), and good thermal, mechanical, and electrical properties. As demands for better electrical performance, ability to withstand lead-free solder temperatures (see Table 1), and environmental compliance have entered the picture, the basic epoxy chemistry has been dramatically changed over the years.

Epoxies are thermosetting resins and use hardeners and catalysts to facilitate the cross-linking reactions that lead to the final cured product. Epoxies are also inherently flammable, so flame retardants are incorporated into the resin to greatly reduce the flammability. Traditionally, the main curing agent was Dicy, but now various phenolic compounds are used. The traditional bromine compounds (i.e., TBBA) used as flame retardants are being substituted with other compounds such as those containing phosphorous because of concerns about bromine getting into the environment when the PCBs are disposed of. Many companies have gone to a "Halogen-Free" requirement in anticipation of an eventual ban or for the appearance of being "green."

- Tg Glass Transition Temperature

- Td Thermal Decomposition Temperature

- "Time to Delamination", T-260°C and T-288°C

- CTE Coefficient Thermal Expansion Z Axis

- STII Solder Temperature Impact Index

TABLE 1. The four important thermal characteristics of a 'lead-Free' laminate and STII.

| A COLORED AND A COLORED |          |                      |                     |               | 1772313 |

|-------------------------|----------|----------------------|---------------------|---------------|---------|

| Vendor                  | Grade    | T <sub>g</sub> (TMA) | T <sub>d</sub> (5%) | TE (50-260°C) | STII    |

| ELITE                   | EM-827   | <b>17</b> 5°C        | 355°C               | 2.6%          | 238     |

| ISOLA                   | IS400    | 135°C                | 330°C               | 3.0%          | 202     |

| ISOLA                   | FR250HR  | 140°C                | 350°C               | 3.4%          | 211     |

| TUC                     | TU-662   | 145°C                | 340°C               | 3.4%          | 211     |

| NELCO                   | N4000-7  | 150 °C               | 340°C               | 3.4%          | 203     |

| TUC                     | TU-752   | 170°C                | 350°C               | 2.7%          | 233     |

| NELCO                   | N4000-11 | 170°C                | 345°C               | 3.2%          | 225     |

| ISOLA                   | IS410    | 170°C                | 350°C               | 3.5%          | 225     |

| TUC                     | TU-722   | 172°C                | 330°C               | 3.0%          | 260     |

| NANYA                   | NPC-175F | 175 °C               | 361°C               | 3.1%          | 233     |

| ISOLA                   | IS500    | 170°C                | 400°C               | 2.8%          | 257     |

| TUC                     | TU-842   | 170°C                | 390°C               | 2.1%          | 259     |

| NANYA                   | NPC-180  | 180°C                | 370°C               | 3.6%          | 240     |

| ISOLA                   | 370HR    | 170°C                | 350°C               | 2.7%          | 233     |

| NELCO                   | N4000-12 | 180°C                | 370°C               | 3.6%          | 239     |

| NELCO                   | N4000-13 | 200°C                | 365°C               | 3.5%          | 247     |

#### STII-Values for Some Laminate Materials

#### STII =(T<sub>g</sub>+ T<sub>d</sub>)/2 - [% thermal expansion 50 to 260°C] x10 Soldering Temperature Impact Index (STII ≥ 215)

#### FIGURE 2. Some STII values of common laminates.

Other resins that are in common use are typically selected to address specific shortcomings of epoxy-resin systems. BT-Epoxy is common for organic chip packages due to its thermal stability, while polyimide and cyanate ester resins are used for better electrical properties (lower Dk and Df) as well as improved thermal stability. Sometimes they will be blended with epoxy to keep costs down and improve mechanical properties. An important thermal property for lead-free assembly is the STII and some laminates values are seen in Figure 2.

Besides thermosetting resins, thermoplastic resins are utilized including polyimide and polytetrafluoroethylene (PTFE). Unlike the thermoplastic version of polyimide which is relatively brittle, the thermosetting version is flexible and is supplied in film form. It is typically used to make flexible circuits as well as the combination circuits called rigid-flex. It is also more expensive than epoxy and is only used as needed.