# Altium

## **Design for Manufacturing**

nananana v

### David Marrakchi

Senior Technical Marketing Engineer

### **Design for Manufacturing**

A Practical Guide for "Right the First Time" PCB Design and Manufacturing

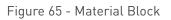

## **Table of Contents**

| Introduction |

|--------------|

|--------------|

#### Design Guidelines for Successful Manufacturing

| <b>Chapter 1</b> - A Day in the Life of a PCB Manufacturing Process | 6  |

|---------------------------------------------------------------------|----|

| Chapter 2 - Selecting Your Materials                                | 13 |

| Chapter 3 - Strategizing Your PCB Layout                            | 22 |

| Chapter 4 - Placing and Orienting Your Components                   | 51 |

| Chapter 5 - Configuring Your Test Point Requirements                | 64 |

## Documentation Guidelines for Successful Fabrication and Assembly

| Chapter 6 - Documenting Your PCB For Fabrication | 76  |

|--------------------------------------------------|-----|

| Chapter 7 - Documenting Your Master Drawing      |     |

| Chapter 8 - Documenting Your PCB for Assembly    | 103 |

| Chapter 9 - Preparing Your Manufacturing Files   | 108 |

|                                                  |     |

| Conclusion                                       |     |

Glossary 129 Appendix 140

#### The Age of Information

I've been in the electronics industry for more than 17 years, and have made a ton of mistakes along the way. But in this digital age that we all live in, information is only a search away, and the design problems that used to plague electrical engineers in the past have largely been ironed out by someone, somewhere. Never before in PCB design has information been so readily available, and problems documented so thoroughly. How does this affect you as an electronics designer? There is no need to continue re-inventing the wheel and making the same cycle of mistakes as our predecessors did in years past.

Whether I talk to seasoned electrical engineers or those fresh out of university, I'm always asked the same question - how do I design better? We are all dealing with the complexities of denser boards, higher clock rates, and smaller mechanical enclosures, and designing for those requirements alone can be a challenge. However, your designs exist beyond the digital domain, and to successfully produce a manufacturable board there are a number of additional guidelines to carefully consider throughout your entire design process.

The reality is, the process of designing better doesn't end the minute you ship off your documentation to manufacturing, it ends when you get your board back in its physical form and it works as intended. This goal can be a challenge for most PCB designers, who commonly have to deal with a myriad of unique requirements that each manufacturer sets forth, only to get lost in the details as design projects run off their intended course.

Here's the good news - there's a way to design your PCB not just for the digital domain, but for the manufacturing world as well. And when you design it correctly, you will start seeing your boards get back right the first time.

You can think of this guidebook as an accumulation of knowledge that has been set down from those before you. The collective years of experience in the electronics industry have allowed us at Altium to soak up knowledge from PCB designers all around the world, and this knowledge we now pass on to you.

Would you like more information? Watch our webinar on DFM Tips and Tricks.

Jul

Samuel P. Sattel, Director of Technical Marketing

#### What is Design for Manufacturing?

The goal for this guidebook is simple - get a good board back, every time. And the applied methodology for doing this is Design for Manufacturing (DFM). You might have heard of DFM in the past, but what exactly does it mean?

Design for Manufacturing (DFM) is the process of designing a PCB that is both manufacturable, functional, and reliable.

With this definition in mind, we have several clear goals to reach by adopting the design practices within this guidebook:

- 1. Eliminate the need for multiple board respins due to manufacturing-specific details that were missed in a design process.

- 2. Design and produce boards that are both manufacturable and function as intended by following a set of best practices set forth by PCB design veterans.

- **3.** Reduce the time spent on design revisions and ultimately meet time to market goals consistently by following a set of best practices for board layout and documentation

To meet these goals, we've structured this guidebook to ideally be read from start to finish to match up with your design workflow. As you read each section in the following chapters you will be able to apply the knowledge to each stage of your PCB design process.

#### What You Will Find in This Guidebook

This guidebook is both theoretical and practical, and applies trusted and accepted design science that has resulted in consistently manufacturable boards. The major sections in this guidebook includes:

#### Section 1: Design Guidelines for Successful Manufacturing

In this section we will be covering design practices that will produce both a functional and manufacturable board layout. This section will include:

• **Chapter 1:** Understanding the typical PCB manufacturing process and its various stages.

- **Chapter 2:** Selecting the right materials for your PCB to meet your specific design requirements.

- **Chapter 3:** Strategizing your PCB layout including via/hole placement, soldermask layers, and silkscreen documentation.

- **Chapter 4:** Placing and orienting your components to ensure proper spacing and assembly.

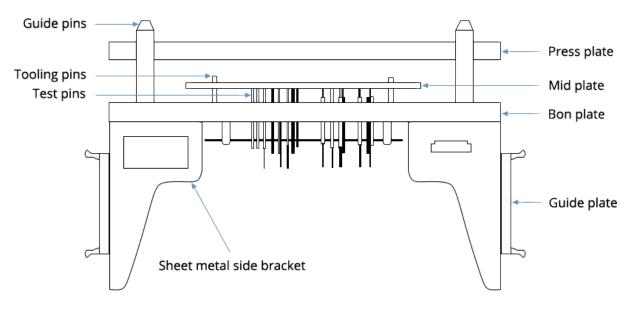

- **Chapter 5:** Configuring test point requirements for successful board testing by your manufacturer.

#### Section 2: Documentation Guidelines for Successful Fabrication and Assembly

With your design complete and ready for manufacturing, we will then be moving on to properly documenting a PCB to provide crystal-clear design intent to your manufacturer. This section will include:

- **Chapter 6:** Understanding what the main factors are in the PCB documentation process and what needs to be sent to your manufacturer.

- **Chapter 7:** Assembling the master drawing of your PCB to accurately portray all of the fine details needed to manufacture a board.

- **Chapter 8:** Understanding what you need to include in your assembly documentation to have your bare board created with your selected components.

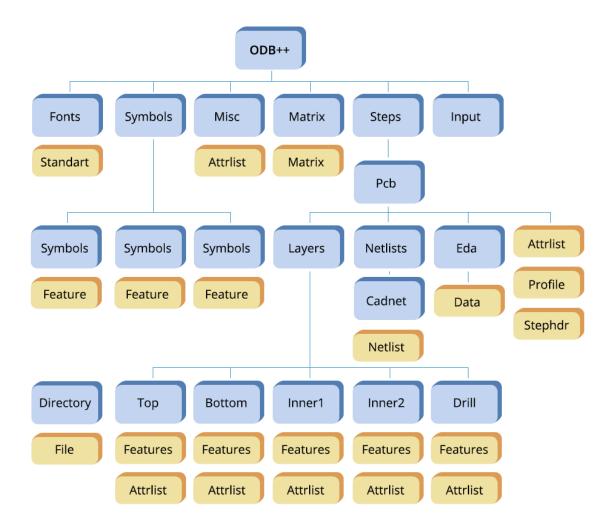

- **Chapter 9:** Understanding why manufacturing files matter and what specific files to send to your manufacturer including Gerbers, ODB++, IPC-2581 and Bill of Materials.

By the end of this guidebook you will be well equipped to implement the design and documentation practices into your own personal workflow to produce manufacturable-ready PCBs.

## Design Guidelines for Successful Manufacturing

#### A Day in the Life of a PCB Manufacturing Process

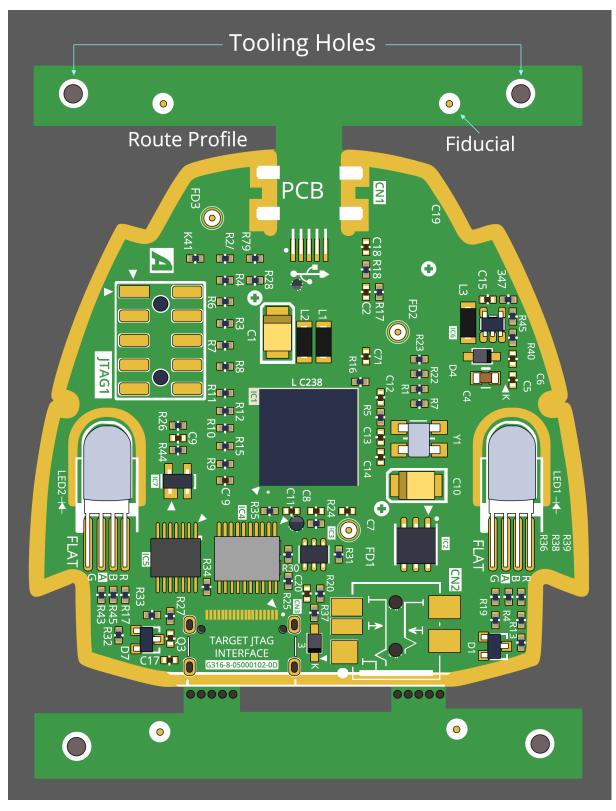

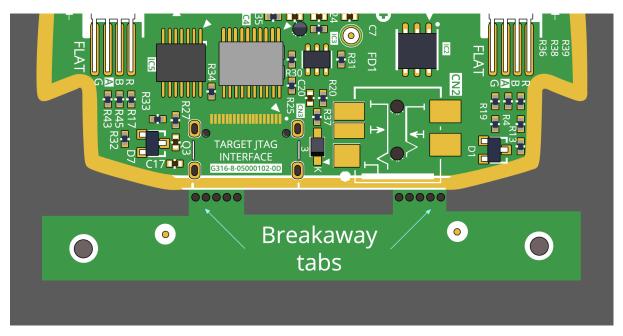

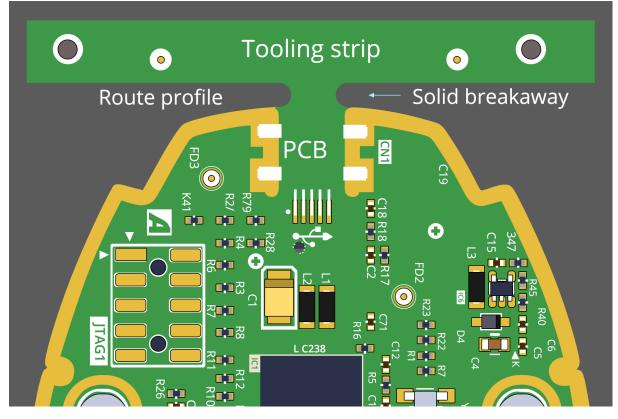

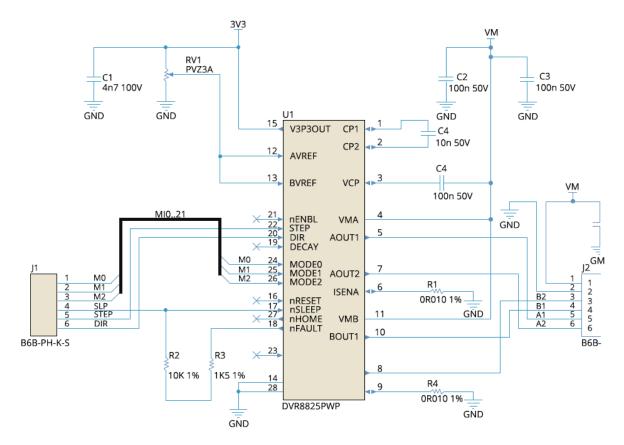

Before undertaking a Design for Manufacturing process, it is important to understand the underlying process behind producing a physical PCB. Regardless of the various technologies present in each facility, a large majority of industry-leading manufacturers follow a specific set of steps to turn your design from digital bits to physical boards. The steps in this process are outlined in Figure 1 and includes:

#### Standard PCB Manufacturing Process

**Data Transfer from Customer:** Gerber, GerberX2, IPC-2581, ODB++, Netlist, NC-Drill, Fab Drawing, Specs

**Data Prep:** Conversion of customer supplied data to tooling (Panelization, Artwork, Drill and Route programs)

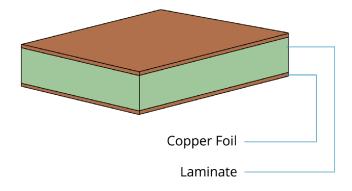

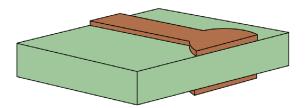

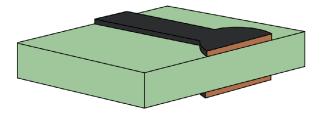

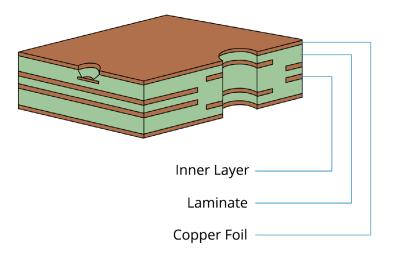

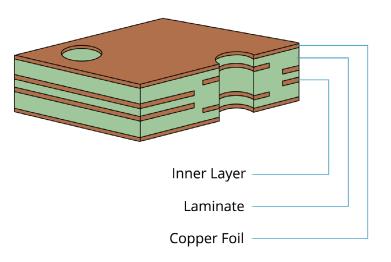

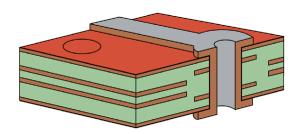

**Cores/Laminate:** Thin laminate material consisting of glass epoxy substrate clad with copper on sides (FR-4 is most commonly used material for PCB design)

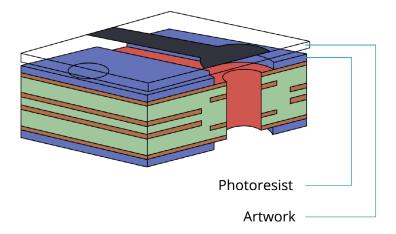

**Dry Film Resist Coating:** Using heat and pressure, a light sensitive film is applied to the copper surface of the core.

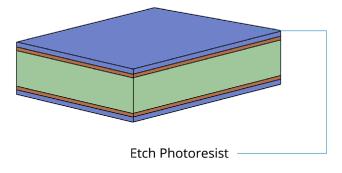

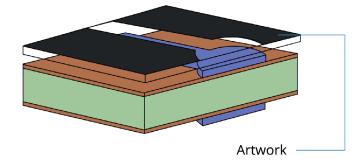

**Place Artwork:** Artwork patterns from the customer (circuits and land patterns) are placed on the film coated surfaces of the core. Each surface has its own artwork pattern.

**Expose Panels to Ultraviolet Light:** This creates a latent image of the circuit board.

**Develop Panels (resist removal):** Chemically remove the resist from areas not hardened by passing the exposed core through a chemical solution.

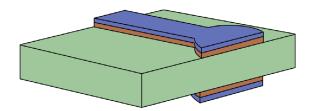

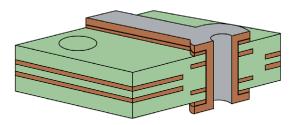

**Etch:** To chemically remove copper from core in all areas not covered by film resist, which creates a discrete copper pattern.

**Strip Resist:** Chemically remove the developed dry film resist.

**Oxide Coating:** Chemically treat copper to roughen surface and improve adhesion to prepreg during the lamination cycle.

**Multilayer Lamination:** Copper foil, prepreg (multilayer glue), and cores are bonded together under heat and pressure.

**Primary Drilling:** Holes are drilled through a stack of panels (double sided/single sided start here).

**Deburr and Clean:** Mechanically remove copper burrs and clean debris from drill holes.

**Desmear:** Chemically remove resin coating from the hole wall.

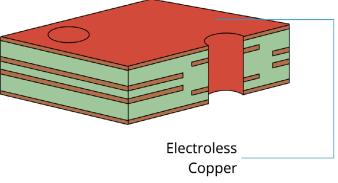

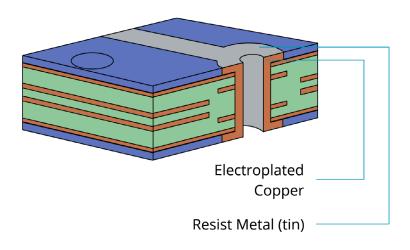

**Copper Deposition:** Chemically deposit a thin coat on the panel surface and hole walls.

**Dry Film Photoresist Coat:** Using heat and pressure, a light sensitive film is applied to the copper surface.

**Expose & Develop:** Similar to the inner layer process for the core.

**Copper Pattern Plate (electroplating):** Additional copper (as well as tin) is electrically plated into the exposed electroless copper surfaces, as well as tin.

**Etch:** Copper is now removed from any area not covered by tin.

**Strip Resist:** Developed dry film resist is chemically removed. Tents that were placed have prevented plating from occurring in "non-plated" holes.

**Solder Mask and Cure:** Liquid photoimageable mask is applied to each surface and dried to the touch. Artwork is also applied and exposed. PPanel is developed, leaving mask pattern defined by artwork.

**Hot Air Solder Leveling (most common PCB surface finish):** Panels processed through a molten solder bath, which covers all exposed copper surfaces.

Surface Finishes: RoHS or not RoHS compliant.

**Hot Air Leveling (HAL, HASL):** Convey PCB through flux station, solder bath, and then through air knives (to remove level excess solder).

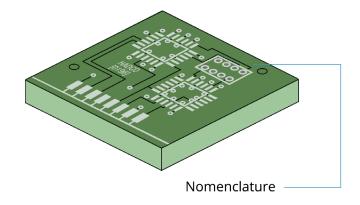

**Legend and Cure:** Top and bottom overlays (silkscreens) are inked onto each side of the panel per customer artwork, then the panels are baked to cure the ink.

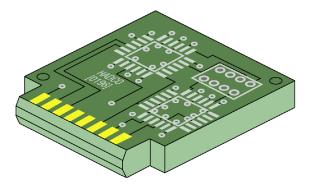

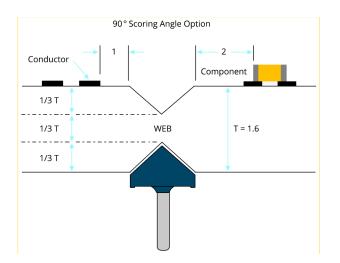

**Fabrication and Routing:** Board is cut to size (a.k.a routing, scoring, punching, or profiling). Slots and chamfers are also added during this step.

**Electrical Test/Final inspection:** Board is tested for electrical integrity (and impedance if required). Shorts and opens are repaired at this point. Flying probes are usually used for smaller lots, and bed of nails test fixtures are used for larger volumes. Other functions usually performed during this step include: automatic optical inspection (AOI) which compares the inner and outer layers cost drivers on PCB against downloaded CAM data for integrity and design rules, reliability testing, and statistical process control (SPC) when required by the customers.

With the final curing of your board complete, a manufacturer will then begin the electrical test process with the provided test points you established on your board layout. All boards that pass this verification process are considered complete and then make their way through shipping and transport.

#### Typical Cost Drivers in the PCB Manufacturing Process<sup>[1-1]</sup>

The cost to have your board manufactured is largely determined by the specific materials and parts that you specify during your design phase. Informed engineers will take their time to carefully balance cost drivers with the need to meet intended functional requirements as outlined in their product's specifications. Some of the most common cost drivers and cost reduction strategies in the manufacturing process are outlined in the table below and includes:

| Cost Driver                        | How to Reduce It                         |

|------------------------------------|------------------------------------------|

| PCB size, shape and edge clearance | Panelize and add tabs                    |

| Non-standard parts and packaging   | Use standard parts and packaging         |

| Layer counts                       | Reduce the number of layers if possible  |

| Build/Complexity                   | Reduce complexity (buried vias, etc)     |

| Additional manual setups           | Place components on one side of board    |

| Number of part types               | Minimize component types used            |

| Parts placed manually              | Use press-fit or SMDs                    |

| Selective solder fixtures          | Use press-fit or single sided SMD        |

| Component pre-load capability      | Component lead design allows pre-loading |

| Hole size and quantity             | Reduce and use standard hole sizes       |

| Two-sided assembly                 | Use captive press-fit studs              |

#### Making Manufacturing-conscious Design Decisions

By understanding the above knowledge about the typical PCB manufacturing process, you will be well on your way towards making more informed choices at design time for materials and part selections. With an understanding of the manufacturing process behind us, it is now time to jump into a practical Design for Manufacturing process, starting with material selection.

## **Selecting Your Materials**

#### Introduction

Every design process begins with material selection, and this chapter focuses on selecting the right materials for your PCB design given the particular design requirements you outline in your specifications. We will be focusing largely on FR-4 as it is the most commonly used material for PCB design. If your specific material requirements are not listed in the sections below, please contact your manufacturer for further guidance.

#### **Basic Material Selection Process**

When designing a PCB, there are several material choices to consider based on your unique design needs. Before selecting a material, it is recommended to first define the functionality and reliability requirements that your board must meet. These requirements will typically include:

- Electrical properties

- Thermal properties

- Interconnections (soldered components, connectors, etc...)

- Structural board integrity

- Circuit density

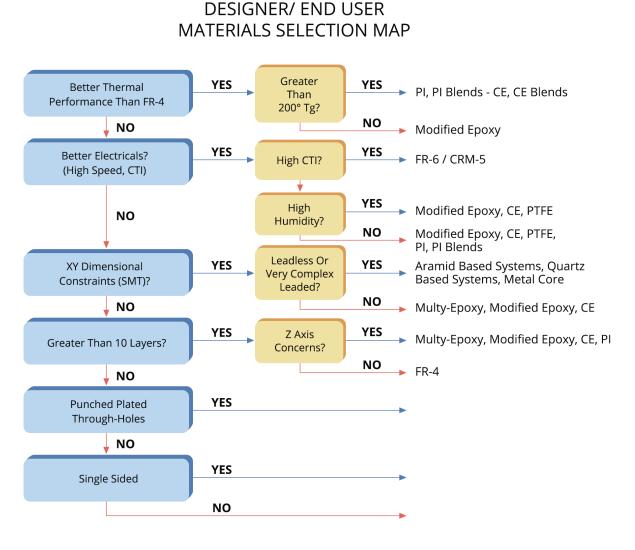

As a general rule, remember that the more you increase your design complexity and properties the more costs you will incur during your manufacturing process. A carefully crafted balance should always be made to meet both budget, functionality, and reliability goals for your particular design needs. See Figure 2 for a visual on how to begin your material selection process<sup>[2-1]</sup>.

Figure 2 - Designer/End-User Materials Selection Map[2-1]

#### **Additional Criteria for Material Selections**

As you begin constructing a composite from your chosen materials, you will want to pay close attention to temperature characteristics. In practice, the lowest-rated material will dictate the maximum end product temperature. Other items that should also be considered when comparing different materials includes:

- Resin formula

- Flame resistance

- Thermal stability

- Structural strength

- Electrical properties

- Flexural strength

- Maximum continuous safe operating temperature

- Glass transition temperature (Tg)

- Reinforcing sheet material

- Nonstandard sizes and tolerances

- Machinability or punchability

- Coefficients of thermal xpansion (CTE)

- Dimensional stability

- Overall thickness tolerances

The sections that follow will dive into some of the various material properties in detail for the primary components that make up a PCB design including electrical properties, FR-4, and copper.

#### **Material Properties in Detail**

#### **Electrical Properties**

The most critical properties to consider for electrical requirements are the electrical strength, dielectric constant, and moisture resistance.

Refer to Figure 3 for a list of some of the more common materials and their associated property values. Remember to consult with your manufacturer for more specific data on electrical properties.

|                                           | Material                |                          |                             |                                |                        |                       |

|-------------------------------------------|-------------------------|--------------------------|-----------------------------|--------------------------------|------------------------|-----------------------|

| Property                                  | FR-4<br>(Epoxy E-glass) | Multifunctional<br>Epoxy | High<br>Perfomance<br>Epoxy | Bismalaimide<br>Triazine/Epoxy | Polyimide              | Cyanate Ester         |

| Dielectric<br>Constant (neat resin)       | 3.9                     | 3.5                      | 3.4                         | 2.9                            | 3.5-3.7                | 2.8                   |

| Dielectric<br>Constant<br>(reinforcement) |                         | _                        |                             | _                              |                        | —                     |

| Electric Strength<br>(V/mm)               | 39.4 x 10 <sup>3</sup>  | 51.2 x 10 <sup>3</sup>   | 70.9 x 10 <sup>3</sup>      | 47.2 x 10 <sup>3</sup>         | 70.9 x 10 <sup>3</sup> | 65 x 10³              |

| Volume Resistivity<br>(D-cm)              | 4.0 x 10 <sup>6</sup>   | 3.8 x 10 <sup>6</sup>    | 4.9 x 10 <sup>6</sup>       | 4 x 10 <sup>6</sup>            | 2.1 x 10 <sup>6</sup>  | 1.0 x 10 <sup>6</sup> |

| Water Absorption<br>(wt%)                 | 1.3                     | 0.1                      | 0.3                         | 1.3                            | 0.5                    | 0.8                   |

| Dissipation Factor<br>(DX)                | 0.022                   | 0.019                    | 0.012                       | 0.015                          | 0.01                   | 0.004                 |

Figure 3 - Typical Properties of Common Dielectric Materials [2-2]

#### FR-4 Default Values

The default values in Figure 4 below for FR-4 can be used as a baseline for determining your specific material requirements. These values will change depending on your specified base material and thickness as shown in the next sections.

|                         |          | FR4<br>Standart | FR4<br>High-TG | FR4<br>Halogen Free | FR4 KF       | Polyimid |

|-------------------------|----------|-----------------|----------------|---------------------|--------------|----------|

| TG                      | Ĉ        | > 135           | >170           | >140                | >135         | >230     |

| CTE-z                   | ppm/℃    | 60              | 45             | 45                  | 50           | 20       |

| Permittivity Er         | bei 1MHz | 4.6             | 4.8            | 4.7                 | 4.7          | 3.4      |

| Electrical strength     | KV/mm    | 45              | 55             | 50                  | 45           | 125      |

| Surface resistivity     | MΩ       | 10^6            | 10^7           | 10^7                | 10^7         | 10^6     |

| Tracking resistance CTI | V        | PLC3*           | PLC3*          | PLC3*               | PLC1 / PLC** | —        |

| Td value                | °C       | 301             | 345            | 360                 | 310          | ***      |

| Peel strength           | N/mm     | 1.1-1.6         | 1.2            | 1.4                 | 1.6          | 1.6      |

| Flammability class      | UL-94    | V0              | VO             | V0                  | V0           | V0       |

| Standart                |          | IPC-4101        | IPC-4101       | IPC-4101            |              | IPC-4204 |

Figure 4 - Default FR-4 Material Values<sup>[2-3]</sup>

#### **FR-4 Base Material and Thickness**

The values in Figure 5 below list the most common FR-4 materials used today for multilayer board designs and will help you to choose the appropriate thickness for your FR-4. The thickness of specific variations of FR-4 including GETEK®, Rogers®, FR-406 and FR-408 are similar and can also be calculated using this table.

| Core                         | Coper<br>Weight (oz) | Nominal Material<br>Thickness (mm) | Measure Material<br>Thickness (mm) |

|------------------------------|----------------------|------------------------------------|------------------------------------|

| (Basic material with copper) |                      | (Base material)                    |                                    |

| 5                            | 0.5/0.5              | 0.125+0.025                        | 0.125                              |

| 6                            | 0.5/0.5              | 0.150+0.025                        | 0.142                              |

| 8                            | 0.5/0.5              | 0.200+0.025                        | 0.188                              |

| 10                           | 0.5/0.5              | 0.250+0.038                        | 0.228                              |

| 12                           | 0.5/0.5              | 0.300+0.038                        | 0.227                              |

| 15                           | 0.5/0.5              | 0.380+0.05                         | 0.358                              |

| 21                           | 0.5/0.5              | 0.635+0.0635                       | 0.632                              |

| 28                           | 0.5/0.5              | 0.711+0.0635                       | 0.716                              |

| 42                           | 1/1                  | 1.066+0.125                        | 1.069                              |

Figure 5 - FR-4 Material Thickness Reference<sup>[2-4]</sup>

#### **FR-4 Prepreg Designation and Thickness**

Prepreg (Pre-impregnated) is the sheet material (e.g. glass fabric) that is cured with a resin and cured to an intermediate stage. Most PCB manufacturers will carry five types of prepreg including 106, 1080, 2113, 2116, and 7628. Refer to Figure 6 for specific thickness specifications for each prepreg type.

Note: There are limitations to the type and number of prepreg sheets that can be placed between board layers. Consult with your manufacturer about your specific board layout needs to determine your correct prepreg designation and thickness.

| Glass Style | Glass Style<br>Thickness mm |

|-------------|-----------------------------|

| 106         | 0.053 (0.002")              |

| 1080        | 0.0787 (0.003")             |

| 2113        | 0.100 (0.004")              |

| 2116        | 0.135 (0.005")              |

| 7628        | 0.193 (0.0075")             |

| Glass Style | Resin Content | Thickness* (Mils) |

|-------------|---------------|-------------------|

| 106         | 72-77         | 2.1-2.8           |

| 1080        | 61-67         | 2.8-3.4           |

| 2113        | 53-56         | 3.8-4.6           |

| 2116        | 51-57         | 4.6-5.4           |

| 7628        | 40-46         | 7.2-8.0           |

\*This is the maximum possible thickness contribution

#### **Copper Foil Types**

Manufacturers will typically offer various types of foil for you to choose from, the most common being Electro-deposited Copper (ED Copper) and Rolled Copper. Rigid boards will typically use electrodeposited copper foil whereas rigid-flex boards will use rolled copper foil. Regardless of which copper foil type you choose, they will all meet your standard IPC-MF-150 requirements<sup>[2-5]</sup>. If you choose an alternative foil type such as nickel or aluminum, be sure to specify the characteristics on your master drawing to avoid any miscommunication or manufacturing issues.

#### **Copper Resistance Values**

As boards get denser and more complex, it becomes increasingly important to calculate your copper's distributed resistance. You can use the formula<sup>[2-6]</sup> below to easily compute the resistivity in your copper traces:

#### $\underline{\mathsf{R}} = \rho^* \mathsf{L} / \mathsf{A}$

where:

**R** is the end-to-end track resistance in Ohms

${\boldsymbol{\rho}}$  is the resistivity of the track material in Ohm Metres

L is the track length in metres

A is the track cross sectional area in square metres

You can also use one of the free tools below to quickly calculate your copper resistivity without needing to perform manual calculations:

- Circuit Calculator<sup>[2-7]</sup>

- EEWeb Trace Resistance Calculator<sup>[2-8]</sup>

- Endmemo Resistance Calculator<sup>[2-9]</sup>

#### **Current Carrying Capacity of Copper**

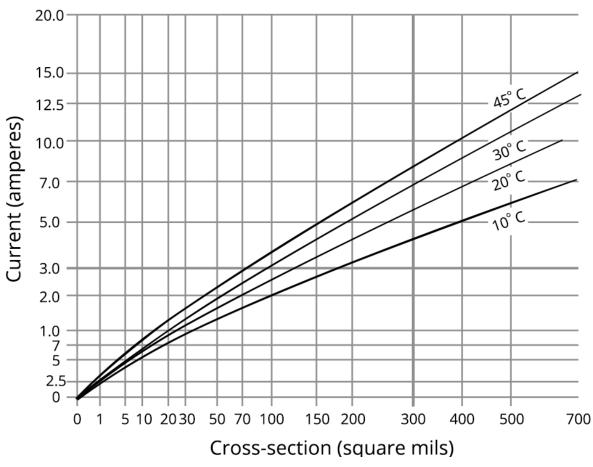

In Figure 7 can be used as a reference to understand the current carrying capacity of internal layers for common copper thicknesses and temperature levels above ambient. The current carrying capacity for external layers is approximately 2x that of internal layers. For more detailed data on line widths and spacing requirements refer to IPC-2221<sup>[2-10]</sup>.

#### Encapsulated conductor

#### Conductor width (w) vs cross-section

Figure 7 - Encapsulated Conductor Widths<sup>[2-10]</sup>

#### **Finished Board Thickness**

As part of your final material selection process, you will want to calculate your finished board thickness. This measurement is made from copper-to-copper and will represent your maximum finished board thickness. Some specifics to keep in mind about board thickness calculation includes:

- Board thickness will determine how your manufacturer sets up their processing machinery.

- Board thickness will affect the limitations of your board during manufacturing, including aspect ratios.

- Manufacturers typically offer lamination thicknesses between 0.0008" to 0.240" including the solder mask.

- Boards with less than 0.05" thickness will typically require special handling and processing, which could result in higher costs and longer processing times.

#### **Finalizing Your Material Selections**

You now have the knowledge needed to finalize your basic material selections for your next manufacturable-ready PCB design. To summarize, the base materials and the required property values you will need before you begin your design process includes:

| FR-4         | Base Material             |

|--------------|---------------------------|

|              | Thickness                 |

| FR-4 Prepreg | Designation               |

|              | Thickness                 |

| Copper Foil  | Туре                      |

|              | Resistance                |

|              | Current Carrying Capacity |

With these values in hand, you can then calculate your maximum board thickness which will have a direct impact on both manufacturing costs and processing requirements by your manufacturer. The next section will cover how to strategize your PCB layout for manufacturing including via/hole placement, soldermask layers, silkscreen documentation, and more.

## Strategizing YourPCB Layout

#### Introduction

With your material selections finalized, it is now time to dive into the specific details of your PCB layout. While individual engineering workflows might differ from one designer to the next, there are a number of primary design considerations that have a need for precise DFM requirements to consider a board 100% ready for manufacturing. In the following sections you will learn the specifics of strategizing your PCB layout including SMT and through-hole specifications, silkscreen documentation, solder mask applications, and more.

#### **Deciding Between Through-hole or SMT**

When designing a PCB, it is typical to either choose surface mount technology (SMT) or through-hole for your component applications. If you do happen to use both manufacturing methods, then your board is considered a hybrid PCB. Based on current industry trends in PCB design, it is recommended that most of your components be surface mounted devices (SMD), as this technology has dominated the PCB design market since the 1990s and includes many advantages including higher board densities at a lower cost. Keep the following in mind when deciding between SMT and through-hole:

- PCBs with plated through-hole devices (PTHs) are wave-soldered, whereas PCBs with surface-mount devices (SMDs) can be wave or reflow soldered.

- Mixing these two technologies will result in separate processes to manufacture your board and will add to your overall manufacturing time and cost.

- Some manufacturers will hand-install through-hole components which will add to your overall manufacturing time and cost.

The component application method you choose will have a direct impact on your overall costs and manufacturing time. It is recommended to stick with SMT for professional board designs as this results in quicker board turnarounds and higher reliability.

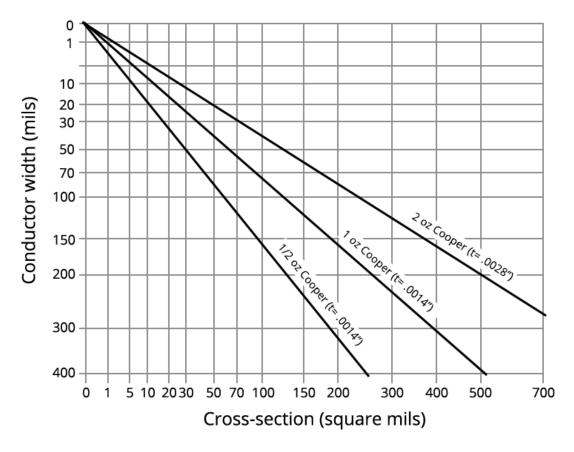

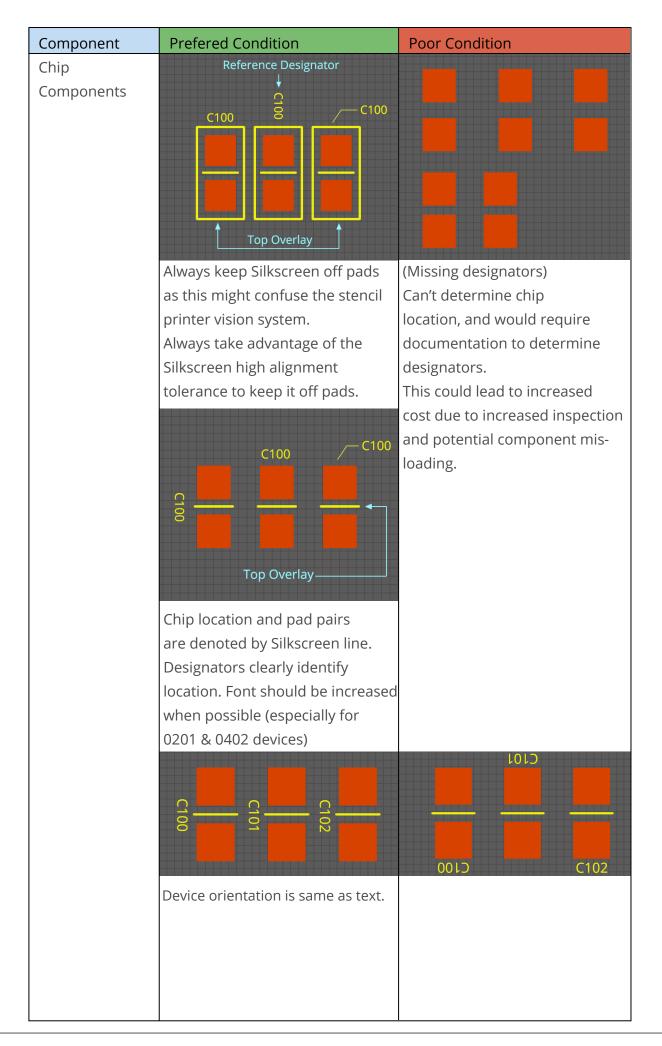

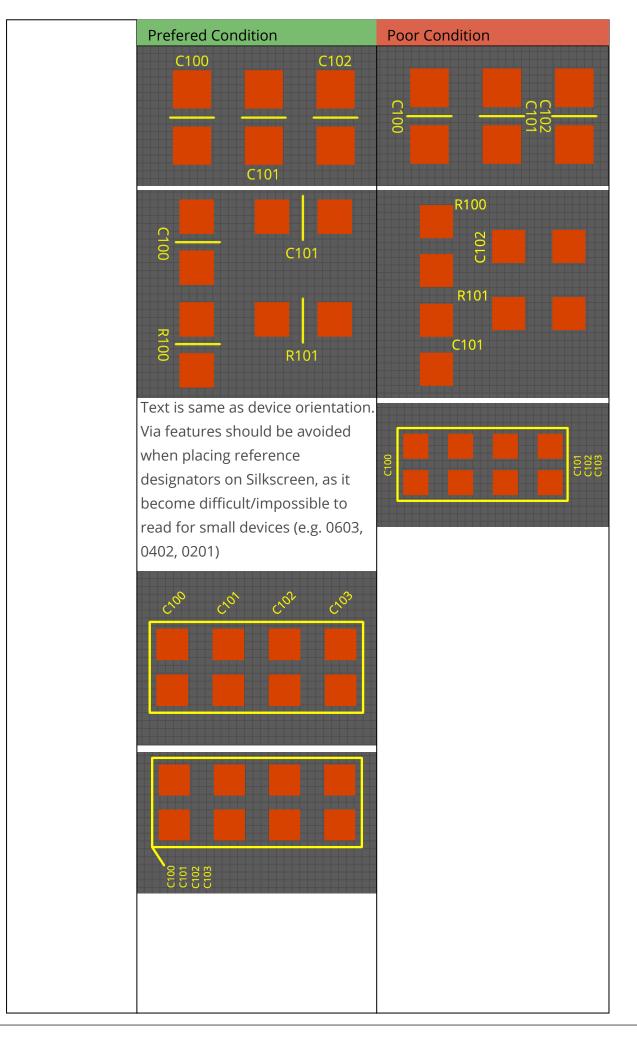

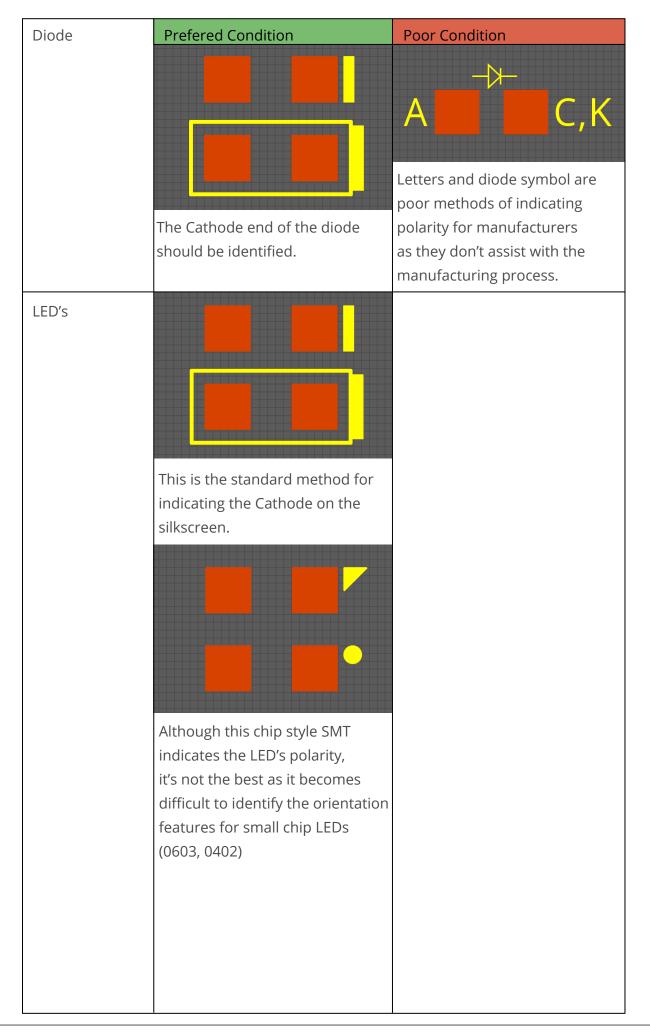

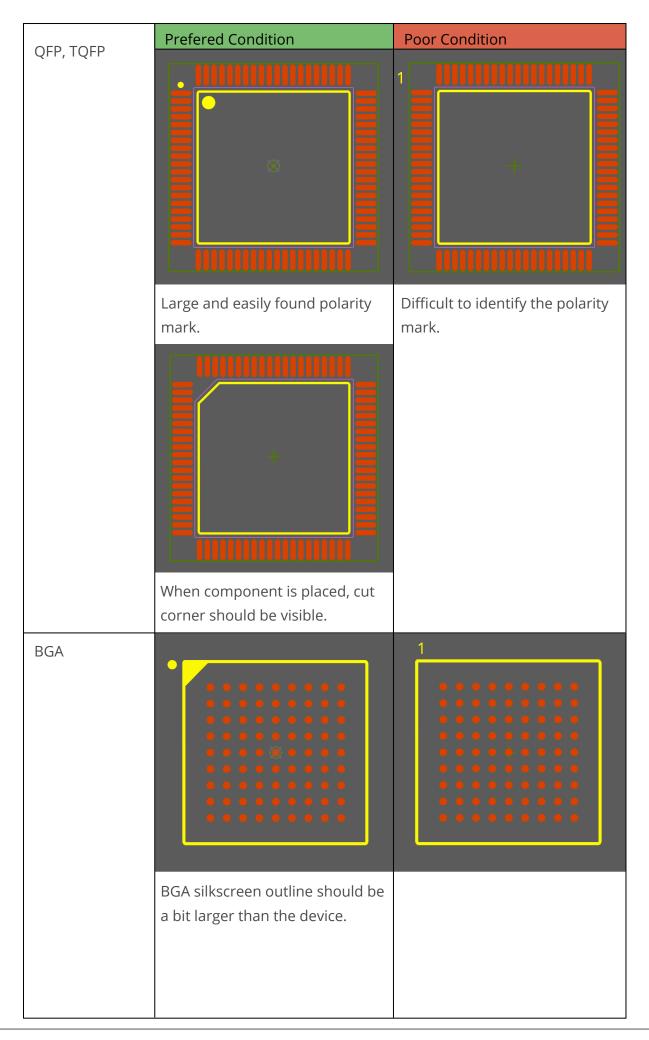

#### Silkscreen and Component IDs

All component outlines on your silkscreen should be marked with a reference designator and polarity indicators (if applicable). It is important to make sure these designators and indicators are readable and visible even after components are installed for easy post-production verification. Figure 8 includes recommended guidelines on where reference designator locations and polarity markings should be placed on your silkscreen:

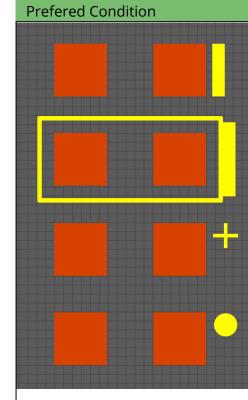

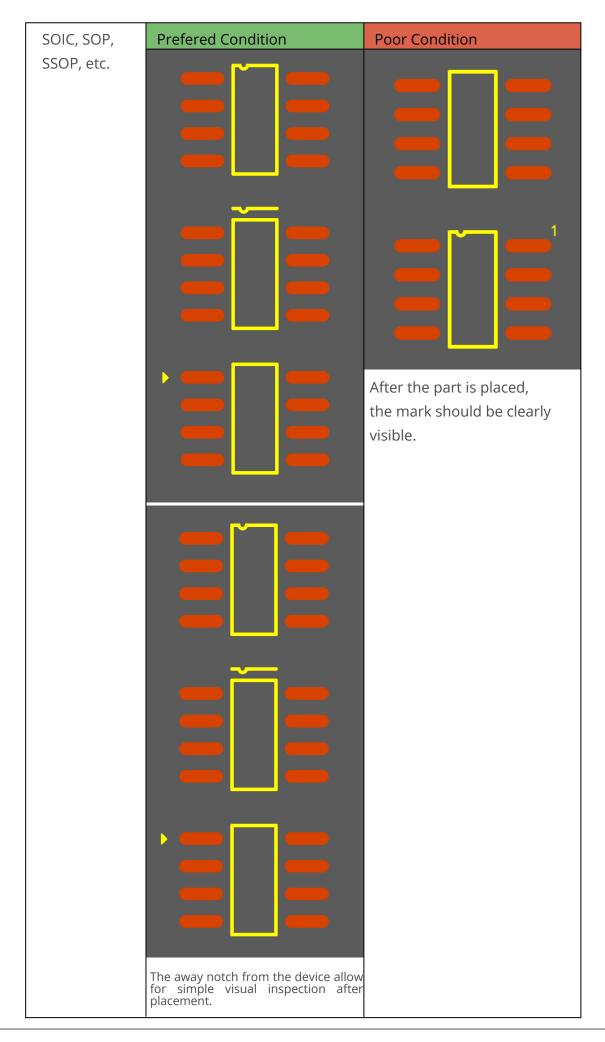

#### Polarized

#### Capacitors

Unmarked polarized locations can complicate the assembly process, which can lead to delays to process the first article. Not to mention the danger associated with mounting a polarized capacitor in reversed orientation.

**Poor Condition**

Mark the Anode (+) side of the capacitor on the silkscreen and it's best to use a bar that is equal to the pad's width. This will correspond to the line on the component (in general).

A "+" or "dot" are fine for indicating polarity, however they don't represent the general standards for SMT polarized capacitors (which uses a line or a bar).

From a manufacturer perspective, all that is important to them is to be able to align the component correctly rather than determining the Anode (or Cathode) orientation.

| Prefered Condition         | Poor Condition                  |

|----------------------------|---------------------------------|

|                            |                                 |

| Easy to identify polarity. | Can't easily identify polarity. |

| Clear visible polarity.    |                                 |

Figure 8 - Placement for Component Reference Designations

#### **Component Reference Designators**

Figure 9 includes a list of industry-standard reference designators from the IPC-2612<sup>[3-1]</sup> standart for schematic symbol generation. It is recommended to use these designators in all of your board layouts to help keep all of your projects consistent.

| A<br>AR<br>AT<br>B<br>T<br>C<br>CB<br>CP<br>CN              | separably assembly<br>amplifier<br>attenuator, isolator<br>blower, motor<br>battery<br>capacitor<br>circuit breaker<br>connector adapter, coupling<br>capacitor network | LS<br>M<br>MG<br>MH*<br>MK<br>P<br>PS<br>Q | loudspeaker, buzzer<br>meter<br>motor-generator<br>mounting hole<br>microphone<br>mechanicalpart<br>connector, plug, male<br>power supply<br>transistor |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D or CR                                                     | diode                                                                                                                                                                   | R                                          | resistor                                                                                                                                                |  |

| D or VR                                                     | breakdown diode                                                                                                                                                         | RN                                         | resistor network                                                                                                                                        |  |

| DC                                                          | directional coupler                                                                                                                                                     | RT                                         | thermistor                                                                                                                                              |  |

| DL                                                          | delay line                                                                                                                                                              | S                                          | switch                                                                                                                                                  |  |

| DS                                                          | display, lamp                                                                                                                                                           | Т                                          | transformer                                                                                                                                             |  |

| E                                                           | terminal                                                                                                                                                                | ТВ                                         | terminal board, terminal strip                                                                                                                          |  |

| F                                                           | fuse                                                                                                                                                                    | тс                                         | thermocouple                                                                                                                                            |  |

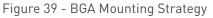

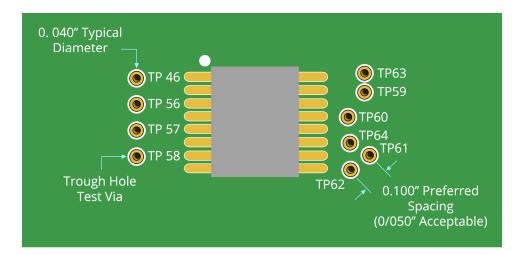

| FD                                                          | fiducial                                                                                                                                                                | TP*                                        | test point, in-circuit test points                                                                                                                      |  |

| FL                                                          | filter                                                                                                                                                                  | ΤZ                                         | transzorb                                                                                                                                               |  |

| G                                                           | generator, oscillator                                                                                                                                                   | U                                          | inseparable assembly, IC pkg                                                                                                                            |  |

| GN                                                          | genera network                                                                                                                                                          | V                                          | electron tube                                                                                                                                           |  |

| н                                                           | hardware                                                                                                                                                                | VR                                         | voltage regulator                                                                                                                                       |  |

| HY                                                          | circulator, directional coupler                                                                                                                                         | W                                          | wire, cable, cable assembly                                                                                                                             |  |

| J                                                           | connector, jack, female                                                                                                                                                 | Х                                          | fuse holder, lamp holder, socket                                                                                                                        |  |

| К                                                           | contactor, relay                                                                                                                                                        | Y                                          | crystal, magnetostriction oscillator                                                                                                                    |  |

| L                                                           | coil, inductor, bead, ferrite bead                                                                                                                                      | Z                                          | miscellaneous                                                                                                                                           |  |

| Figure 9 - Component Reference Designators <sup>[3-1]</sup> |                                                                                                                                                                         |                                            |                                                                                                                                                         |  |

\*Not a class letter, but commonly used to designate test points for maintenance purposes.

Note: The above list is not exhaustive. See the standard list of class designation letters in **ANSI Y32.2/IEEE Std 315**<sup>[3-2]</sup>, Section 22 and the Index.

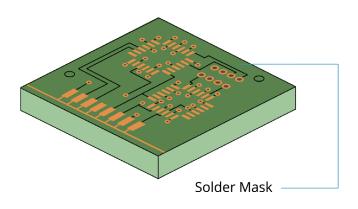

#### Solder Mask

The solder mask is a thin, lacquer-like layer applied as a final coating to your PCB to protect various features including copper traces and ground planes that should not be soldered. Some of the benefits of solder masking includes:

- Protecting your PCB against oxidation damage.

- Preventing thieving and solder bridging (shorts) between conductors and lands.

- Preventing flaking during the assembly process if placed directly over bare copper.

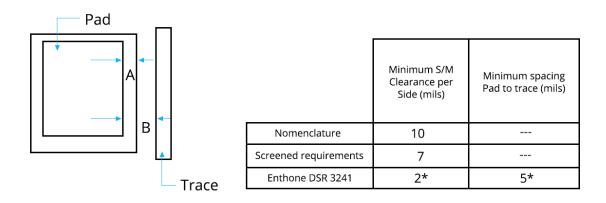

#### **Basic Clearance Requirements for Solder Mask**

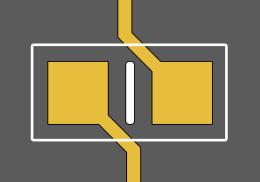

Wherever soldering or electrical contact is needed (around SMD and PTH pads, tooling holes, shield contact areas, fiducials, etc...) a solder mask clearance is required. Specifying a solder mask clearance ensures that there is no encroachment of the solder mask on pads during fabrication, which can result in a smaller solder fillet or completely disconnected pads if proper clearance requirements are not specified. Refer to Figure 10 below for proper clearance requirements for solder mask on pads and traces:

| А | В |

|---|---|

|   |   |

|   |   |

|   |   |

#### \* IPC A600 Rev E class II and III acceptance requirement

In the example above, if minimum spacing between the pad and trace (column B) is less than required, then solder mask will be applied to the pad or exposed metal on the trace and could result in a board malfunction.

#### Solder Mask between SMD Pads

If there is a need for solder mask between SMD pads and there is not enough spacing to apply it, then it is recommended to keep two things in mind:

- The minimum spacing provided between the pads.

- The minimum successfully reproducible solder mask size your manufacture can make.

With these two requirements in mind, it is recommended to either increase the spacing between the pads for solder mask application or consult with your manufacturer to determine additional alternatives.

#### Vias and Holes

Vias are a critical part of every PCB design and are responsible for transmitting electrical current between layers. They can also be a significant burden to manufacturing costs if consistent clearance and sizing guidelines are not followed. The sections below will cover the specifics of via and hole clearances, sizing guidelines, and specific via applications.

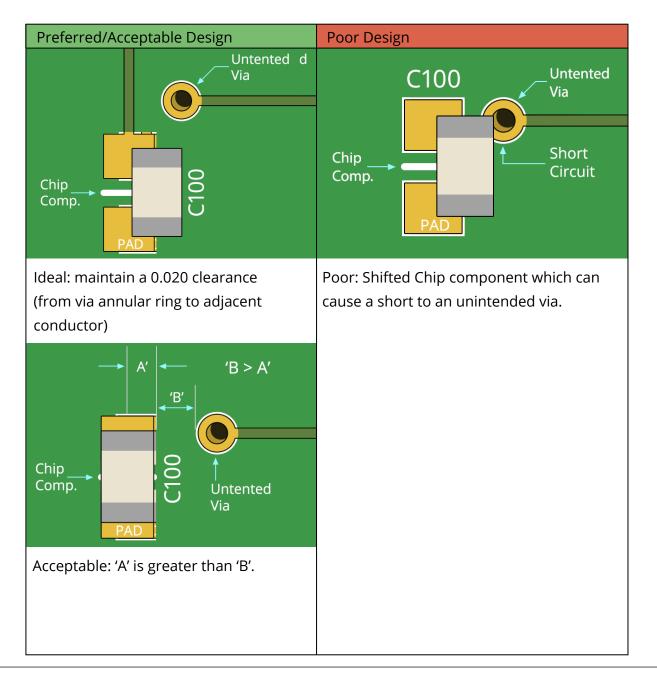

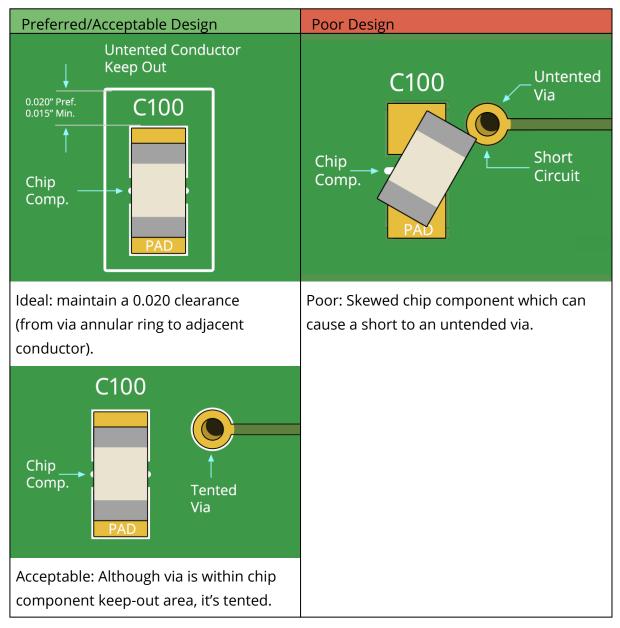

#### **Via Clearance Requirements**

Standard vias should maintain minimum clearances from adjacent conductors, and the clearance will largely depend on whether the via is tented or exposed.You will often find that exposed vias will require greater clearances to close exposed electrical connections when compared with masked vias.

#### Via Size Guidelines

When designing plated via holes, it is recommended to maintain a 1:1 aspect ratio between the hole diameter and the substrate thickness. This rule of thumb will ensure that adequate copper metal builds up throughout the entire hole during the fabrication process. For example, in a 0.20" thick substrate, holes should at least 0.20" in diameter. However, most manufacturers have a wide selection of drill hole sizes and will usually meet requirement outside this general recommendation. One thing to remember when choosing a hole size is that a finished plated-through hole will be narrower due to the plating. Figure 11 depicts typical standard drill sizes:

| Drill Number | Holes size | Finished Hole Size |

|--------------|------------|--------------------|

| 70           | .028″      | .025″              |

| 65           | .035″      | .032″              |

| 58           | .042"      | .039″              |

| 55           | .052"      | .049″              |

| 53           | .0595″     | .056″              |

| 44           | .086″      | .083″              |

| 1/8″         | .125″      | .122″              |

| 24           | .152″      | .149″              |

Figure 11 - Standard Drill Sizes for Vias and Holes

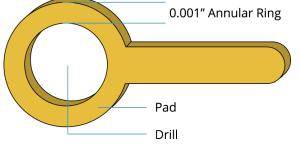

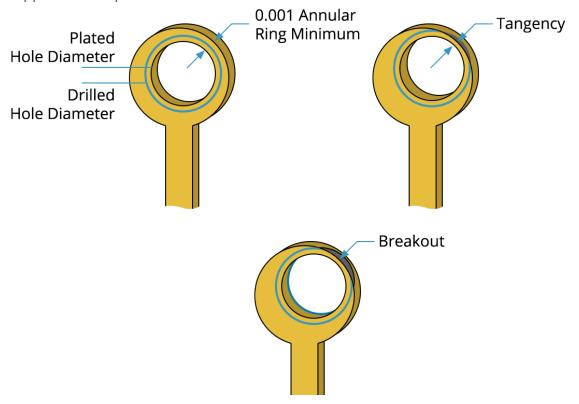

#### **Annular Rings**

The annular ring is the difference between the pad diameter and the corresponding drill diameter; in other words, the area on the pad that surrounds the via. Figure 12 shows how to easily calculate the width of an annular ring:

Annular Ring Width = (diameter of the pad - diameter of the hole) /2

Figure 12 - Recommended Annular Ring Width

There are many conditions that can cause the drilled hole not to be exactly at the center during manufacturing. If it is acceptable to include "tangency" on the pads of your finished product, then it is recommended to check with your manufacturer on their guidelines for minimum annual ring widths.

To ensure a 0.001" minimum annular ring on the finished product, all pads on your design should be 0.0008" (2 x 0.0004") larger than the drilled hole. This will ensure the drilled hole will be tangent to the pad's edge. If you do not plate your design's through-holes, it can result in smaller annular rings, which could result in the ring being lifted during soldering or breaking off during normal board operations. This occurs due to the lack of support from a plated barrel.

Figure 13 - Drilled and Plated Hole Diameters

# **Exposed Vias**

Exposed vias are exposed electrical connections that are not covered with solder mask. Open clearances for exposed vias to other vias or lands not adjacent to the pad should be 0.15" at a minimum, with 0.20" being preferred.

# **Tented Vias**

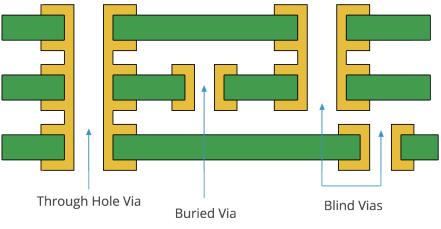

Tenting a via covers the via hole and annular ring with soldermask, and should be set as the default method in your design workflow. Keep in mind, there are usually no additional steps taken by your manufacturer to ensure a via opening remains closed. If you want to ensure that your via is closed and covered, you should specify in your fabrication print that you want these vias to be mask plugged, which is also called mask filled. This is especially important for BGA designs where vias are found close to the BGA's SMD pads.

Soldermask

Soldermask Dam

Oldermask Dam

O

See Figure 14 for examples of recommended via tenting applications:

## Via-in-pads and Micro Vias

Via-in-pads allows for close placement of bypass capacitors and makes routing easier for any ball pitch BGAs, as well as assists with thermal management and grounding. Follow the guidelines below when your design requires via-in-pads:

- The via-in-pads should be copper capped. In addition, the opposite side of the vias should be either copper capped (if used as an in-circuit test (ICT) point), or masked to ensure plating chemicals do not get trapped within the via.

- If the via-in-pads are not capped, additional assembly cost could incur to deal with solder wicking (redistribution of solder away from the intended joint) and solder scavenging (lack of enough solder and voids in intended joints).

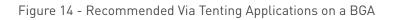

# **Blind and Buried Vias**

Similar to through-holes, blind and/or buried vias (BBV) are holes that connect one or more layers. In this process, a blind via connects an outer layer to one or more inner layers but not to both outer layers, and a buried via connects one or more inner layers, but not to an outer layer. This is important as these type of vias allow for denser boards and can save board real estate by not requiring any space on the components layers. See Figure 15 for an example of a blind and buried via application:

Figure 15 - Blind and Buried Vias

One particular detail to pay attention to when using blind vias is the drill depth (from an outside layer to an internal layer). For example, if you have a 0.062" thick board with 8 layers, the maximum depth of the blind via hole cannot exceed 0.018" (for a 0.035" via with a 0.018" hole).

As a general guideline, keep internal layer's via pads about 0.016" over the drill size, as this will provide a good yield for your manufacturer. It is recommended to consult with your manufacturer to further understand their BBV design constraints for copper weight, minimum drill size, and maximum aspect ratio requirements.

## Vias Under BGAs

Reflow processes can cause chip components to shift or skew, resulting in one side of the chip component shorting to a nearby exposed via. Because of this, it is recommended that BGA vias be tented as a default in your design rules. Use the guidelines below for recommended clearance spacing for the exposed keep out area:

- If a via is adjacent to an SMD pad, it should be a minimum of 50% component termination width.

- If a via is at the end of an SMD pad, it should be at a minimum of 0.15" (preferably 0.20").

Figure 16 show some examples of good design practices for vias that are placed near chip components:

Figure 16 - Via Placement Guidelines Near Chip Components

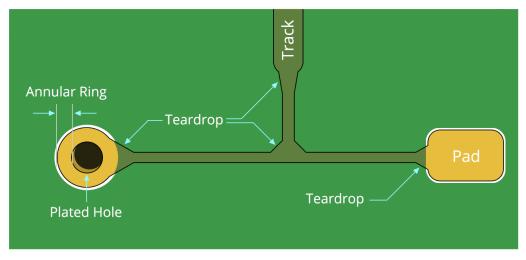

## **Teardrop Pads**

The purpose of adding a teardrop pad is to reduce the mechanical and thermal stress where the trace joins the pad by providing additional copper/metal support. This also helps to ensure that good connections are made and maintained as it increases the PCB manufacturer's tolerance when an order is drilled and a misregistration occurs.

The tear dropping process involves adding copper to the junction of an existing pad and a trace exit. It is important to primarily add these to through-hole drills, where you might have a small trace-to-pad ratio. They should also be added to circuit runs from a pad (solid or via pad), and this practice becomes more important as a trace narrows. For traces larger than 0.20", teardrops are usually not needed. As a rule, if your design is not an RF or high-frequency device, add tear drops at the final stage of your design. Figure 17 shows various teardrop examples and their recommended spacing and shape requirements:

Figure 17 - Recommended Teardrop Shapes

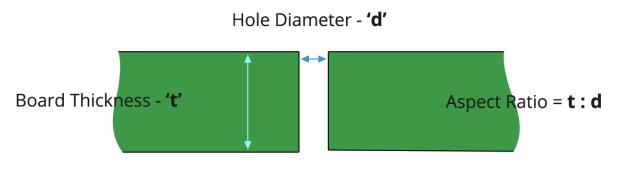

#### **Aspect Ratio Plating**

Aspect ratio is the ratio between the thickness of the board and the size of the drilled hole (before plating)<sup>[3-4]</sup>. TThis ratio will guide your manufacturer so they do not exceed the mechanical capabilities of their drilling equipment. Figure 18 shows a visual example of how aspect ratios are determined on a PCB:

Figure 18 - Determining an Aspect Ratio for a PCB

## Altıum.

For example, a PCB that has 0.065" thickness and consists of a hole size of 0.020" will have an aspect ratio equal to 3:1. This ratio is important as it relates to the plating process as well. Hole sizes that are too small compared to the board thickness (higher aspect ratios), might not achieve an acceptable copper plating when the plating solutions flow through the hole. Figure 19 provides a general set of guidelines for establishing aspect ratios:

| Drilled             | Board Thickness (mm)/Aspect Ratio |               |               |               |  |  |  |

|---------------------|-----------------------------------|---------------|---------------|---------------|--|--|--|

| Hole Size mm (inch) | 1.8 (0.070")                      | 2.35 (0.093") | 3.15 (0.125") | 6.75 (0.125") |  |  |  |

| 1.65 (0.065")       | OK                                | ОК            | ОК            | 4.1 : 1       |  |  |  |

| 1.65 (0.065")       | OK                                | ОК            | ОК            | 5.9 : 1       |  |  |  |

| 1.65 (0.065")       | OK                                | ОК            | ОК            | 7.6 : 1       |  |  |  |

| 1.65 (0.065")       | 2.8 : 1                           | 3.7 : 1       | 5.0 : 1       | 10.6 : 1      |  |  |  |

| 1.65 (0.065")       | 3.5 : 1                           | 4.65 : 1      | 6.25 : 1      | 13.3 : 1      |  |  |  |

| 1.65 (0.065")       | 3.9 : 1                           | 5.1 : 1       | 6.9 : 1       | 14.7 : 1      |  |  |  |

| 1.65 (0.065")       | 4.4 : 1                           | 5.8 : 1       | 7.8 : 1       |               |  |  |  |

| 1.65 (0.065")       | 5.2 : 1                           | 6.8 : 1       | 9.3 : 1       |               |  |  |  |

| 1.65 (0.065")       | 5.6 : 1                           | 5.6 : 1       |               |               |  |  |  |

| 1.65 (0.065")       | 7:1                               | 9.3 : 1       |               |               |  |  |  |

Figure 19 - Aspect Ratio Matrix for Specific Board Thicknesses<sup>[3-5]</sup>

#### Via Spacing, Placement, and Routing Guidelines

With your via sizing and types established, it is now time to start placing and routing them on your board layout. Below you will find several placement guidelines to keep in mind, especially for board layouts that utilize through-hole components or SIP-type packages.

#### Via Placement Recommendations for Through-hole Components

When your design consists of through-hole components, it is recommended to keep vias away from these devices as the via can cause the solder to flow up and damage those components. It is also recommended to keep vias away, around 0.100", from SIP packages, as these packages can be incorrectly inserted.

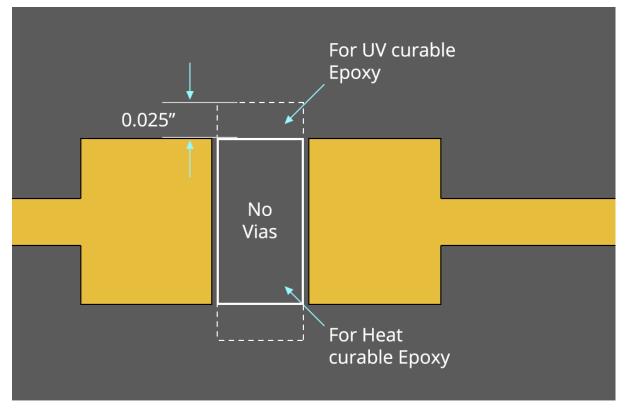

#### **General Via Placement Recommendations**

Since solder can flow up through vias, it is not recommended to place vias under chip components as this can result in a damaged, shorted, or lifted component. This is also important because sometimes chip components need to be glued or epoxied to the board, and a via under it or near it can interfere with that area (see Figure 20 for an example).

Figure 20 - Via Clearance Guidelines for Wave Soldering

When connecting a via edge to a component pad edge, clearances of less than 0.010" are not recommended unless you are designing a dense board. If your board is dense, then you will need to cover them with solder mask. It is recommended to consult with your manufacturer on the minimum clearances they require for denser boards. See Figure 21 for an example of recommended connections of vias to component pads:

Figure 21a - Recommended Connections of Vias to Pad Components (Good Design)

Figure 21b - Not Recommended Connections of Vias to Pad Components (Poor Design)

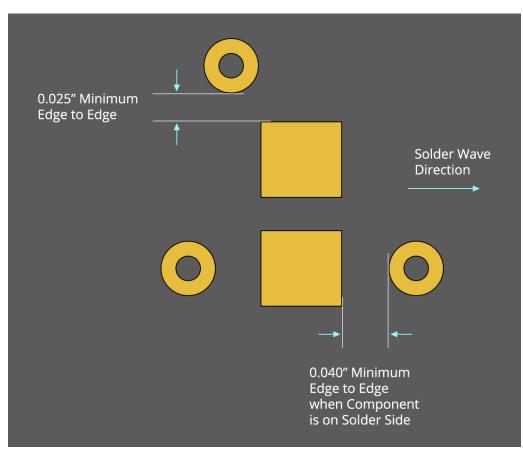

When not connecting a via to a component pad, a minimum of 0.025" clearance spacing is recommended, and this clearance should be increased to 0.040" if the via is on the solder side of the board.

See Figure 22 and make note of the wave solder direction:

Figure 22 - Via Component Spacing for Wave Soldering

## **Finalizing Your Via Requirements**

Vias are a critical piece of every electronics design and ensuring that your clearances, sizing, types, and routing methods remain consistent throughout your board will go a long way towards designing a manufacturable and cost-efficient board. The next section will focus on additional board layout strategies and other options to be aware of during your design process.

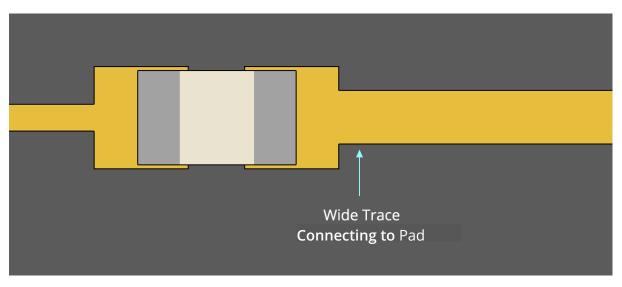

#### **Trace Routing to Component Lands**

When you have a component's termination that could generate heat and is connected to a large trace, the heat transfer produced can lead to a poor solder joint. This can even result in open solder joints for connections without a solder mask, as solder can migrate away from the component termination.

To resolve this issue, trace necking can help with thermal balance and prevent the solder and heat from flowing away from the pad.

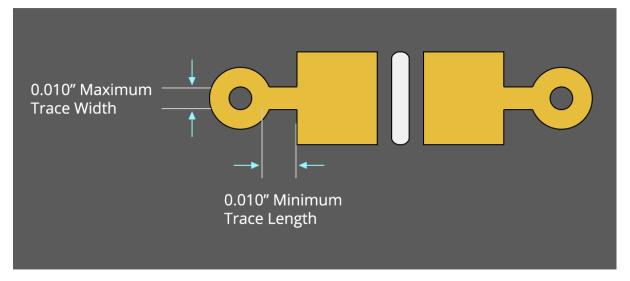

#### **Necking a Trace**

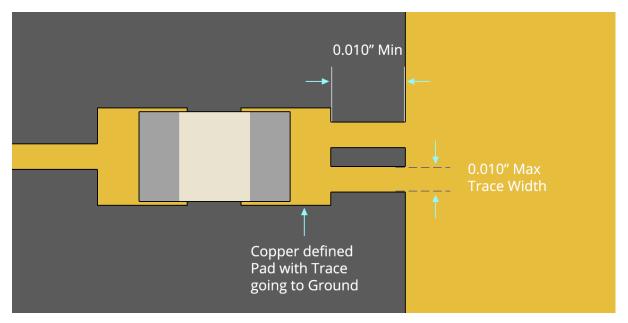

A general guideline for necking a trace is to keep it no wider than 0.010" where it connects to the pad and run it at least 0.010" before it connects to the large trace. If you have to connect a wide trace to a component land, they should have the same width while keeping the dimensions as small as possible. Figure 23 shows an example of this process:

Figure 23b - Connecting Large Traces to Component Lands (Good Design)

Figure 23b - Connecting Large Traces to Component Lands (Good Design)

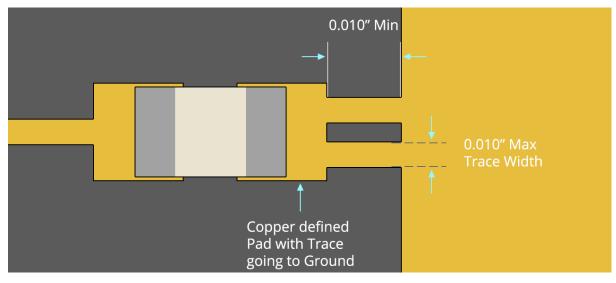

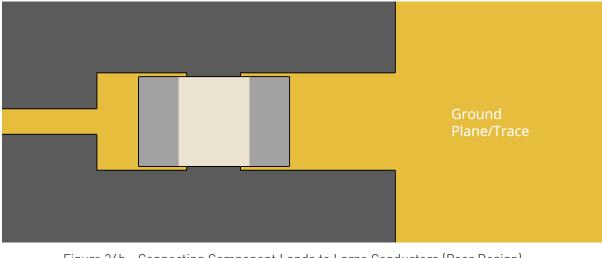

## **Connecting Large Ground Traces to Component Lands**

When you need to connect large ground traces to component lands, you should neck down the traces to ensure a good balance and to prevent heat transfer that might cause solder to travel to the large conductor area. You can also have multiple traces connecting land patterns to the large traces and ground planes. It is recommended to keep trace width (when necking) from the pad at a max of 0.010" and 0.010" as a minimum length from the pad to a large plane or trace. See Figure 24 for an example of these spacing recommendations:

Figure 24a - Connecting Component Lands to Large Conductors (Good Design)

Figure 24b - Connecting Component Lands to Large Conductors (Poor Design)

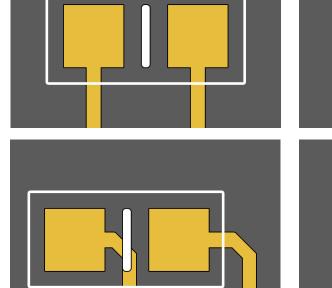

#### **Connecting Pads of Closely Spaced Components**

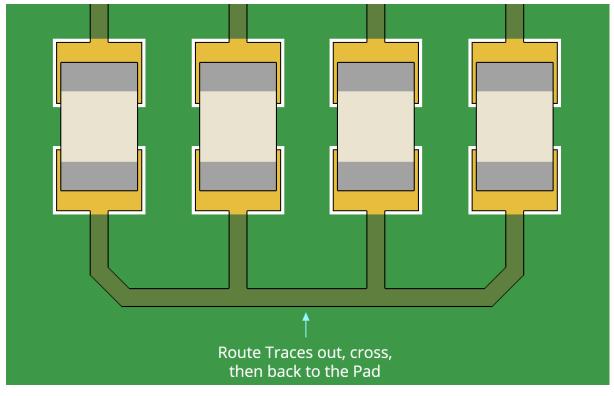

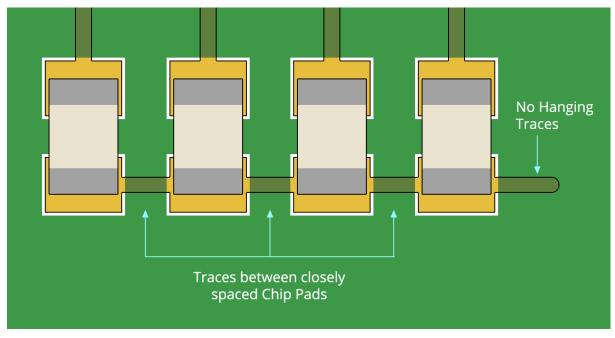

When connecting the pads of closely spaced chip components, it is recommended to route the traces out across and then back into the pads rather than having traces routed directly between the pads or across the pads. This will help prevent shorts that will be mistakenly reworked, prevent tombstoning due to poor thermal balances, and avoid cold solder joints and shifting of components. See Figure 25 for an example on how to properly connect pads to components:

Figure 25a - Connecting Pads of Closely Spaced Components (Good Design)

Figure 25b - Connecting Pads of Closely Spaced Components (Poor Design)

Figure 25c - Connecting Pads of Closely Spaced Components (Poor Design)

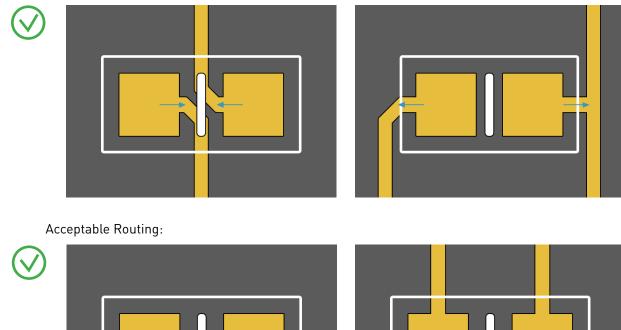

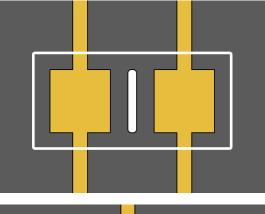

#### **Connecting Pads to Traces**

Every pad should be connected to its own trace, and it is recommended to have the routing from either outside the edges or inside the edges of the pads while keeping the routing symmetrical. This is important and critical in areas with no soldermask, as it helps prevent the solder from moving away from the pad and stops components from shifting. In general, most manufacturers will want to see a balanced amount of copper connecting the component pads. See Figure 26 for trace routing examples and preferred methods of connecting traces to chip pads.

Preferred Routing: (arrows indicate solder migration)

Non-Preferred Routing: (arrows indicate solder migration)

Figure 26 - Connecting Traces to Component Lands When Using Soldermask

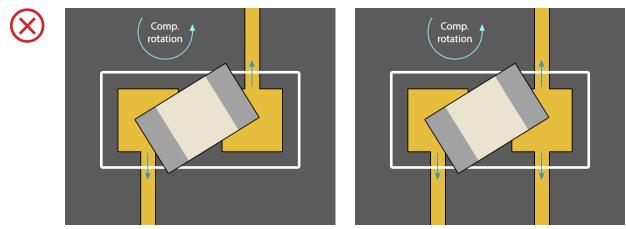

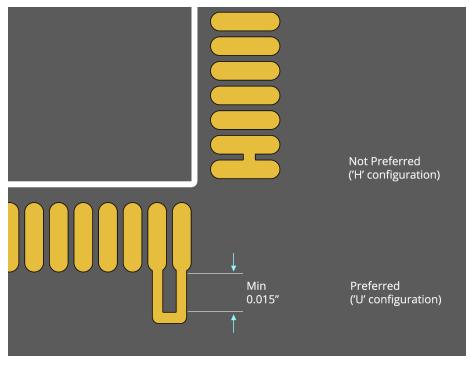

When routing leaded SMD components, it is recommended to route the trace over and then back in, forming a flipped "U" configuration, rather than forming an "H" by going directly between lands. See Figure 27 for an example of this "U" shaped configuration:

Figure 27 - "U" Configuration for Routing Leaded SMD Components

#### **Planes and Traces**

It is recommended to have your power and ground planes always on internal layers, symmetrical, and centered. This will help prevent your board from bending, and will also help with accurate positioning and component placement. Most assembly manufacturers allow a bow and twist of 0.7%-0.75% either for double layer PCBs or multilayer PCBs with 0.06" board thickness.

The same set of recommendations applies to traces. They should be as equally laid out as possible in both the X and Y axis and preferably in multi-orientation on all layers to help prevent board warping.

# **Plating Options**

For plated through-hole (PTH) boards, electroless copper is utilized to make the hole path conductive enough to allow further build-up of copper metal to a thickness specified by the designer, which is usually 0.001". The electroless copper process also adds an average of 0.0013" of copper to the external lines, in addition to the original copper foil (0.5 oz or 1 oz). Figure 28 summarizes the most common finish types for all exposed circuitry on a board. It is recommended to consult with your manufacturer for guidance on selecting a finish that will lessen material decay and improve surface consistency when connecting components on your board.

|                                 | HASL<br>(SnPb) | HASL<br>Lead-<br>Free | Electroles<br>nickel<br>immersion<br>gold- ENIG | Immersion<br>Silver- IAg |              | Immersion<br>Tin - ISn | Electrolytic<br>nickel<br>gold - NIAu |  |

|---------------------------------|----------------|-----------------------|-------------------------------------------------|--------------------------|--------------|------------------------|---------------------------------------|--|

| RoHS<br>Compliant               | No             | Yes                   | Yes                                             | Yes                      | Yes          | Yes                    | Yes                                   |  |

| Fabrication costs               | Low            | Low                   | Medium                                          | Medium                   | Low          | Medium                 | High                                  |  |

| Shelf life                      | 1 Year         | 1 Year                | 1 Year                                          | 9-12 Months*             | 9-12 Months* | 9-12 Months*           | 1 Year                                |  |

| Assembly cyde<br>capacity       | Multiplie      | Multiplie             | Multiplie                                       | Multiplie                | Multiplie    | Multiplie              | Multiplie                             |  |

| Multiplie<br>rework<br>capacity | Limited        | Limited               | Limited                                         | Yes                      | No           | No                     | No                                    |  |

| Solder<br>wettability           | Excellent      | Good                  | Good                                            | Very Good                | Good         | Good                   | Good                                  |  |

| Co-planarity                    | Poor           | Good                  | Excellent                                       | Excellent                | Excellent    | Excellent              | Good/Poor                             |  |

| Solder joint integrity          | Excellent      | Good                  | Good                                            | Excellent                | Good         | Good                   | Poor**                                |  |

| Low resistanse/<br>high speed   | No             | No                    | No                                              | Yes                      | N/A          | No                     | No                                    |  |

| Aluminium<br>wire bond          | No             | No                    | No                                              | No                       | No           | No                     | Yes                                   |  |

\* Requires unique storage techniques

\*\* Thicker applications of Au can cause embrittlement

Figure 28 - Final Plating Finish Comparisons<sup>[3-6]</sup>

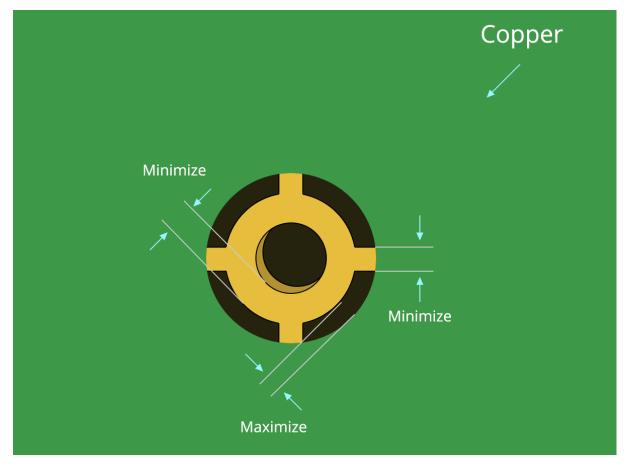

#### **Thermal Relief**

Thermal relief is critical for wave soldering, SMT processing, and hand soldering. This becomes more important on high copper content assemblies and multilayer boards as the copper can turn into a heat sink that draws most of the heat from the soldering areas. This can make it difficult to maintain process temperatures, and the presence of a thermal relief makes it easy to solder through-hole components by slowing the rate of heat sinking through plated through-holes. Not having a heat relief could result in poor hole filling and cold solder joints, and can also impact rework capabilities. Some of the benefits of adding a thermal relief on your board include:

- Better control over hole size.

- More consistency in plating thickness.

- Faster and easier solder joint inspection.

As a general rule, it is recommended to use a thermal relief pattern for any via or hole that is connected to a ground or power plane. It is also recommended to avoid using thermal relief on press fit component holes and consider using the thermal current capacity in your calculations. See Figure 29 for an example of a typical thermal relief pattern on a board layout:

Figure 29 - Typical Thermal Relief Pattern

## Laying the Groundwork

This chapter laid the groundwork for your design process, allowing you to strategize the basics of your board layout including using through-hole or SMT for components, clearly documenting your silkscreen, understanding the importance of solder mask, and finally specifying via sizing and placement. We are now ready to dive into the specific guidelines for component placement and orientation on your board layout to have your PCB successfully manufactured.

# Placing and Orienting Your Components

## Introduction

With your preferred component types established, it is now time to decide how to place efficiently and orient those parts on your board. This process will have a large effect on how you utilize the available space on your board layout, and can be one of those most challenging steps in your design process. Below you will find specific recommendations on how to optimize your component placement to be both manufacturable and capable of meeting your specific design requirements.

## **General Component Placement and Spacing Guidelines**

Before going into the specifics of component placement and orientation, there are several general guidelines to keep in mind:

- For efficient soldering and placement, it is recommended to orient similar components in the same direction.

- Avoid placing components on the solder side of a board that would lay behind components with plated through-holes.

- To minimize the number of processes required to assemble a board, try to place all your SMD components on the same side of the board, and all the through-hole components (if mixed) on the top side of the board.

- When you have mixed technology components (through-hole at the top and SMT on both sides), manufacturers might require an extra process to epoxy the bottom components which will add to your overall manufacturing costs.

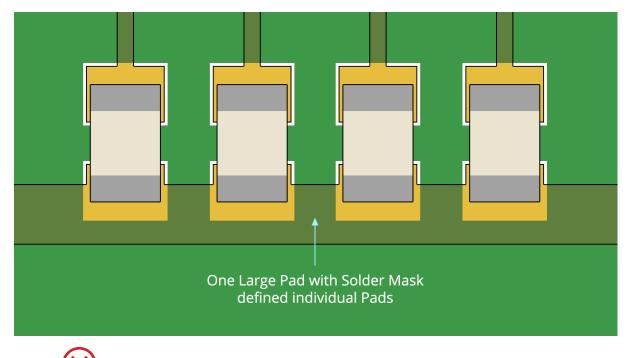

- You should terminate all lands with only one trace, and define your pads with solder mask.

By following the above guidelines alone, you will be well ahead of a typical PCB designer in the efficient utilization of your board layout while also ensuring that your board is manufactured without any delays. The next sections will go into specific component placement, orientation, and termination recommendations.

#### **Specific Component Placement and Board Orientation Guidelines**

Having adequate spacing between your components is critical for proper soldering, performing rework, testing your board, and a smooth assembly process. Poor spacing on components could lead to manual placement due to the inability of a pick-and-place machine to do its job properly.

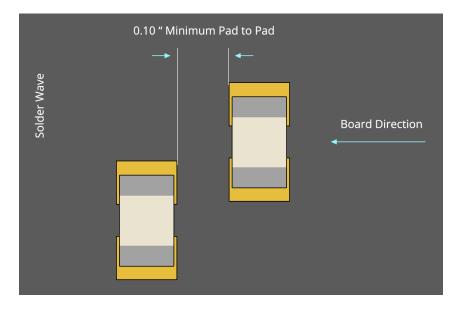

Sometimes you cannot avoid scattering chip components on the bottom of your board. To avoid shadowing and unsoldered termination, it is recommended to have a 0.100" spacing between each component, as shown in Figure 30:

Figure 30 - Component Spacing to Avoid Shadowing and Unsoldered Termination

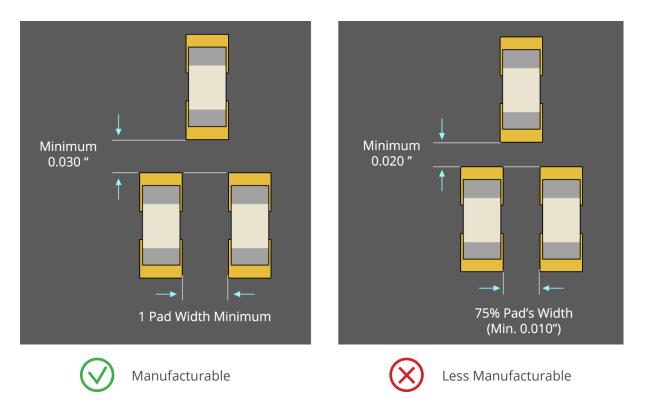

It is recommended that component-to-component spacing be 1x the component height (or a minimum of ½ its height). Figure 31 and b shows the minimum recommended component spacing for some of the most common package types. For a more detailed on component spacing please refer to IPC-7351<sup>[4-1]</sup>.

| Minimum | 50% Pad's width          |

|---------|--------------------------|

| 0.010 " | (Min. 0.010")            |

|         | Difficult Manufacturable |

Figure 31a - Recommended Minimum Spacing Between SMD Components Based on SMT Density

#### Component-to-Component Spacing

| To<br>From | Chip | Tantalum | SOIC | QFP/QFN | SOT23 | PLCC | BGA | CSP | DIP |

|------------|------|----------|------|---------|-------|------|-----|-----|-----|

| Chip       | 40   | 50       | 40   | 100     | 50    | 50   | 125 | 125 | 60  |

| Tantalum   | 50   | 50       | 55   | 100     | 75    | 100  | 125 | 100 | 60  |

| SOIC       | 40   | 55       | 50   | 100     | 50    | 100  | 125 | 125 | 60  |

| QFP/QFN    | 100  | 100      | 100  | 100     | 100   | 100  | 250 | 250 | 100 |

| SOT23      | 50   | 75       | 50   | 100     | 35    | 100  | 125 | 125 | 60  |

| PLCC       | 50   | 100      | 100  | 100     | 100   | 100  | 125 | 125 | 60  |

| BGA        | 125  | 125      | 125  | 250     | 125   | 125  | 250 | 250 | 125 |

| CSP        | 125  | 100      | 125  | 250     | 125   | 125  | 250 | 100 | 125 |

| DIP        | 60   | 60       | 60   | 100     | 60    | 60   | 125 | 125 | 100 |

ALL DIMENTIONS IN MILS

Figure 31b - Standard Clearance Requirements for Component Spacing Based on Type<sup>[4-2]</sup>

NOTE: Sockets (for PLCC and DIP) and connectors should be away from BGA and CSP components to prevent solder joint cracking due to possible stress exerted during second loading/removal of add-on cards or IC components.

(\*) For primary side only. For secondary side 0.125" clearance for all SMT components from DIP pins requiring selective wave solder fixture. Press fit connectors are an exception and do not require this clearance on the secondary side.

(\*\*) Advanced Option if absolutely necessary:

0402 components can be 20 mils apart.

0603 components can be 25 mils apart.

These numbers applies to Viasystems only and requires special setupon their side. Viasystems should be notified before the board is built.

#### **Component and Board Orientation**

It is important to spend time carefully orienting your components as it directly affects your board manufacturability and the reliability of the assembly process. A few variables will determine how your board will be placed and soldered through your manufacturer's assembly equipment, including the tooling holes, connector locations, edge components, and the PCB outline. See Figure 32 for a comparison between board layouts with poorly placed components and those with adequate spacing.

Figure 32a - Clustering Large components Requires High Temp Reflow (can damage Chips)

This board will have to be reflowed at higher temperature which could cause damage to chip components. This due to having large components located in one particular area of the board.

Figure 32b - Spreading Out Large Components for Better Thermal Distribution

For better thermal distribution it's best to spread out large components throughout the board.

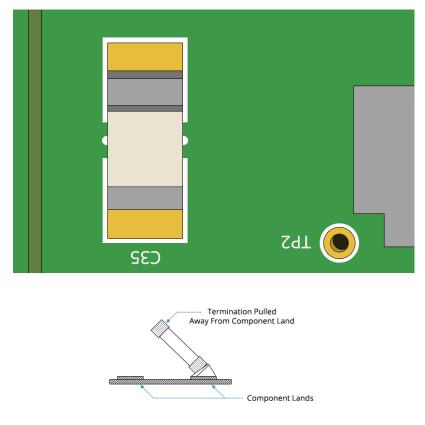

Figure 33: Termination Pulled Away from Component Pad Due to Poor Thermal Balance (Tombstoning)

If your board consists of large components with heights greater than 0.20" it is recommended to make the component-to-component spacing equal to the height of the largest component package. This strategy gives ample room for visual inspection and makes rework easier.

To achieve a better thermal balance of your board during reflow, you should distribute the components as evenly as possible throughout your board. This will ensure that no area on your board will be substantially hotter than another. It is also recommended to avoid concentrating large components in one area of your board to help minimize bow and twist while providing a balanced thermal distribution.

## **Board Orientation for Wave Soldering**

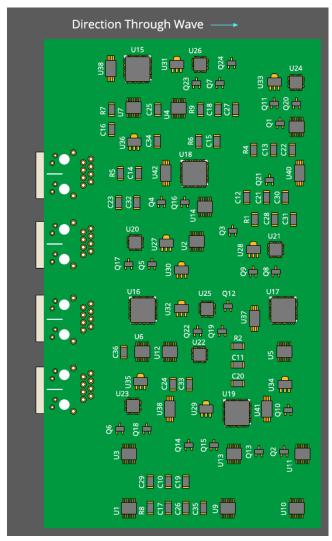

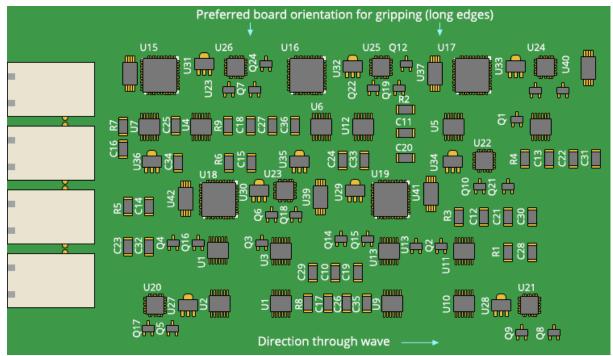

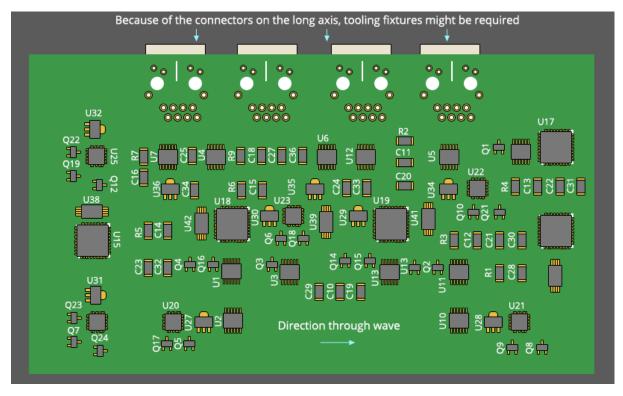

Manufacturers typically prefer a board to be on its long axis when flowing through a soldering machine. This will minimize the setup complexity and prevent a board from bulging downward during soldering. See Figure 34 for an example showing a unpreferred board orientation dictated by the card edge connector, which would interfere with the gripping assembly if rotated to the preferred long axis.

Figure 34 - Unpreferred Board-to-Solder Orientation

## **Component Orientation**

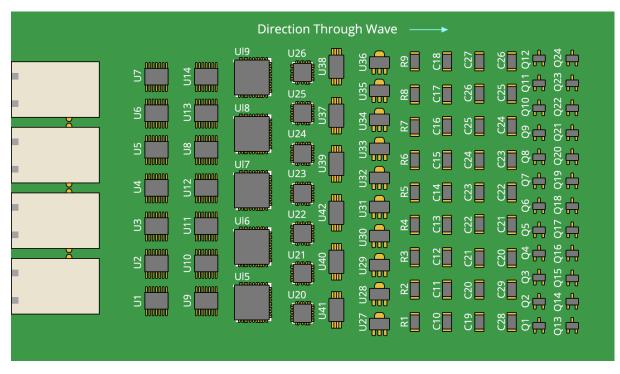

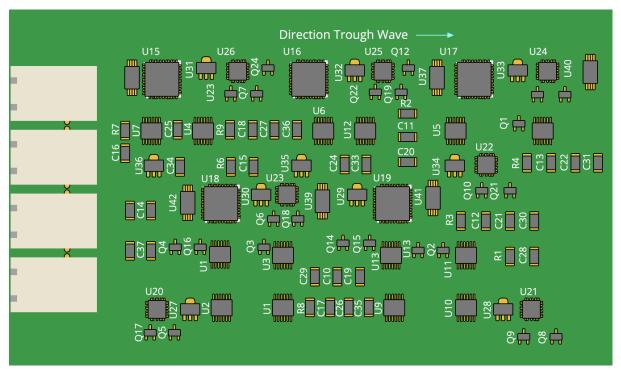

The geographic location of a component on a PCB is important for proper board manufacturability. It is recommended to orient your components relative to your board outline and the solder process on the long axis of the PCB, where your small outline ICs (SOIC) are set in parallel to the solder flow direction as shown in Figures 35 a and b.

Figure 35a: Board in This Orientation (Top & Bottom) is Soldered in the Long Axis (Preferred Orientation)

Figure 35b: Bottom Side Component Orientation for Wave Solder (Non-Preferred)

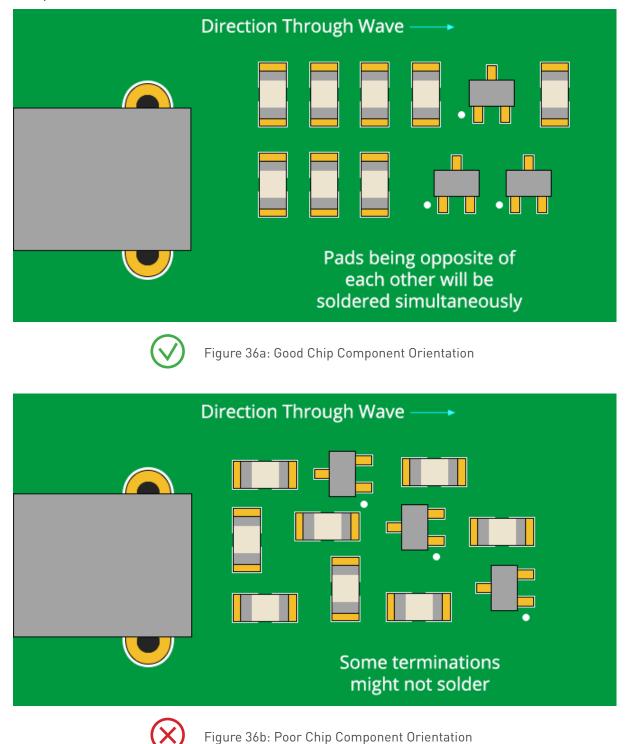

For chip components, both terminations should be parallel to the solder wave so they can be soldered at the same time. Avoid shadowing by not placing chip components perpendicular to each other. This will also help to avoid uneven solder fillets (and skips) that usually put stress on solder joints. Figure 36 shows a visual example of correct chip component orientation.

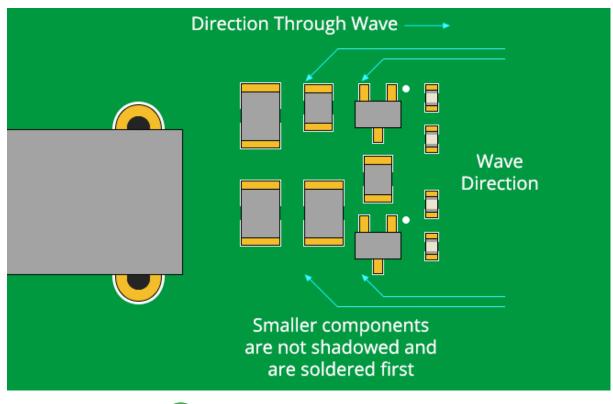

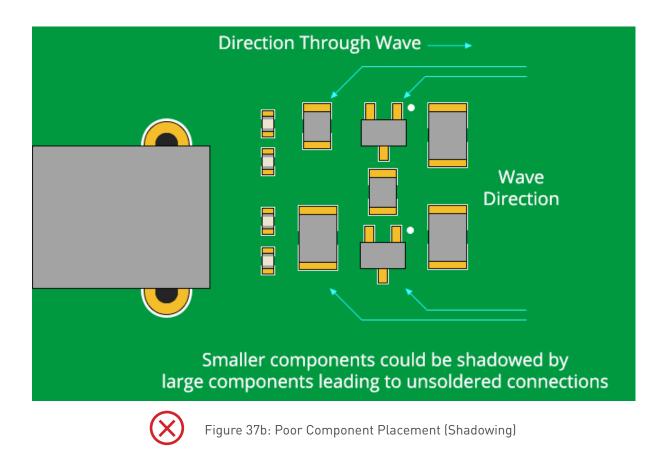

The more shadowing of smaller components you have on your board from the solder wave, the more likely your PCB will end up with open solder joints. Ensure that the soldering direction of your board is positioned in a way that large components will not shadow the smaller chip components as shown in Figure 37 below.

Figure 37a: Good Component Placement

## **BGA** Orientation

It is recommended to place BGAs on the top of the board to eliminate the possibility of open solder connections during the second pass reflow. Your manufacturer might require additional steps in the assembly process if you have BGA components on both sides of your board.

These additional steps will ensure a temporary support to the other side of a BGA during the second pass reflow process.

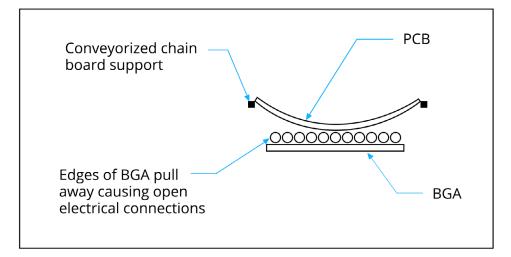

Avoid placing BGA and larger quad flat package (QFP) components in the center of the PCB to prevent board warpage caused by heavier parts. Not following this guideline can result in open solder connections as shown in Figure 38, and is a concern for standard 0.062" boards when the board area is greater than 25 square inches.

Figure 38 - Example of the Bow-and-Twist Effect on BGA Devices

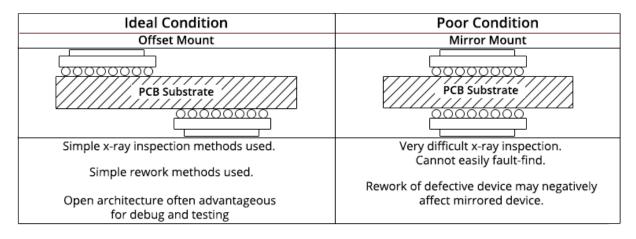

If your design has BGA components on both sides of the board, it is recommended to offset each BGA to ease rework and facilitate the solder ball inspection as shown in Figure 39.

## **Chip Under Device Placement**

When you specify a chip under a device, this can make inspections, rework, and test more difficult. If placed under BGA sockets or ZIF sockets, you will need to account for the BGA ball collapse, which is typically around 25% of the ball diameter. It is recommended to keep the stackup tolerances in mind with these type of designs as they make it impossible to inspect hidden devices and make it challenging to perform rework.

# **Resistor Pack (R-Pack) Placement Limitations**

Resistor packs with convex-type termination and external solder joints are preferred by PCB manufacturers. These types of resistor packs have better spacing and easier termination soldering, which makes the visual checking and inspection of the solder joints easier.

# **Capacitor Placement**

To keep your design consistent and assist with the assembly process, it is recommended to place all polarized capacitors in an orientation where the positive end is to the right or down. As you saw earlier, the polarity should be indicated on the silkscreen on the package outline. Decoupling capacitors should always be placed as close as you can get to them to the IC's power pin and oriented perpendicular to SOIC components and the solder flow.

## **Double-Sided Boards**

The spacing between pads (land-to-land) that are perpendicular and parallel to the solder direction should be at least 0.025" to avoid solder bridging. It is also recommended to maintain a minimum of 0.025" spacing from a through-hole pad or via edge to a surface mount pad or another via.

#### **Components and Wave Soldering**

All components used on the wave solder sides of an assembly should first be approved by your manufacturer for immersion in a solder bath. For tall components (taller than 0.0100") such as tantalum capacitors, it is recommended to have at least 0.100" land-toland clearance (from all directions) to avoid skips and open connections during the wave solder operation.

Some types of components are sensitive to wave soldering at higher temperatures, and it is not recommended to place them on the backside of your board (bottom layer) where the solder wave would contact the component. Components that are not recommended for placement on the backside of a board (bottom layer) include:

- BGA components.

- Non-encapsulated inductors.

- QFP components.

- "J" leaded devices.

- Connectors.

- Any other device that cannot be submerged in solder.

## **Through-hole Components**

When determining your required PTH finished size, keep in mind that if the PTH is too large, the component will not stay in place and could misalign, increasing the "lift" probability and creating shorts due to solder flooding during wave soldering. If the PTH is too small, the component might not fit in the PTH and could result in insufficient solder fill. It is easy to disorient a through-hole component, so directional packages are preferred over bi-directional ones. Figure 40 gives a general set of guidelines to determine PTH finished sizes:

|                |               |         |                                                     | More<br>Manufacturable                            |                                                   | Less Manufacturable                               |                                                                              |

|----------------|---------------|---------|-----------------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------|

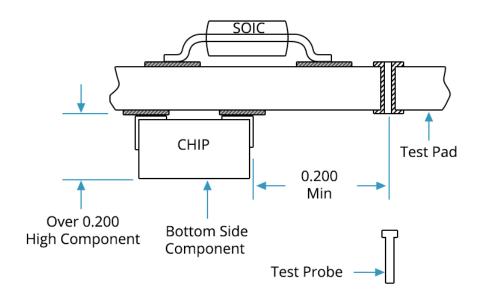

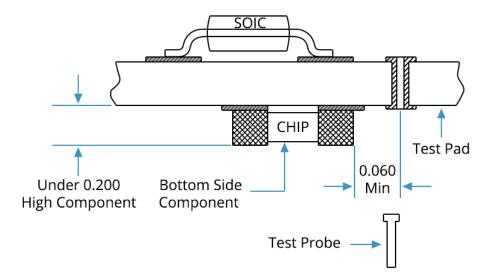

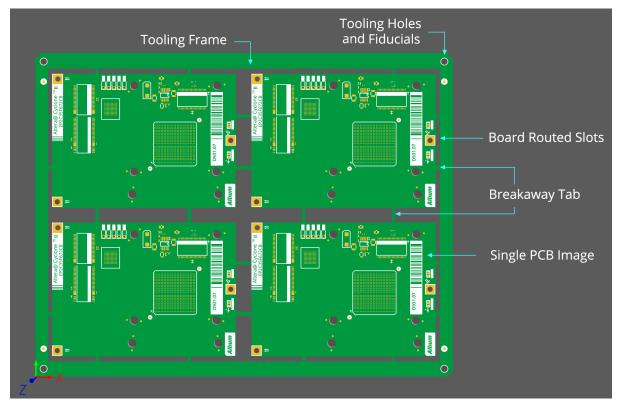

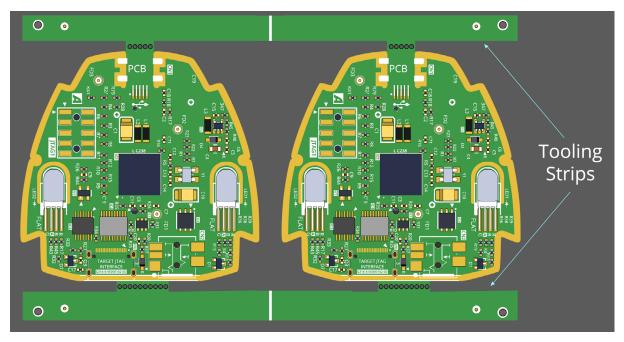

| _              |               |         |                                                     | Lead Clearance                                    | Lead Clearance                                    | Lead Clearance                                    | Lead Fee                                                                     |