Concevoir du matériel électronique en période de pénurie de mémoire : guide pratique pour les ingénieurs et les équipes achats

Dans la première partie de cette série, How AI Broke the Memory Market, nous avons vu comment la demande des centres de données IA a transformé la mémoire en goulet d’étranglement, et pourquoi les prix de la DRAM et de la NAND ont peu de chances de se normaliser rapidement. Nous allons maintenant voir comment opérer dans cet environnement. Si vous concevez ou approvisionnez du matériel en 2026, vous devez toujours faire des choix : quelles références spécifier, comment structurer vos conceptions pour plus de flexibilité, et comment gérer le risque lié à la chaîne d’approvisionnement.

Nous aborderons les composants mémoire de « nouvelle vague » en préparation, puis nous passerons à certains composants DRAM et flash de référence. À partir de là, nous présenterons des guides pratiques à la fois pour l’ingénierie et les achats.

Pour une vue d’ensemble des composants mémoire, les pages de catégorie d’Octopart consacrées aux circuits intégrés mémoire et à la mémoire flash constituent de bons points de départ pour effectuer des recherches parmi les fabricants, les boîtiers et les disponibilités.

Points clés à retenir

- Sachez distinguer ce qui arrive de ce qui est disponible. Les composants de nouvelle génération comme la LPDDR6 et la HBM4 indiquent la direction prise par les plateformes, mais vos conceptions de 2026 seront livrées avec de la DDR5, de la LPDDR5X et de la NAND mature disponibles en stock aujourd’hui.

- Concevez pour la substitution et la flexibilité. Standardisez sur des interfaces grand public, qualifiez des familles de composants et prenez en charge plusieurs densités dans le firmware. Utilisez des sockets et des modules lorsque c’est possible, et prévoyez des options de mémoire déclassée qui répondent malgré tout aux objectifs d’expérience utilisateur.

- Abordez le risque d’approvisionnement comme un problème d’ingénierie. Constituez des listes de fournisseurs approuvés multisources, sécurisez des allocations pour les lignes critiques et suivez le cycle de vie ainsi que les alternatives avec des outils comme Octopart.

Composants de nouvelle génération qui donnent la direction

DRAM mobile LPDDR6 de Samsung

Conçue pour l’IA embarquée, l’automobile et les plateformes mobiles et PC de nouvelle génération, la LPDDR6 de Samsung offre des gains d’efficacité significatifs par rapport à la LPDDR5X, une architecture d’E/S étendue et une vitesse initiale allant jusqu’à 10,7 Gbit/s, la norme LPDDR6 étant conçue pour évoluer davantage à mesure que l’écosystème mûrit. Vous ne verrez pas encore de LPDDR6 dans les rayons des distributeurs, mais si vous concevez autour de SoC de pointe ou d’appareils haut de gamme, vous devez vous attendre à y être confronté.

HBM4

Au sommet de la pile, les dispositifs HBM4 16 couches de 48 Go de SK Hynix promettent plus de 2 To/s de bande passante, avec une production de masse visée autour du troisième trimestre 2026. Samsung adopte une approche différente, en utilisant une logique en 4 nm et de la DRAM 1c pour améliorer les performances thermiques. Les ingénieurs travaillant sur du matériel IA ne s’approvisionneront généralement pas en ces composants auprès de distributeurs sur catalogue, mais la HBM4 concerne tout le monde, car elle absorbe une grande part de la capacité DRAM avancée, ce qui explique en partie pourquoi la DRAM conventionnelle reste sous tension.

V-NAND de 10e génération de Samsung

Avec plus de 400 couches et une interface à 5,6 GT/s, la V-NAND de 10e génération de Samsung vise les SSD PCIe 5.0 et les futurs SSD PCIe 6.0 pour les charges de travail de centres de données et de classe IA. Il faut s’attendre à ce que la TLC haute densité basée sur ce silicium serve de fondation à de nombreux disques d’entreprise et clients haut de gamme au cours des prochaines années.

NAND BiCS10 de Kioxia/Sandisk

Cette BiCS10 à 332 couches avec interface Toggle DDR 6.0 délivre 4,8 Gbit/s par broche et cible le stockage IA et hyperscale. Selon EE Times, Kioxia a indiqué que l’ensemble de sa production NAND 2026 était déjà vendu à des applications liées à l’IA, et a avancé la montée en cadence de sa BiCS10 du second semestre 2027 à 2026 pour répondre à la demande.

Produits mémoire de référence moins contraints

Ces composants étaient disponibles à la commande auprès des principaux distributeurs début mars 2026. La disponibilité évolue rapidement ; vérifiez donc le stock et le statut de cycle de vie sur Octopart avant de figer une nomenclature.

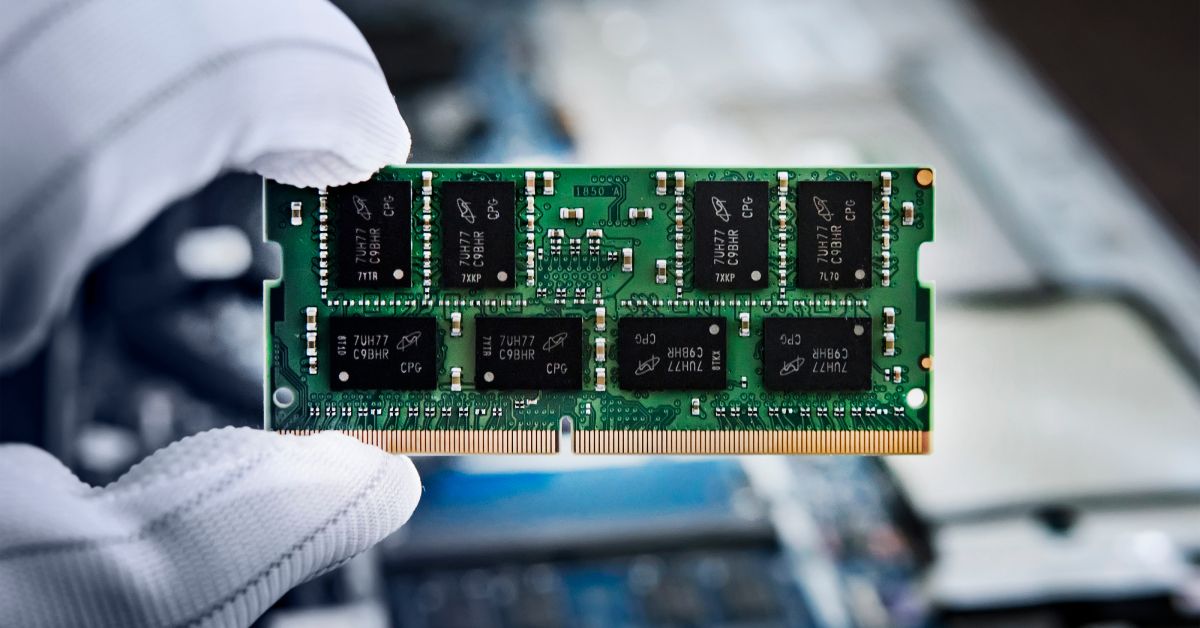

- Apacer D22.31491S.001, SO-DIMM DDR5-4800 de 8 Go. Une option DRAM pratique à « liaison tardive » pour les conceptions pouvant utiliser un module sur socket, ce qui donne plus de marge de manœuvre aux achats lors des substitutions.

- MT60B2G8RZ-56B IT:D, SDRAM DDR5 de 16 Gbit (2G x 8), VFBGA à 78 billes. Un circuit DRAM DDR5 x8 de classe DDR5-5600 grand public qui convient aux conceptions mémoire personnalisées au niveau carte et offre une flexibilité de second sourcing plus réaliste qu’une référence de module unique.

- Macronix MX30LF4G28AD-XKI-TR, NAND SLC de 4 Gbit (VFBGA-63). Un bon choix pour les conceptions NAND industrielles et embarquées qui exigent endurance et comportement prévisible dans une empreinte BGA compacte.

- Macronix MX60LF8G28AD-TI-T, NAND SLC de 8 Gbit (TSOP-48). Un choix pratique lorsqu’il faut une empreinte NAND parallèle largement prise en charge pour des écosystèmes de contrôleurs matures et une reprise carte plus simple qu’avec des BGA à pas fin.

- Macronix MX52LM04A11XSI, eMMC 5.1 de 4 Go (BGA-153). Une option NAND gérée simple lorsque vous souhaitez moins de dépendances au contrôleur et une substitution plus propre qu’avec de la NAND brute associée à une pile flash personnalisée.

- Macronix MX52LM08A11XVW, eMMC 5.1 de 8 Go (BGA-153). Un niveau de capacité pratique pour de nombreux systèmes Linux embarqués et systèmes de type IHM, avec les mêmes avantages d’interface et d’intégration que les composants eMMC de plus faible capacité.

- Micron MT40A2G8SA-062E:F, DRAM DDR4 de 16 Gbit (2G x 8). Toujours un composant de référence à fort volume pour de nombreuses plateformes et une option pragmatique « expédier maintenant » lorsque la DDR5 n’est pas requise.

Guide de conception : comment les ingénieurs intègrent la flexibilité

Dans ce contexte, les ingénieurs matériel disposent encore de nombreuses actions pour rendre leurs conceptions plus résilientes.

- Standardisez sur des interfaces et des familles grand public. La DDR5, la LPDDR5X, l’e.MMC, l’UFS et la flash SPI/QSPI disposent d’écosystèmes riches et de nombreuses secondes sources. Rester dans des tensions et des boîtiers courants maximise le vivier de composants compatibles.

- Intégrez de la flexibilité dans le firmware et les cartes mémoire. Évitez de coder en dur une seule densité DRAM ou une seule taille de flash SPI. Prenez en charge plusieurs géométries dans votre code d’initialisation afin de pouvoir remplacer les alternatives.

- Privilégiez la mémoire non volatile gérée lorsque cela convient. L’e.MMC et l’UFS masquent les détails de gestion de la NAND derrière des interfaces stables et offrent souvent des voies de substitution plus claires que la NAND brute liée à un contrôleur spécifique.

- Prévoyez des variantes déclassées. Concevez votre logiciel de sorte que des configurations mémoire plus faibles offrent malgré tout une expérience utilisateur acceptable, par exemple en utilisant une concurrence par défaut plus faible, des ensembles de ressources plus petits ou une hiérarchisation des fonctionnalités.

- Utilisez une mémoire et un stockage modulaires lorsque c’est possible. Les sockets pour SO-DIMM, UDIMM et SSD M.2 permettent une configuration tardive et donnent plus de levier aux achats. Réservez la mémoire soudée aux formats contraints où elle est réellement nécessaire.

Guide d’approvisionnement : comment les achats peuvent gérer le risque

La situation exige toute votre attention. Fin février 2026, Lenovo a averti ses partenaires de distribution de passer commande avant la fin du mois pour éviter les hausses de prix de mars, tandis que TrendForce prévoyait que la DRAM PC mixte (DDR4/DDR5) augmenterait de 105 à 110 % d’un trimestre à l’autre rien qu’au T1. Le guide ci-dessous reflète cette nouvelle réalité.

- Sécurisez des allocations et des accords à long terme pour les lignes critiques de DRAM et de NAND, en particulier pour les serveurs, les boîtiers IA et les ordinateurs portables haut de gamme. Les informations de marché fournies par des sociétés comme TrendForce peuvent aider à déterminer quand s’engager.

- Construisez des listes de fournisseurs approuvés autour de familles, et non de références individuelles. Définissez des classes acceptables de modules, de NAND et d’e.MMC, et travaillez avec l’ingénierie pour valider plusieurs options en amont.

- Segmentez les produits selon leur sensibilité à la mémoire. Réservez la mémoire rare et coûteuse aux références pour lesquelles elle a le plus d’impact sur les performances et la marge ; appliquez des contrôles de coûts plus agressifs aux appareils moins sensibles à la mémoire.

- Utilisez le stock de mémoire comme couverture stratégique pour les produits à long cycle de vie. Conserver un tampon de DRAM ou de NAND clés peut coûter moins cher que de reconcevoir des cartes ou de réécrire le firmware en cours de vie si un composant devient contraint.

La flexibilité est la stratégie

Dans la première partie de cette série, nous avons expliqué les causes de la crise de la mémoire. Ici, nous avons exploré ce qu’il faut faire maintenant. La réponse est la même, que vous soyez ingénieur ou du côté des achats : la flexibilité est la meilleure couverture. Concevez pour la substitution, qualifiez largement et utilisez des outils comme Octopart pour garder vos options visibles et à jour. Les équipes qui traverseront ce cycle dans les meilleures conditions seront celles qui auront intégré très tôt de l’optionalité dans leurs conceptions et leurs chaînes d’approvisionnement, et qui continueront à s’adapter à mesure que l’offre et les prix évoluent.

Questions fréquentes

Pourquoi la DRAM et la NAND restent-elles difficiles à approvisionner en 2026 ?

La pénurie actuelle est due à l’allocation des wafers, et non à des limites technologiques. Les fournisseurs de mémoire privilégient la demande IA à forte marge, en particulier la HBM et la DRAM pour centres de données, dans le cadre de contrats pluriannuels. Comme la HBM consomme nettement plus de capacité wafer par bit que la DRAM conventionnelle, il reste moins de capacité pour la DDR5, la LPDDR et la NAND, ce qui maintient une disponibilité tendue.

Les ingénieurs doivent-ils concevoir dès aujourd’hui avec de la mémoire de nouvelle génération comme la LPDDR6 ou la HBM4 ?

La LPDDR6 et la HBM4 indiquent la direction prise par les plateformes, mais la plupart des produits de 2026 seront livrés avec de la DDR5, de la LPDDR5X et de la NAND mature disponibles dès maintenant. Les ingénieurs doivent concevoir en gardant à l’esprit la compatibilité future, tout en sélectionnant des composants pouvant être approvisionnés de manière fiable pendant la production, plutôt que de miser sur des composants qui ne sont pas encore distribués.

Comment rendre les conceptions matérielles plus résilientes face aux pénuries de mémoire ?

Les conceptions résilientes misent sur la flexibilité et la substitution. Cela inclut la standardisation sur des interfaces grand public, la qualification de plusieurs densités et fournisseurs, l’évitement des hypothèses mémoire codées en dur dans le firmware, et l’utilisation de sockets ou de modules lorsque c’est possible. La prise en charge d’options mémoire déclassées garantit que les produits peuvent toujours être livrés lorsque les composants de plus forte capacité sont contraints.

Quelle est la meilleure façon pour les équipes achats de gérer le risque d’approvisionnement en mémoire ?

Les achats doivent considérer la mémoire comme une ressource stratégique, et non comme une commodité. Parmi les bonnes pratiques figurent la sécurisation d’allocations à long terme pour les références critiques, la constitution d’AVL autour de familles de composants plutôt que de pièces uniques, la surveillance du cycle de vie et des alternatives à l’aide d’outils comme Octopart, ainsi que le stockage ciblé de stocks pour les produits à long cycle de vie afin d’éviter des reconceptions forcées.