Comment l’IA a bouleversé le marché de la mémoire : plongée au cœur de la pénurie de DRAM et de NAND de 2024 à 2026

Points clés

- Les centres de données IA sont devenus les principaux clients des fabricants de mémoire, entraînant des changements dans l’allocation des wafers entre la DRAM, la HBM et la NAND simultanément.

- Ce cycle offre-demande est différent. L’expansion limitée des fabs, une production NAND en grande partie déjà vendue, et des contrats HBM pluriannuels signifient que la pénurie persistera probablement jusqu’à fin 2027–2028.

- Les conceptions legacy et embarquées en subissent les dommages collatéraux. La DDR3, les premières générations de DDR4 et la NAND SLC font face à un risque croissant de fin de vie (EOL), à des délais d’approvisionnement plus longs et à des prix imprévisibles, les fournisseurs privilégiant la mémoire IA à forte marge.

Le retournement de situation de la mémoire : d’élément secondaire à goulet d’étranglement

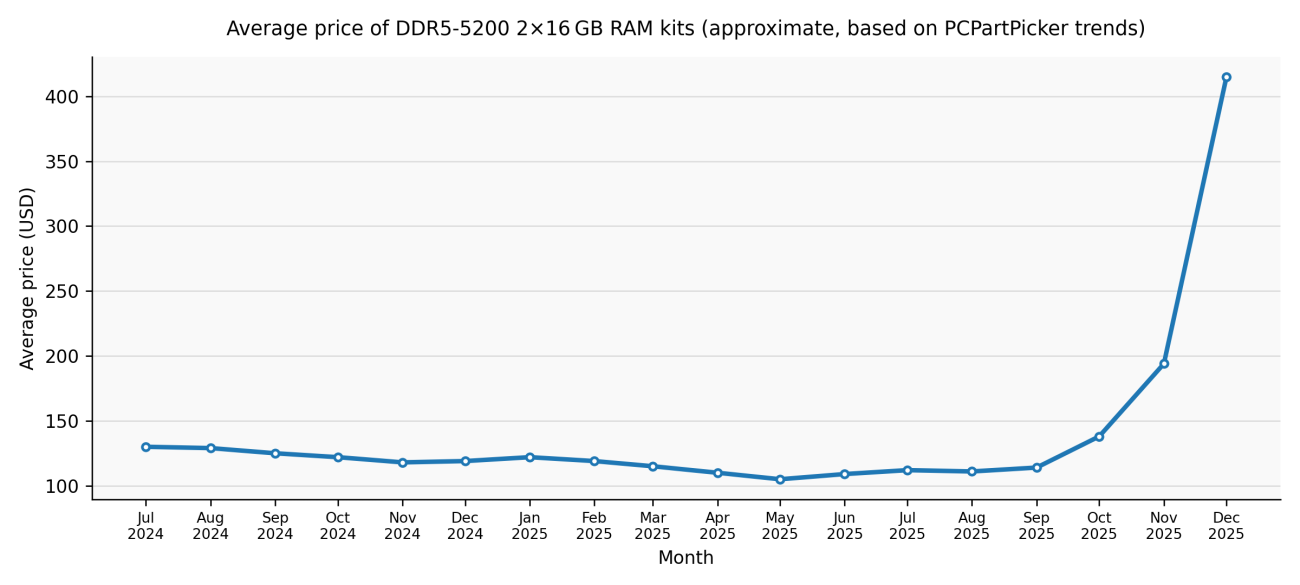

Pendant la majeure partie de l’ère du PC, la mémoire restait en arrière-plan. Entre 2024 et 2026, cette dynamique s’est inversée. La mémoire est devenue la contrainte principale dans la conception des systèmes, et le coût du « simple ajout de RAM » a fortement augmenté en seulement quelques trimestres.

Les prix ont grimpé, la disponibilité s’est resserrée, et les produits sont de plus en plus livrés avec le strict minimum de mémoire plutôt qu’avec la marge confortable à laquelle nous étions habitués. Un rééquilibrage structurel est en cours quant à l’attribution des wafers et aux raisons de cette attribution.

Alors, qu’est-ce qui a réellement changé, et pourquoi cette pénurie semble-t-elle différente des précédentes ? Nous allons l’examiner ici, dans le premier volet d’une série en deux parties consacrée aux forces qui perturbent l’approvisionnement en mémoire, des serveurs cloud jusqu’aux systèmes embarqués. La deuxième partie, Concevoir du matériel dans un contexte de pénurie de mémoire, approfondit le sujet avec une analyse détaillée des composants mémoire de nouvelle génération qui arrivent tout juste sur le marché, des principaux produits de référence que vous pouvez commander dès aujourd’hui auprès de votre distributeur, ainsi que des modèles de conception et des tactiques d’approvisionnement.

Comment les centres de données IA redessinent le paysage de la demande

Lors des cycles précédents, la demande en mémoire était largement répartie entre les PC, les téléphones, les serveurs et l’électronique grand public. L’offre et la demande se désalignaient progressivement, les prix montaient ou baissaient fortement, puis la situation se normalisait à mesure que les fabs s’ajustaient. La pénurie de 2024–2026 ne suit pas ce scénario.

La différence tient à l’identité des acheteurs. Les centres de données orientés IA dominent désormais la demande, et leurs clusters d’entraînement ainsi que leurs fermes d’inférence nécessitent d’énormes quantités de mémoire à large bande passante (HBM) et de DRAM conventionnelle par GPU ou accélérateur. La HBM consomme nettement plus de capacité wafer par bit que la DRAM standard, ce qui la rend extrêmement attractive pour les fabricants cherchant à sécuriser des contrats pluriannuels à forte marge avec les fournisseurs d’infrastructure IA.

Certains analystes estiment désormais que les centres de données consommeront jusqu’à 70 % de toutes les puces mémoire haut de gamme produites en 2026, un renversement marqué par rapport à l’époque où les appareils grand public représentaient la majorité de ces puces. Dans cet environnement, la mémoire pour PC et mobiles devient une activité secondaire, tandis que les centres de données IA deviennent l’enjeu principal.

La génération HBM4 dévoilée au CES 2026 illustre l’ampleur de ce basculement. SK Hynix a présenté un composant 16 couches de 48 Go offrant plus de 2 To/s, augmentant significativement les performances des premières HBM3 utilisées dans la première vague d’accélérateurs d’IA générative. Chaque wafer consacré à ces empilements n’est pas utilisé pour fabriquer de la DDR5 pour votre prochain PC ni de la LPDDR5X pour un téléphone.

Conceptions embarquées et legacy : prises en étau

Les conceptions embarquées et industrielles, qui reposent souvent sur d’anciennes normes DRAM ou sur de la NAND SLC mature, font face à leurs propres vents contraires. Beaucoup de ces produits utilisent de la DDR3 ou des premières DDR4, ainsi que de la mémoire flash NAND parallèle, qui ne sont plus au cœur des feuilles de route des fournisseurs.

À mesure que les fabricants privilégient la HBM à forte marge et la DRAM de classe serveur, ils réduisent ou arrêtent les lignes legacy. Ce qui reste affiche des prix étonnamment élevés et des délais plus longs, même si la technologie elle-même est mature.

Surveiller de près le statut du cycle de vie des composants avec des outils comme Octopart aide les équipes à repérer les annonces d’EOL et les tensions d’approvisionnement avant qu’elles ne deviennent critiques.

Des progrès sous pression : DDR5, LPDDR6, NAND et HBM4

Les mêmes transitions technologiques qui privent les anciennes conceptions d’approvisionnement produisent aussi de véritables avancées d’ingénierie. Comprendre les deux faces de cette dynamique est important, car les progrès modifient ce qu’il est possible de concevoir, tandis que les aspects économiques liés aux wafers expliquent pourquoi la mémoire de commodité ne deviendra pas moins chère de sitôt.

DRAM

Samsung produit en volume la DRAM LPDDR5X la plus fine de sa catégorie 12 nm pour les appareils mobiles de nouvelle génération, en combinant hautes performances, efficacité énergétique et boîtier fin adapté aux smartphones premium et aux ultraportables. Les premiers composants LPDDR6 poussent encore plus loin la bande passante et l’efficacité énergétique, en ciblant l’IA embarquée et les applications automobiles. L’implémentation LPDDR6 de Samsung gagne en reconnaissance lors des événements du secteur, signalant la direction prise par la mémoire mobile haut de gamme.

HBM

À l’extrémité HBM du spectre, la couverture du CES 2026 sur la HBM4 montre que les empilements mémoire deviennent des sous-systèmes hautement intégrés. Les empilements 16 couches de SK Hynix utilisent le MR-MUF et des wafers DRAM ultra-fins pour rester dans les limites de hauteur JEDEC, tandis que Samsung se tourne vers sa logique en 4 nm (qui est entrée en production de masse en février 2026) pour améliorer les performances thermiques et l’efficacité énergétique. Tous ces efforts d’ingénierie et cette capacité wafer visent directement les accélérateurs IA.

NAND

Du côté de la NAND, les fournisseurs empilent toujours plus de couches. La V-NAND de 10e génération avec plus de 400 couches et des interfaces autour de 5,6 GT/s est intégrée dans des SSD PCIe 5.0 et futurs PCIe 6.0 pour les cas d’usage des centres de données et de l’IA. La BiCS NAND 332 couches de 10e génération de Kioxia et Sandisk, utilisant l’interface Toggle DDR 6.0 jusqu’à 4,8 Gb/s par broche, montre à quel point la NAND à haute bande passante a progressé pour les SSD de centres de données et de classe entreprise.

La technologie progresse, mais la capacité ne suit pas. Selon EE Times, Samsung et SK Hynix ont réduit la production de wafers NAND en 2024–2025 pour se concentrer sur la HBM et la DRAM, et n’ont annoncé aucune nouvelle capacité NAND bien qu’ils contrôlent plus de la moitié du marché. Les données d’Omdia montrent que les wafers NAND de Samsung sont passés de 4,9 millions (2024) à 4,68 millions (2025), et ceux de SK Hynix de 1,9 million à 1,7 million.

Dans le même temps, la NAND est devenue essentielle à l’inférence IA. À mesure que l’IA passe de l’entraînement au service des modèles, les SSD reposant sur de la NAND à grand nombre de couches deviennent de plus en plus le principal stockage des poids de modèles et des données de travail. La direction de Kioxia a indiqué que l’ensemble de sa production NAND 2026 est déjà vendu, que la BiCS10 est avancée du second semestre 2027 à 2026, et qu’à l’avenir, près de la moitié de sa demande NAND pourrait provenir d’applications IA. Les spécialistes de la NAND comme Kioxia et l’activité Sandisk redevenue indépendante, autrefois considérés comme des outsiders sur un marché banalisé, se retrouvent soudainement en position de gagnants du boom des SSD pour l’IA.

Pourquoi la reprise habituelle ne viendra pas

Les analystes du secteur soulignent une croissance relativement modeste de l’offre de DRAM et de NAND jusqu’en 2026 par rapport aux normes historiques. Pendant ce temps, la demande ne faiblit pas. Les nouvelles architectures de modèles, les charges de travail d’inférence et les déploiements d’IA en périphérie continuent de faire grimper les besoins en mémoire au lieu de les laisser se stabiliser. Les fournisseurs de HBM4 consacrent une part importante de leur capacité wafer aux besoins de Nvidia et d’autres accélérateurs, et comme nous l’avons mentionné dans la section précédente, des fournisseurs NAND comme Kioxia affichent complet pour 2026.

En décembre 2025, Micron a illustré la nature structurelle de ce basculement en annonçant son retrait de son activité grand public Crucial afin de mieux servir des « clients stratégiques plus importants ». Certains fournisseurs, dont Micron, ont déclaré publiquement qu’ils ne s’attendent pas à un assouplissement significatif de la pénurie de RAM pour les consommateurs avant 2028 environ, date à laquelle les nouvelles capacités et les transitions de procédés devraient atteindre leur pleine montée en cadence. La même logique s’applique de plus en plus à la NAND : l’inférence IA verrouille l’offre future de SSD presque aussi vite que les fournisseurs peuvent la mettre en ligne.

En décembre 2025, IDC a qualifié la pénurie de « non seulement cyclique, mais potentiellement d’une réallocation permanente et stratégique de la capacité mondiale en wafers de silicium ». En février 2026, TrendForce a fortement révisé à la hausse sa prévision de prix contractuels de la DRAM conventionnelle pour le T1 2026, passant d’une estimation précédente de 55–60 % à 90–95 % d’un trimestre sur l’autre. Dans ce total, la DRAM PC (mélange DDR4/DDR5) devait augmenter de 105–110 % en glissement trimestriel, un nouveau record trimestriel.

Et ensuite : passer de la compréhension à l’action

Dans Concevoir du matériel dans un contexte de pénurie de mémoire, nous examinons sept composants mémoire de nouvelle vague en montée en puissance dans les conceptions OEM et de centres de données, huit produits DRAM et flash de référence facilement disponibles auprès des grands distributeurs, ainsi que des guides pratiques concrets pour travailler dans ces contraintes.

Questions fréquentes

Pourquoi y a-t-il une pénurie de mémoire alors que les technologies DRAM et NAND continuent de s’améliorer ?

La pénurie actuelle n’est pas due à des limites technologiques, mais à l’économie de l’allocation des wafers. Une part croissante de la capacité mondiale de wafers mémoire est redirigée vers la mémoire IA à forte marge, en particulier la HBM pour les accélérateurs de centres de données. Comme la HBM consomme nettement plus de surface wafer par bit exploitable que la DRAM conventionnelle, chaque wafer affecté à la production de HBM réduit la production de DDR4, DDR5, LPDDR et NAND. Avec une expansion limitée des nouvelles fabs et des contrats d’approvisionnement IA à long terme qui verrouillent la capacité, les améliorations de densité mémoire ne se traduisent pas par une disponibilité accrue pour les marchés grand public ou embarqués.

Pourquoi cette pénurie de mémoire semble-t-elle différente des cycles précédents ?

Contrairement aux précédents cycles d’expansion et de repli, cette pénurie est façonnée par une concentration structurelle de la demande plutôt que par une surconsommation temporaire. Les charges de travail d’entraînement et d’inférence IA continuent d’augmenter les besoins en mémoire, tandis que les fournisseurs ont délibérément limité la croissance des capacités. Les contrats HBM pluriannuels, une production NAND 2026 déjà entièrement vendue, et les indications explicites des fournisseurs selon lesquelles aucun soulagement n’est attendu avant 2027–2028 signifient qu’il s’agit d’une réallocation de longue durée, et non d’un déséquilibre de court terme qui se corrigerait de lui-même par les seuls prix.

Quels risques cela crée-t-il pour les conceptions embarquées et héritées utilisant la DDR3, les premières générations de DDR4 ou la NAND SLC ?

Les produits mémoire hérités sont de plus en plus considérés comme non stratégiques par les principaux fournisseurs. À mesure que les fabricants privilégient la DRAM avancée et la HBM, les nœuds de procédé plus anciens voient leurs volumes de production diminuer, les quantités minimales de commande augmenter, les délais d’approvisionnement s’allonger et le risque de fin de vie (EOL) s’accroître. Même lorsque les composants restent techniquement « en production », les prix deviennent volatils et la disponibilité imprévisible. Pour les équipes embarquées, cela renforce l’importance du suivi du cycle de vie, du multi-sourcing et de la planification des refontes bien plus tôt dans le cycle de vie du produit que lors des générations précédentes.

Quand les ingénieurs doivent-ils s’attendre à une normalisation des prix et de la disponibilité de la mémoire ?

D’après les déclarations des fournisseurs et les prévisions des analystes, un soulagement significatif est peu probable avant fin 2027 ou 2028. De nouvelles capacités de production, des transitions de procédé et l’extension des lignes de packaging pour la HBM et la NAND avancée sont prévues, mais leur mise en service prendra plusieurs années. Dans le même temps, les charges de travail d’inférence IA accroissent la demande à la fois pour la DRAM et pour la NAND de classe SSD, absorbant une grande partie de cette capacité future. Les ingénieurs doivent concevoir en partant du principe que la mémoire restera un coût système contraint et à fort impact pendant le reste de cette décennie.