Come l’IA ha sconvolto il mercato della memoria: dentro la stretta su DRAM e NAND del 2024–2026

Punti chiave

- I data center per l’AI sono diventati il principale cliente del silicio per memorie, determinando cambiamenti nell’allocazione dei wafer tra DRAM, HBM e NAND contemporaneamente.

- Questo ciclo domanda-offerta è diverso. L’espansione limitata delle fab, la produzione NAND in gran parte già esaurita e i contratti pluriennali per HBM significano che la carenza probabilmente persisterà fino alla fine del 2027–2028.

- I progetti legacy ed embedded sono danni collaterali. DDR3, le prime DDR4 e la NAND SLC affrontano un rischio EOL crescente, tempi di consegna più lunghi e prezzi imprevedibili, mentre i fornitori danno priorità alla memoria AI ad alto margine.

Il colpo di scena della memoria: da componente di contorno a collo di bottiglia

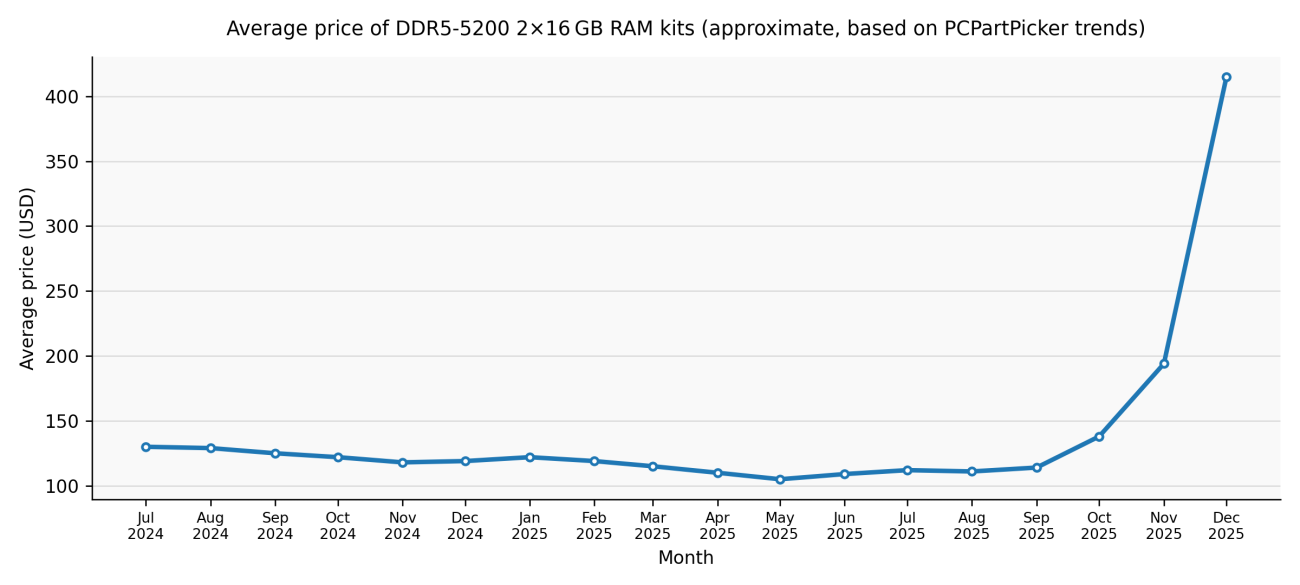

Per gran parte dell’era del PC, la memoria è rimasta sullo sfondo. Tra il 2024 e il 2026, questa dinamica si è ribaltata. La memoria è diventata il vincolo principale nella progettazione dei sistemi e il costo del “basta aggiungere più RAM” è aumentato bruscamente nel giro di pochi trimestri.

I prezzi sono saliti, la disponibilità si è ridotta e i prodotti vengono sempre più spesso spediti con il minimo indispensabile di memoria invece del margine confortevole a cui eravamo abituati. È in corso un riequilibrio strutturale su chi ottiene i wafer e perché.

Quindi, che cosa è cambiato davvero e perché questa carenza sembra diversa dalle precedenti? Lo analizzeremo qui, nel primo di una serie in due parti che tratta le forze che stanno sconvolgendo la fornitura di memoria, dai server cloud fino ai sistemi embedded. La seconda parte, Progettare hardware in una carenza di memoria, approfondisce il tema con un’analisi dettagliata dei componenti di memoria di nuova generazione che stanno appena entrando sul mercato, dei principali prodotti “workhorse” che puoi ordinare oggi dal tuo distributore, dei pattern di progettazione e delle tattiche di approvvigionamento.

Come i data center AI stanno riscrivendo il panorama della domanda

Nei cicli precedenti, la domanda di memoria era distribuita in modo ampio tra PC, telefoni, server ed elettronica di consumo. Domanda e offerta uscivano dalla sincronizzazione, i prezzi salivano o scendevano, e poi la situazione si normalizzava man mano che le fab si adeguavano. La carenza del 2024–2026 non sta seguendo questo copione.

La differenza sta in chi compra. I data center incentrati sull’AI ora dominano il quadro della domanda, e i loro cluster di training e le loro farm di inferenza richiedono enormi quantità di memoria ad alta larghezza di banda (HBM) e di DRAM convenzionale per GPU o acceleratore. L’HBM consuma una capacità di wafer significativamente maggiore per bit rispetto alla DRAM standard, rendendola estremamente interessante per i produttori che cercano di assicurarsi contratti pluriennali ad alto margine con i fornitori di infrastrutture AI.

Alcuni analisti stimano ora che i data center consumeranno fino al 70% di tutti i chip di memoria di fascia alta prodotti nel 2026, un netto ribaltamento rispetto all’epoca in cui i dispositivi consumer rappresentavano la maggioranza di questi chip. In questo contesto, la memoria per PC e mobile diventa un’attività secondaria, mentre i data center AI diventano l’evento principale.

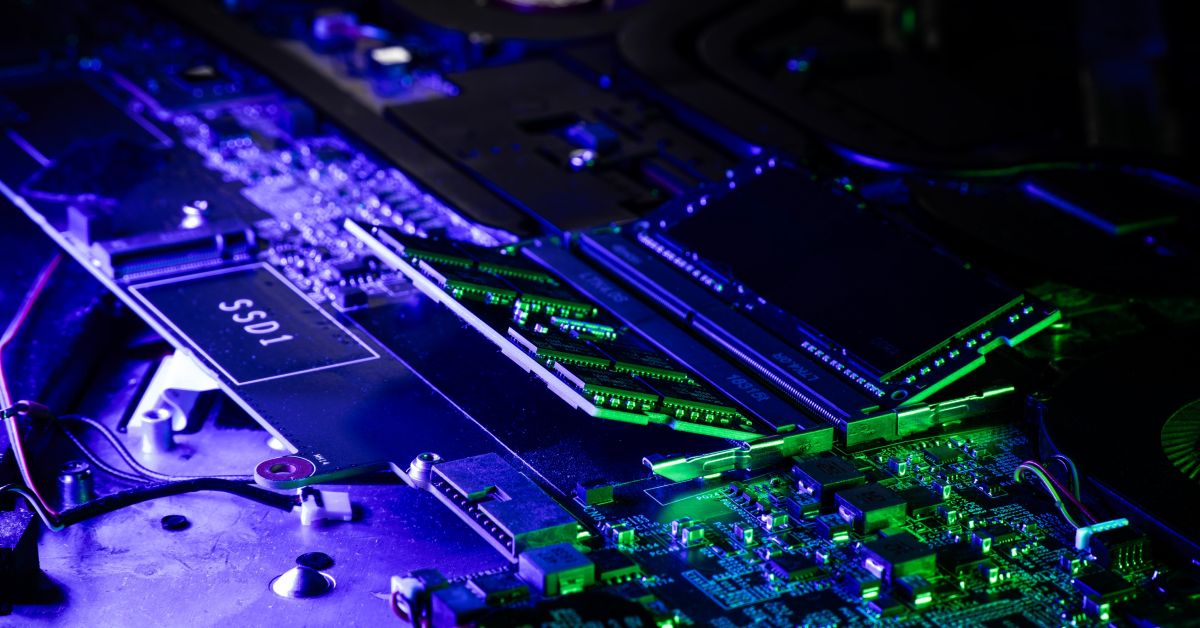

La generazione HBM4 presentata al CES 2026 illustra la portata di questo cambiamento. SK Hynix ha mostrato un dispositivo a 16 layer da 48 GB che offre oltre 2 TB/s, aumentando in modo significativo le prestazioni delle prime HBM3 utilizzate nei primi acceleratori gen-AI. Ogni wafer destinato a questi stack non viene usato per produrre DDR5 per il tuo prossimo PC o LPDDR5X per uno smartphone.

Progetti embedded e legacy: stretti ai margini

I progetti embedded e industriali, che spesso si basano su standard DRAM più vecchi o su NAND SLC mature, stanno affrontando difficoltà proprie. Molti di questi prodotti utilizzano DDR3 o prime DDR4, insieme a flash NAND parallela, che non sono più al centro delle roadmap dei fornitori.

Poiché i produttori danno priorità a HBM ad alto margine e DRAM di classe server, stanno riducendo o interrompendo le linee legacy. Ciò che resta ha prezzi inaspettatamente elevati e tempi di consegna più lunghi, anche se la tecnologia in sé è matura.

Monitorare da vicino lo stato del ciclo di vita dei componenti con strumenti come Octopart aiuta i team a individuare annunci EOL e irrigidimenti dell’offerta prima che diventino emergenze.

Progressi sotto pressione: DDR5, LPDDR6, NAND e HBM4

Le stesse transizioni tecnologiche che stanno privando i progetti più vecchi della disponibilità stanno producendo autentici progressi ingegneristici. Comprendere entrambi i lati di questa dinamica è importante, perché i progressi stanno cambiando ciò che è disponibile per la progettazione, mentre le economie dei wafer che li sostengono spiegano perché la memoria commodity non diventerà meno costosa a breve.

DRAM

Samsung sta producendo in volumi la DRAM LPDDR5X di classe 12 nm più sottile per dispositivi mobili di nuova generazione, combinando alte prestazioni con efficienza energetica e packaging sottile adatto a smartphone premium e ultraportatili. I primi componenti LPDDR6 spingono ancora oltre larghezza di banda ed efficienza energetica, puntando ad applicazioni AI on-device e automotive. L’implementazione LPDDR6 di Samsung sta ottenendo riconoscimenti agli eventi di settore, segnalando la direzione verso cui si sta muovendo la memoria mobile di fascia alta.

HBM

All’estremo HBM dello spettro, la copertura del CES 2026 su HBM4 mostra che gli stack di memoria stanno diventando sottosistemi altamente integrati. Gli stack a 16 die di SK Hynix utilizzano MR-MUF e wafer DRAM ultrasottili per rimanere entro i limiti di altezza JEDEC, mentre Samsung guarda alla propria logica a 4 nm (che ha avviato la produzione in volumi nel febbraio 2026) per migliorare termica ed efficienza energetica. Tutto questo sforzo ingegneristico e tutta questa capacità wafer sono chiaramente destinati agli acceleratori AI.

NAND

Sul fronte NAND, i fornitori stanno impilando un numero sempre maggiore di layer. La V-NAND di decima generazione con oltre 400 layer e interfacce intorno a 5,6 GT/s viene progettata in SSD PCIe 5.0 e futuri PCIe 6.0 per casi d’uso data center e AI. La BiCS NAND a 332 layer di decima generazione di Kioxia e Sandisk, che utilizza l’interfaccia Toggle DDR 6.0 fino a 4,8 Gb/s per pin, dimostra quanto sia avanzata la NAND ad alta larghezza di banda per SSD di classe data center ed enterprise.

La tecnologia avanza, ma la capacità non tiene il passo. Secondo EE Times, Samsung e SK Hynix hanno ridotto l’output di wafer NAND nel 2024–2025 mentre inseguivano HBM e DRAM, e non hanno annunciato nuova capacità NAND pur controllando oltre metà del mercato. I dati di Omdia mostrano i wafer NAND di Samsung in calo da 4,9 milioni (2024) a 4,68 milioni (2025), e quelli di SK Hynix da 1,9 milioni a 1,7 milioni.

Allo stesso tempo, la NAND è diventata critica per l’inferenza AI. Man mano che l’AI passa dal training all’erogazione dei modelli, gli SSD basati su NAND ad alto numero di layer diventano sempre più spesso l’archivio principale per i pesi dei modelli e i dati di lavoro. Il management di Kioxia ha dichiarato che l’intera produzione NAND del 2026 è già esaurita, che BiCS10 è stata anticipata dalla seconda metà del 2027 al 2026 e che, in futuro, quasi metà della domanda NAND potrebbe provenire da applicazioni AI. Specialisti NAND come Kioxia e la nuova attività indipendente Sandisk, un tempo considerati outsider in un mercato commoditizzato, si trovano improvvisamente in posizione vincente nel boom degli SSD per AI.

Perché la solita ripresa non arriverà

Gli analisti di settore indicano una crescita relativamente modesta dell’offerta di DRAM e NAND fino al 2026 rispetto alle norme storiche. Nel frattempo, la domanda non rallenta. Nuove architetture di modelli, carichi di lavoro di inferenza e implementazioni edge-AI continuano a spingere verso l’alto i requisiti di memoria invece di lasciarli stabilizzarsi. I fornitori di HBM4 stanno dedicando una quota sostanziale della capacità wafer ai requisiti di Nvidia e di altri acceleratori e, come abbiamo menzionato nella sezione precedente, i fornitori NAND come Kioxia hanno già esaurito la produzione per il 2026.

Nel dicembre 2025, Micron ha dimostrato la natura strutturale di questo cambiamento annunciando l’uscita dal business consumer Crucial per supportare meglio “clienti più grandi e strategici”. Alcuni fornitori, tra cui Micron, hanno dichiarato pubblicamente di non aspettarsi un allentamento sostanziale della carenza di RAM per i consumatori prima del 2028 circa, quando nuova capacità e transizioni di processo dovrebbero entrare pienamente a regime. La stessa logica si applica sempre più anche alla NAND: l’inferenza AI sta bloccando la futura disponibilità di SSD-class con la stessa rapidità con cui i fornitori riescono a portarla online.

Nel dicembre 2025, IDC ha descritto la carenza come “non solo una carenza ciclica ma una potenziale riallocazione permanente e strategica della capacità mondiale dei wafer di silicio”. Nel febbraio 2026, TrendForce ha rivisto nettamente al rialzo la previsione dei prezzi contrattuali della DRAM convenzionale per il Q1 2026, da una stima precedente del 55–60% al 90–95% trimestre su trimestre. All’interno di questo dato, la DRAM per PC (mix DDR4/DDR5) era prevista in aumento del 105–110% QoQ, un nuovo record trimestrale.

Cosa c’è dopo: dalla comprensione all’azione

In Progettare hardware in una carenza di memoria, esaminiamo sette componenti di memoria della prossima ondata in fase di ramp-up nei progetti OEM e data center, otto prodotti DRAM e flash “workhorse” facilmente disponibili presso i principali distributori e playbook concreti per operare entro questi vincoli.

Domande frequenti

Perché c’è una carenza di memoria anche se la tecnologia DRAM e NAND continua a migliorare?

L’attuale carenza non è causata da limiti tecnologici ma dalle economie di allocazione dei wafer. Una quota crescente della capacità globale dei wafer per memorie viene reindirizzata verso memoria AI ad alto margine, in particolare HBM per acceleratori da data center. Poiché l’HBM consuma un’area di wafer significativamente maggiore per bit utile rispetto alla DRAM convenzionale, ogni wafer destinato alla produzione HBM riduce l’output di DDR4, DDR5, LPDDR e NAND. Con un’espansione limitata delle nuove fab e contratti di fornitura AI a lungo termine che bloccano la capacità, i miglioramenti nella densità di memoria non si traducono in una maggiore disponibilità per i mercati mainstream o embedded.

Perché questa carenza di memoria sembra diversa dai cicli passati?

A differenza dei precedenti cicli boom-bust, questa carenza è modellata da una concentrazione strutturale della domanda piuttosto che da un eccesso temporaneo di consumo. I carichi di lavoro di training e inferenza AI continuano ad aumentare i requisiti di memoria, mentre i fornitori hanno deliberatamente limitato la crescita della capacità. Contratti HBM pluriennali, produzione NAND del 2026 già esaurita e indicazioni esplicite dei fornitori che rimandano il sollievo solo al periodo successivo al 2027–2028 significano che si tratta di una riallocazione di lunga durata, non di uno squilibrio di breve termine che si correggerà da solo solo tramite i prezzi.

Quali rischi comporta questo per i progetti embedded e legacy che utilizzano DDR3, le prime DDR4 o NAND SLC?

I prodotti di memoria legacy sono sempre più considerati non strategici dai principali fornitori. Poiché i vendor danno priorità a DRAM avanzate e HBM, i nodi di processo più vecchi devono fare i conti con lotti di produzione sempre più ridotti, quantitativi minimi d’ordine in aumento, lead time più lunghi e un rischio di fine vita del prodotto più elevato. Anche quando i componenti risultano tecnicamente ancora “in produzione”, i prezzi diventano volatili e la disponibilità imprevedibile. Per i team embedded, questo aumenta l’importanza del monitoraggio del ciclo di vita, del multi-sourcing e della pianificazione della riprogettazione molto prima nel ciclo di vita del prodotto rispetto alle generazioni passate.

Quando gli ingegneri possono aspettarsi una normalizzazione dei prezzi e della disponibilità delle memorie?

In base alle dichiarazioni dei fornitori e alle previsioni degli analisti, è improbabile un sollievo significativo prima della fine del 2027 o del 2028. Sono previsti nuovi incrementi di capacità, transizioni di processo ed espansioni delle linee di packaging per HBM e NAND avanzate, ma serviranno diversi anni prima che entrino in funzione. Allo stesso tempo, i carichi di lavoro di inferenza AI stanno ampliando la domanda sia di DRAM sia di NAND di classe SSD, assorbendo gran parte di questa capacità futura. Gli ingegneri dovrebbero progettare partendo dal presupposto che la memoria rimarrà un costo di sistema vincolato e ad alto impatto per il resto di questo decennio.