O que é um ambiente de projeto integrado para eletrônica?

A descoberta tardia de restrições mecânicas é uma causa comum de atrasos no cronograma e retrabalho em projetos eletrônicos.

Considere um cenário típico: três meses após o início de um projeto, o esquemático está concluído e o layout da PCB está em grande parte finalizado. Só então o cliente menciona que uma segunda PCB é montada alguns milímetros acima da placa principal, algo que ele presumiu ser óbvio a partir de fotos anteriores. Nesse ponto, conectores e componentes previamente selecionados são altos demais, forçando a reseleção de peças que já são difíceis de obter devido aos requisitos de tensão e corrente. Várias semanas de trabalho são perdidas para lidar com uma restrição que nunca foi formalmente registrada.

Esse tipo de problema não é incomum. É um resultado previsível de fluxos de trabalho de projeto desconectados.

Principais conclusões

- Um ambiente de projeto integrado combina captura esquemática, layout de PCB, simulação, colaboração MCAD e gerenciamento de dados, para que os engenheiros não sejam obrigados a alternar entre ferramentas desconectadas.

- Regras e restrições de projeto (como folga, espaçamento e altura de componentes) devem ser verificadas em tempo real durante o projeto, e não depois que os arquivos forem liberados para fabricação.

- Restrições mecânicas e de firmware devem ser introduzidas no início de um projeto. Descobri-las após a seleção de componentes leva a retrabalho e atrasos desnecessários.

O problema: seis ferramentas para construir uma placa

Em muitas equipes de hardware, o fluxo de trabalho de projeto está distribuído entre várias ferramentas desconectadas. As definições de pad stack podem estar em uma aplicação. Símbolos esquemáticos e bibliotecas são gerenciados em uma ferramenta separada e frequentemente armazenados em diferentes pastas locais ou de rede. O layout da PCB é tratado em outro lugar. Integração de sistema, integridade de sinal e análise de EMI normalmente são realizadas em aplicações adicionais e especializadas. O acompanhamento do projeto e o gerenciamento de tarefas geralmente são baseados na web e nem sempre acessíveis quando os engenheiros estão trabalhando offline.

Como resultado, os engenheiros precisam aprender e manter proficiência em pelo menos cinco ferramentas diferentes apenas para levar um projeto da captura esquemática até uma PCB fabricável.

Em equipes pequenas, essa fragmentação cria sobrecarga adicional. Alternar entre ferramentas exige exportações e importações frequentes de arquivos, com risco de erros de tradução em cada etapa. Bibliotecas e footprints precisam ser colocados em estruturas de diretório específicas para continuarem utilizáveis; um arquivo no local errado pode impedir que um componente seja transferido corretamente do esquemático para o layout.

Perde-se um tempo significativo localizando símbolos esquemáticos, footprints de PCB e as versões corretas dos arquivos, um trabalho que deveria ser trivial, mas que frequentemente consome dias ou semanas ao longo de um projeto.

Apesar do número de ferramentas envolvidas, a coordenação final ainda depende de e-mails e planilhas. As próprias ferramentas permanecem em grande parte desconectadas, oferecendo pouca visibilidade compartilhada ao longo do processo de projeto.

O que realmente significa um ambiente de projeto integrado

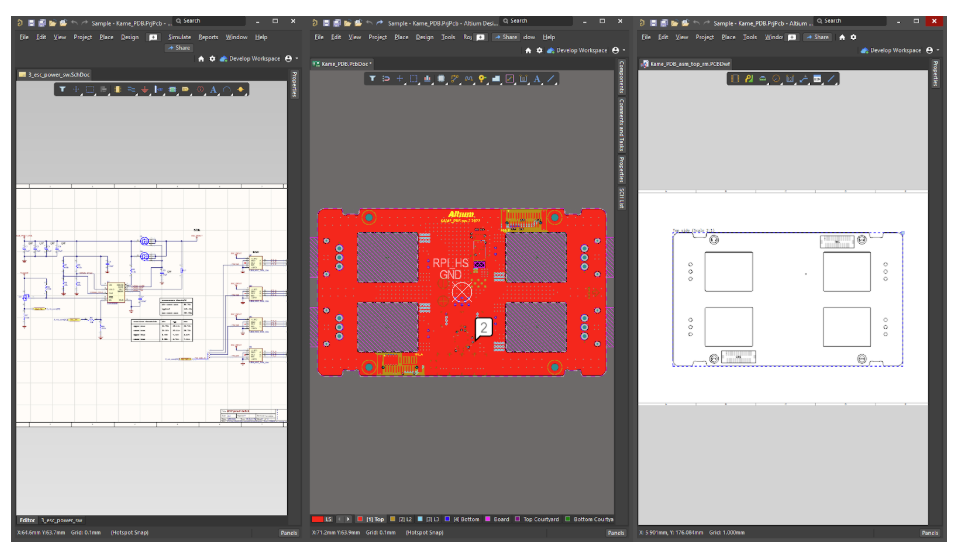

Um ambiente de projeto integrado para eletrônica é uma única aplicação, ou um conjunto de ferramentas fortemente acopladas, que dá suporte a todo o fluxo de trabalho de projeto de hardware:

- Captura esquemática para projeto de circuitos

- Layout de PCB para posicionamento de componentes e roteamento

- Simulação para validação antes da fabricação

- Colaboração ECAD-MCAD para que as equipes elétrica e mecânica trabalhem com os mesmos dados

- Gerenciamento de dados para bibliotecas de componentes, arquivos de projeto e requisitos de projeto

Em um ambiente integrado, os mesmos dados subjacentes são usados em todas as etapas do projeto. Alterações feitas no esquemático se propagam diretamente para o layout da PCB. Restrições mecânicas, como contornos da placa ou folgas do invólucro, ficam visíveis no ambiente de projeto elétrico à medida que são atualizadas.

Isso elimina exportações manuais, importações de arquivos e incompatibilidades de versão que são comuns em cadeias de ferramentas construídas em torno de aplicações desconectadas.

- Para uma explicação detalhada de como isso funciona na prática entre equipes elétricas e mecânicas, consulte colaboração ECAD-MCAD no Altium Develop.

Como a integração fecha o ciclo de feedback

Aqui está um cenário comum em um projeto de eletrônica de potência. O layout da PCB é criado em uma ferramenta, a captura esquemática é feita em outra, e o invólucro é projetado separadamente no PTC Creo pelo engenheiro mecânico. Nenhum desses ambientes compartilha dados de projeto em tempo real.

Nesse caso, o invólucro mal acomodava a PCB, e os conjuntos de cabos violavam os requisitos de espaçamento. Esses problemas não eram erros de projeto isoladamente. Eles ocorreram porque nenhum ambiente único fornecia visibilidade do contexto mecânico e elétrico completo. Resolver os conflitos exigiu vários ciclos de ida e volta entre as equipes elétrica e mecânica e acrescentou de duas a três semanas ao cronograma.

Quando as ferramentas ECAD e MCAD são integradas, esse ciclo de feedback se fecha. O engenheiro mecânico define o contorno da placa e as restrições diretamente a partir do modelo do invólucro, e essas restrições se propagam para o layout da PCB. O engenheiro elétrico vê imediatamente a área disponível da placa, as posições validadas dos furos de montagem e os limites de altura dos componentes antes de se comprometer com a seleção de peças ou decisões de roteamento.

Essa sincronização bidirecional reduz iterações, evita conflitos em estágio avançado e encurta os ciclos gerais de projeto.

- Para detalhes adicionais sobre colaboração ECAD-MCAD, consulte a documentação do MCAD CoDesigner.

Validação de regras de projeto em tempo real salva suas placas

Vias de caminho de retorno, violações de folga e erros de espaçamento relacionados a design for fabrication ou design for assembly são causas comuns de retrabalho e respins de PCB. Esses problemas frequentemente passam despercebidos quando as regras de projeto só são verificadas após a conclusão do layout.

A validação de regras de projeto em tempo real sinaliza violações no momento em que são introduzidas. Se uma restrição de folga for violada, isso fica imediatamente visível. Se a largura de uma trilha não atender aos requisitos de sua classe de net atribuída, o erro é destacado diretamente no layout.

Essa abordagem difere das verificações de regras de projeto em lote, que identificam problemas apenas depois que o trabalho de projeto está concluído. Verificações em lote revelam problemas que podem ter sido introduzidos horas ou dias antes. A verificação em tempo real impede que esses erros se propaguem ao aplicar as restrições durante o layout.

O custo real do “está bom”

“Nossa cadeia de ferramentas atual funciona bem” muitas vezes significa que o processo é frágil.

Em um projeto, um software de captura esquemática foi usado para projeto de cabos e chicotes. Embora isso fosse tecnicamente possível, a ferramenta não foi projetada para esse propósito. Como resultado, alterações elétricas não se propagavam automaticamente para os desenhos, e cada rótulo e campo de texto precisava ser atualizado manualmente.

Isso criou falhas previsíveis. Vários conjuntos de cabos foram montados com fiação incorreta porque a documentação estava fora de sincronia com o projeto real. Os engenheiros gastaram um tempo significativo revisando, conferindo novamente e corrigindo erros que deveriam ter sido evitados pela própria ferramenta. A produtividade individual caiu para cerca de 40–50% devido à sobrecarga constante de atualizações manuais e verificação.

O sistema funcionava, mas apenas no sentido de que não falhava imediatamente. O custo real do “está bom” foi pago em retrabalho, atrasos e redução da capacidade de engenharia.

Quando firmware e mecânica aparecem tarde demais

Em um projeto recente, o projeto da PCB principal foi concluído, a lista de materiais finalizada e o projeto estava pronto para ser liberado para fabricação.

Nesse momento, surgiu uma nova restrição: uma placa secundária de LED seria montada sobre a placa principal, com apenas 10 mm de folga vertical.

Esse requisito tardio forçou um redesenho da área afetada. Os conectores existentes excediam a altura permitida. Componentes com capacidade de corrente suficiente não estavam disponíveis em encapsulamentos de baixo perfil. Peças alternativas que atendiam ao requisito de altura tinham quantidades mínimas de pedido impraticáveis ou já estavam obsoletas.

Aproximadamente quatro semanas foram gastas avaliando alternativas, resultando em US$ 2.000 em custos adicionais de consultoria (cerca de 10% do orçamento total do projeto), apenas para determinar que a abordagem original de projeto não era viável.

Agravando o problema, as paralisações do Ano-Novo Chinês atrasaram a fabricação. Placas que deveriam ter sido enviadas em outubro ou novembro só foram entregues em março.

A causa raiz não foi uma falha técnica, mas uma falha de processo. As restrições mecânicas não foram comunicadas no início do projeto, e não havia um ambiente compartilhado em que as equipes elétrica, mecânica e de firmware pudessem visualizar e validar requisitos em nível de sistema no início do ciclo de projeto.

Por que tudo precisa funcionar em conjunto

Sistemas de software muitas vezes conseguem tolerar falhas parciais. Se uma função quebra, outras partes da aplicação podem continuar funcionando, permitindo que os problemas sejam corrigidos de forma incremental.

Sistemas de hardware não se comportam dessa maneira.

Se a arquitetura de potência estiver incorreta, se level shifters forem aplicados incorretamente, ou se interfaces fundamentais falharem, grandes partes da placa não funcionarão, ou o sistema pode nem sequer ligar. Hardware exige um alto grau de correção em todos os subsistemas antes que testes significativos possam começar.

Como o hardware é inerentemente integrado, o processo de desenvolvimento também deve ser integrado. Os requisitos não podem ficar em threads de e-mail. As regras de projeto não podem ser verificadas apenas no final do processo de layout. Restrições mecânicas não podem ser descobertas meses após o início do desenvolvimento sem introduzir retrabalho e atraso.

As ferramentas de projeto devem refletir essa realidade. Dados elétricos, mecânicos e de componentes precisam estar conectados, visíveis e acessíveis ao longo de todo o ciclo de projeto, e não gerenciados como arquivos desconectados e transferências manuais.

Para equipes prontas para deixar para trás a cadeia de ferramentas desconectada, Altium Develop é um bom ponto de partida.

Se você precisa desenvolver eletrônica de potência confiável ou sistemas digitais avançados, Altium Develop une todas as disciplinas em uma única força colaborativa. Livre de silos. Livre de limites. É onde engenheiros, projetistas e inovadores trabalham como um só para cocriar sem restrições. Experimente o Altium Develop hoje mesmo!

Perguntas frequentes

O que é um ambiente de projeto integrado para eletrônica?

Um ambiente de projeto integrado reúne captura esquemática, layout de PCB, simulação, colaboração ECAD-MCAD e gerenciamento de dados em um único fluxo de trabalho conectado. Em vez de mover arquivos entre ferramentas separadas, os engenheiros trabalham com dados compartilhados para que as alterações se propaguem automaticamente entre as etapas do projeto.

Como um ambiente integrado reduz retrabalho e atrasos no cronograma?

Ao validar restrições elétricas, mecânicas e de fabricação em tempo real, problemas como violações de folga, limites de altura de componentes ou conflitos de roteamento são detectados no momento em que ocorrem, e não semanas depois. Isso evita redesenhos em estágio avançado, que normalmente causam atrasos no cronograma e custos adicionais.

Por que a integração ECAD-MCAD é crítica no início de um projeto?

Restrições mecânicas, como a geometria do gabinete, o empilhamento das placas e o alinhamento dos conectores, afetam diretamente a seleção de componentes e as decisões de layout. Quando essas restrições estão visíveis desde o início, as equipes evitam escolher peças ou arquiteturas que mais tarde se revelem inviáveis.

Como a verificação de regras de projeto em tempo real difere das verificações tradicionais em lote?

A verificação em tempo real sinaliza erros imediatamente quando uma regra é violada, permitindo que os engenheiros corrijam os problemas antes que eles se propaguem. As verificações em lote só identificam os problemas depois que o layout está concluído, muitas vezes exigindo retrocessos significativos e retrabalho.