Chiplet là gì và Chúng được Sử dụng như thế nào trong Đóng gói?

Chiplet là những vi mạch nhỏ với chức năng chuyên biệt. Chúng được thiết kế để kết hợp lại với nhau tạo thành một mạch tích hợp lớn hơn, theo xu hướng tích hợp đa dạng của ngành công nghiệp bán dẫn. Khả năng lựa chọn từ một loạt các chip nhỏ, chuyên biệt cao, sau đó phối hợp chúng lại để tạo ra chức năng tổng thể mong muốn, là một bước tiến lớn so với phương pháp truyền thống là hệ thống trên chip (SoC) trong đóng gói bán dẫn. Các nhà cung cấp lớn đã sản xuất các bộ vi xử lý máy tính kết hợp một số lượng nhất định của chiplet, thay vì đi theo con đường truyền thống của việc sản xuất bán dẫn đơn khối, nơi thiết bị được chế tạo trên một miếng silicon duy nhất.

Mặc dù ý tưởng về chiplet đã tồn tại hàng thập kỷ, nhưng việc đóng gói dựa trên chiplet đang thúc đẩy các loại linh kiện, sản phẩm và hệ thống mới cho các ứng dụng chuyên biệt. Những linh kiện này được thiết kế riêng cho các ứng dụng cụ thể, và ngày càng có nhiều công ty tham gia vào trò chơi thiết kế chip với trọng tâm là chiplet làm bộ xử lý cốt lõi của họ. Dựa trên số lượng các bài báo nghiên cứu, đơn đăng ký sáng chế và bài viết kỹ thuật bạn có thể tìm thấy trực tuyến, rõ ràng là các thành phần dựa trên chiplet sẽ tồn tại lâu dài.

Nếu bạn là một nhà thiết kế hệ thống và bạn đang cân nhắc các lựa chọn bộ vi xử lý, bạn có thể không nhận ra rằng chiplet chính là nền tảng cho hệ thống của bạn. Tuy nhiên, chiplet là xương sống cho phép tích hợp đa dạng chức năng tìm thấy trong các chip hiện đại, và khái niệm đóng gói này tiếp tục thúc đẩy việc tích hợp các tính năng mới vào thiết kế chip. Ví dụ bao gồm việc tích hợp các khối FPGA và các khối tăng tốc AI vào cùng một gói với bộ nhớ, CPU và thậm chí là các thành phần RF.

Tại sao lại là Chiplet?

Chi phí và hiệu suất là hai vấn đề cấp bách nhất trong thiết kế và sản xuất chip. Những năm gần đây đã chứng kiến sự chậm lại của quy luật Dennard và quy luật Moore, dẫn đến khoảng thời gian dài hơn giữa các nút công nghệ quy trình. Hơn nữa, việc tích hợp transistor trên một chip đơn khối ngày càng trở nên thách thức hơn vì có ít lựa chọn có sẵn cho việc thu nhỏ thiết bị. Những thách thức này đã làm giảm ROI cho bán dẫn đơn khối do quy trình sản xuất đắt đỏ hơn.

Cách duy nhất để tăng số lượng đơn vị chức năng tích hợp với cùng kích thước transistor là mở rộng diện tích chip, hoặc theo phương diện thiết bị hoặc theo chiều dọc. Vấn đề với việc tăng diện tích chip là những chip lớn hơn dễ bị lỗi sản xuất hơn, điều này hạn chế hiệu suất wafer và tăng giá của sản phẩm giao cho khách hàng. Do đó, chip đơn khối ngày càng không thể cung cấp hiệu suất mong muốn trước nhu cầu tính toán tăng cao.

Vì vậy, để hỗ trợ các ứng dụng tính toán cao như AI/ML trên thiết bị, mạng siêu nhanh, sự kết hợp cảm biến, và thiết bị di động thế hệ tiếp theo, chúng ta đã chứng kiến sự xuất hiện của hệ thống dựa trên chiplet cho việc phát triển hiệu quả về chi phí của điện tử hiệu năng cao. Điều này đã được mở rộng từ SoCs tiên tiến đến bộ xử lý máy tính để bàn/máy chủ và GPU.

Vượt qua “Bức Tường Diện Tích”

Vấn đề "bức tường diện tích" là kết quả của sự không phù hợp giữa nhu cầu về chip diện tích lớn của hệ thống tính toán hiệu năng cao và tỷ lệ lợi nhuận thấp của sản xuất bán dẫn. Bức tường diện tích đề cập đến thách thức này trong sản xuất bán dẫn đơn khối, nơi mà chip lớn hơn được sử dụng để tăng mật độ tính năng, nhưng số lượng lỗi cũng tăng lên. Khi khả năng xử lý sản xuất chuyển sang các nút tiên tiến hơn, tỷ lệ lợi nhuận giảm, và do đó, chi phí cho khách hàng cuối cùng tăng lên. Vì vậy, luôn có động lực để giảm rủi ro sản xuất cho những sản phẩm này bằng cách loại bỏ cơ hội cho lỗi.

Một giải pháp cho bức tường diện tích sẽ giảm tổng chi phí của một sản phẩm cuối cùng bằng cách giảm lãng phí trong quá trình sản xuất. Chiplet cơ bản làm đa dạng hóa hồ sơ rủi ro cho một sản phẩm bằng cách phân tán nó qua nhiều vi mạch bán dẫn. Kết quả cuối cùng là giảm chi phí và khả năng đa dạng hóa chức năng một cách rộng rãi hơn nhiều so với trong một thành phần đơn khối.

Giảm Chi Phí

Nhiều chiplet được kết hợp với các kỹ thuật đóng gói đặc biệt để tạo thành một IC lớn hơn như một phương án thay thế cho cấu trúc đơn khối. Vì chiplet được sản xuất trên một diện tích nhỏ hơn, thường trên các wafer tròn, ảnh hưởng của lỗi sản xuất được giảm bớt và việc sử dụng diện tích tăng lên. Do đó, chi phí được giảm bởi vì tỷ lệ lợi nhuận wafer đáng kể cao hơn khi chiplet được sử dụng để tạo ra một thành phần.

Tích hợp không đồng nhất là một lợi ích đáng kể khác của chiplet, đặc biệt là về việc giảm chi phí thiết kế và sản xuất IC. Mỗi chiplet có thể được sản xuất bằng cách sử dụng các nút quy trình khác nhau, điều mà AMD tiết lộ đã được thực hiện với sản phẩm Ryzen 7 của họ. Một ví dụ khác từ AMD là một bằng sáng chế gần đây cho GPU dựa trên chiplet; kiến trúc cho hệ thống này được hiển thị trong tác phẩm gốc dưới đây:

Nhiều vật liệu (ví dụ, chiplet GaN và Si) cũng có thể được kết hợp vào cùng một gói với cách tiếp cận này. Việc sử dụng các nút công nghệ quy trình khác nhau giảm tổng rủi ro được xây dựng vào sản phẩm; rủi ro cao nhất chỉ được giới hạn ở chiplet đang được sản xuất tại nút quy trình tiên tiến nhất, thay vì trải rộng qua toàn bộ chip.

Tái Sử Dụng Thiết Kế

Một khi chiplet được phát triển, nó có thể được tái sử dụng, giảm chi phí kiểm tra và xác minh. Hiệu quả chi phí của quá trình thiết kế chip là đáng kể cao hơn thông qua việc sử dụng các mô-đun chiplet vì chúng có thể được tái sử dụng. Một kịch bản tái sử dụng chiplet là chỉ thiết kế và sản xuất chiplet cốt lõi cho một IC, trong khi các chiplet còn lại trong gói được mua từ nhà cung cấp khác. Sử dụng cách tiếp cận này với các chiplet sẵn có từ nhiều nhà cung cấp, hoặc bằng cách tái sử dụng IP trong một thiết kế mới, giảm đáng kể tổng chi phí thiết kế và xác minh của sản phẩm.

Trong trường hợp cần cập nhật hệ thống, một chiplet có thể được thay thế bằng chiplet khác bên trong bao bì. Lưu ý rằng bản thân bao bì có thể cần được cập nhật, nhưng đây là một nhiệm vụ thiết kế ít khó khăn hơn nhiều so với việc thiết kế lại một thành phần đơn khối hoàn toàn. Một phần nhỏ của hệ thống cũng có thể được thiết kế lại mà không phải chịu chi phí xác minh mới mà sẽ phát sinh trong gói bán dẫn đơn khối. Phương pháp tái sử dụng chiplet này được gọi là “tái sử dụng không đồng nhất”.

Một kịch bản tái sử dụng chiplet khác là tích hợp nhiều chiplet giống hệt nhau vào cùng một hệ thống. Phương pháp này lý tưởng cho các hệ thống có thể mở rộng và cải thiện đáng kể hiệu quả của chúng trong khi giảm chi phí. Điều này được gọi là phương pháp tái sử dụng đồng nhất và lợi ích chính là chỉ cần tăng số lượng chiplet trong kiến trúc là đủ để đáp ứng các yêu cầu về hiệu suất và công suất khác nhau.

Công nghệ Đóng Gói Chiplet

Để tạo ra sản phẩm dựa trên chiplet, bạn cần kỹ năng thiết kế, dies, kết nối giữa các dies, và một chiến lược sản xuất. Hiệu suất, giá cả, và độ chín của công nghệ đóng gói chiplet có ảnh hưởng đáng kể đến việc áp dụng chiplet. Dựa vào sự khác biệt trong phương tiện kết nối và phương pháp, công nghệ đóng gói được sử dụng cho việc kết nối chiplet có thể được phân loại thành ba nhóm:

-

Đóng gói dựa trên Substrate

-

Đóng gói Silicon-interposer

-

Đóng gói Redistribution-layer (RDL)

-

Embedded multi-die interconnect bridge (EMIB)

Đóng Gói Dựa Trên Substrate

Trong đóng gói dựa trên substrate, lựa chọn substrate phổ biến là vật liệu hữu cơ vì chúng dễ dàng có sẵn. Tương tự như PCB thông thường, các kết nối dây được tạo ra thông qua quá trình ăn mòn độc lập với các quá trình khác được sử dụng trong sản xuất bán dẫn. Đây được biết đến như là hình thức đầu tiên của tích hợp không đồng nhất 2D.

Thông qua thiết kế flip-chip hoặc xếp chồng, nhiều dies có thể dễ dàng được kết nối với một substrate có mật độ cao. Hơn nữa, chi phí vật liệu và sản xuất liên quan đến nó là tối thiểu vì công nghệ này không phụ thuộc vào quá trình sản xuất chip. Nhược điểm chính của việc sử dụng công nghệ này là mật độ chân I/O thấp và hạn chế kết quả trong băng thông của các kết nối trong các gói này.

Đóng Gói Silicon Interposer

Công nghệ này bao gồm công nghệ đóng gói 2.5D và 3D, nơi các chip được xây dựng theo chiều ngang trên một bộ chuyển đổi (2.5D) hoặc xếp chồng lên nhau theo chiều dọc (3D). Để thực hiện kết nối và giao tiếp giữa các vi mạch, lớp bộ chuyển đổi silicon được đặt giữa lớp nền và các vi mạch. Bộ chuyển đổi giống như một tấm mạch in thu nhỏ, cung cấp cơ sở cho các kết nối điện giữa các chiplet. Lớp kết nối được xây dựng từ các tiếp điểm kim loại (gọi là micro bumps) và các vias qua silicon (TSV) chạy bên trong gói. Chúng được sử dụng để kết nối vi mạch với bộ chuyển đổi, và các kết nối bộ chuyển đổi với lớp nền gói có mẫu BGA.

Các sản phẩm này có mật độ I/O cao hơn với mức tiêu thụ năng lượng giảm và độ trễ truyền thấp hơn. Điều này được kích hoạt bởi chiều dài và khoảng cách giữa các micro bumps và TSVs nhỏ hơn. Nhược điểm đáng kể duy nhất của công nghệ này là chi phí sản xuất tăng cao.

Đóng Gói RDL

Công nghệ đóng gói lớp phân phối lại (RDL) không sử dụng lớp nền, thay vào đó là việc trực tiếp phủ lớp điện môi và kim loại lên bề mặt trên của wafer. Công nghệ này còn được gọi là công nghệ ‘fanout’. Để thực hiện thiết kế dây, một lớp phân phối lại được xây dựng sao cho các cổng I/O trên mỗi chiplet được bố trí xung quanh thiết bị. Bằng cách rút ngắn chiều dài của mạch, RDL cung cấp độ tin cậy tín hiệu cao hơn (giảm tổn thất và méo).

Cầu Kết Nối Đa Vi Mạch Nhúng

EMIB là công nghệ sử dụng các phần wafer silicon mỏng nhúng vào các vật liệu hữu cơ làm lớp nền cho kết nối vi mạch với vi mạch. Vấn đề chi phí cao trong các sản phẩm tiên tiến có thể được giải quyết bằng cách sử dụng đóng gói cầu với các chiplet đa dạng. Công nghệ đóng gói lai này là sự kết hợp của đóng gói dựa trên lớp nền và đóng gói dựa trên bộ chuyển đổi. Các lớp silicon mỏng, thường ít hơn 75 microns, được phủ lên lớp nền và được sử dụng để tạo kết nối giữa các vi mạch, và các lớp này được nhúng vào một lớp nền hữu cơ..

Khái niệm này tuân theo cùng một ý tưởng trong ELIC được sử dụng trong HDI PCBs, nơi một lớp kết nối mỗi lớp kết nối nhiều vi mạch với các lớp bên trong trong một lớp nền cách điện (hữu cơ). Phần EMIB của gói là một cầu silicon cung cấp các kết nối băng thông cao giữa các chiplet.

Kết Luận

Các chiplet được kỳ vọng sẽ tiếp tục cách mạng hóa các ứng dụng đòi hỏi các thành phần tính toán cao cũng như chức năng đa dạng trong một gói duy nhất. Hiện tại, các sản phẩm này đang nhắm đến các công nghệ tiên tiến như 5G, IoT, ô tô, tính toán biên, hình ảnh y tế, tính toán biên, AI, thiết bị di động và nhiều hơn nữa.

Hôm nay, các nhà sản xuất bán dẫn lớn như Intel, Marvell và AMD đã bắt đầu tham gia vào công nghệ chiplet, và chúng ta có thể mong đợi nhiều công ty khác sẽ khám phá lựa chọn này. Khi một thị trường cho IP chiplet phát triển, tương tự như cách một thị trường đã phát triển cho nhiều thành phần khác, nhiều công ty bán dẫn không sở hữu nhà máy có thể chọn cách tiếp cận bằng việc tạo ra bán dẫn tùy chỉnh thay vì xây dựng hệ thống với các thành phần rời rạc.

Giờ đây, khi Intel, AMD và TSMC đã đồng ý về một tiêu chuẩn chung cho kết nối chiplet, liệu chúng ta có thấy sự phổ biến rộng rãi hơn của những thiết kế này bởi các công ty khác không? Người ta có thể hy vọng một thị trường sẽ phát triển cho những thành phần này vì điều này sẽ khuyến khích nhiều đổi mới hơn ở cấp độ đóng gói ngoài các nhà sản xuất bán dẫn lớn.

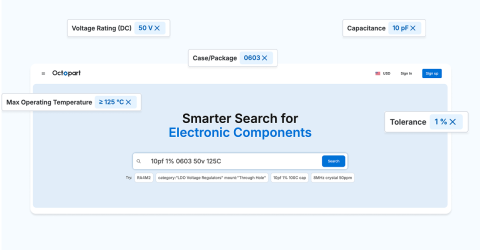

Khi các thành phần dựa trên chiplet với bao bì tiên tiến xuất hiện trên thị trường, các nhà thiết kế hệ thống có thể sử dụng các tính năng tìm kiếm và lọc tiên tiến trong Octopart để tìm tất cả các thành phần tiên tiến họ cần cho các thiết kế tiên tiến. Khi bạn sử dụng công cụ tìm kiếm điện tử của Octopart, bạn sẽ có quyền truy cập vào dữ liệu giá của nhà phân phối cập nhật, hàng tồn kho phần, và thông số kỹ thuật của phần, và tất cả đều dễ dàng truy cập trong một giao diện thân thiện với người dùng. Hãy xem trang mạch tích hợp của chúng tôi để tìm các thành phần bạn cần.

Hãy cập nhật với các bài viết mới nhất của chúng tôi bằng cách đăng ký nhận bản tin của chúng tôi.