Diseño de hardware en tiempos de escasez de memoria: una guía práctica para ingenieros y equipos de abastecimiento

En la primera parte de esta serie, Cómo la IA rompió el mercado de la memoria, analizamos cómo la demanda de los centros de datos de IA convirtió la memoria en un cuello de botella y por qué es poco probable que los precios de la DRAM y la NAND se normalicen rápidamente. Ahora exploraremos cómo operar en este entorno. Si diseñas o abasteces hardware en 2026, aún tienes que tomar decisiones: qué componentes especificar, cómo estructurar tus diseños para ganar flexibilidad y cómo gestionar el riesgo de la cadena de suministro.

Veremos los componentes de memoria de “próxima ola” que vienen en camino y luego pasaremos a algunos componentes DRAM y flash consolidados. A partir de ahí, presentaremos guías prácticas tanto para ingeniería como para compras.

Para una visión general de los componentes de memoria, las páginas de categorías de Octopart para circuitos integrados de memoria y memoria flash son buenos puntos de partida para buscar entre fabricantes, encapsulados y disponibilidad.

Conclusiones clave

- Sepa qué viene y qué está disponible. Los componentes de próxima ola, como LPDDR6 y HBM4, indican hacia dónde se dirigen las plataformas, pero tus diseños de 2026 se enviarán con DDR5, LPDDR5X y NAND madura que hoy sí está en stock.

- Diseña para la sustitución y la flexibilidad. Estandariza interfaces convencionales, homologa familias de componentes y admite múltiples densidades en el firmware. Usa zócalos y módulos cuando sea posible, y planifica opciones de memoria con binning inferior que sigan cumpliendo los objetivos de experiencia de usuario.

- Aborda el riesgo de suministro como un problema de ingeniería. Crea listas de proveedores aprobados (AVL) con múltiples fuentes, asegura asignaciones para líneas críticas y haz seguimiento del ciclo de vida y de las alternativas con herramientas como Octopart.

Componentes de próxima ola que marcan la dirección

LPDDR6 Mobile DRAM de Samsung

Diseñada para IA en el dispositivo, automoción y plataformas móviles y de PC de próxima generación, Samsung’s LPDDR6 ofrece mejoras significativas de eficiencia frente a LPDDR5X, una arquitectura de E/S ampliada y una velocidad inicial de hasta 10,7 Gbps, con el estándar LPDDR6 diseñado para escalar aún más a medida que madure el ecosistema. Todavía no verás LPDDR6 en las estanterías de los distribuidores, pero si diseñas en torno a SoC de última generación o dispositivos insignia, deberías esperar encontrártelo.

HBM4

En la parte más alta de la pila, los dispositivos HBM4 de 16 capas y 48 GB de SK Hynix prometen más de 2 TB/s de ancho de banda, con producción en masa prevista en torno al tercer trimestre de 2026. Samsung está adoptando un enfoque diferente, utilizando lógica de 4 nm y DRAM 1c para mejorar el rendimiento térmico. Los ingenieros que trabajan en hardware de IA normalmente no adquirirán estos componentes a través de distribuidores de catálogo, pero HBM4 importa a todos porque está absorbiendo una gran parte de la capacidad avanzada de DRAM, lo que explica en parte por qué la DRAM convencional sigue tan ajustada.

V-NAND de 10.ª generación de Samsung

Con más de 400 capas y una interfaz de 5,6 GT/s, la V-NAND de 10.ª generación de Samsung apunta a SSD PCIe 5.0 y futuros PCIe 6.0 para cargas de trabajo de centros de datos y de clase IA. Cabe esperar que TLC de alta densidad basada en este silicio sirva de base para muchas unidades empresariales y de cliente de gama alta durante los próximos años.

NAND BiCS10 de Kioxia/Sandisk

Esta BiCS10 de 332 capas con interfaz Toggle DDR 6.0 ofrece 4,8 Gb/s por pin y está orientada a almacenamiento para IA e hiperescaladores. Según EE Times, Kioxia ha dicho que toda su producción NAND de 2026 ya está vendida para aplicaciones relacionadas con IA, y adelantó la rampa de BiCS10 desde la segunda mitad de 2027 a 2026 para satisfacer la demanda.

Productos de memoria consolidados con menos restricciones

Estos componentes estaban disponibles para pedido en grandes distribuidores a principios de marzo de 2026. La disponibilidad cambia rápidamente, así que verifica el stock y el estado del ciclo de vida en Octopart antes de cerrar una BOM.

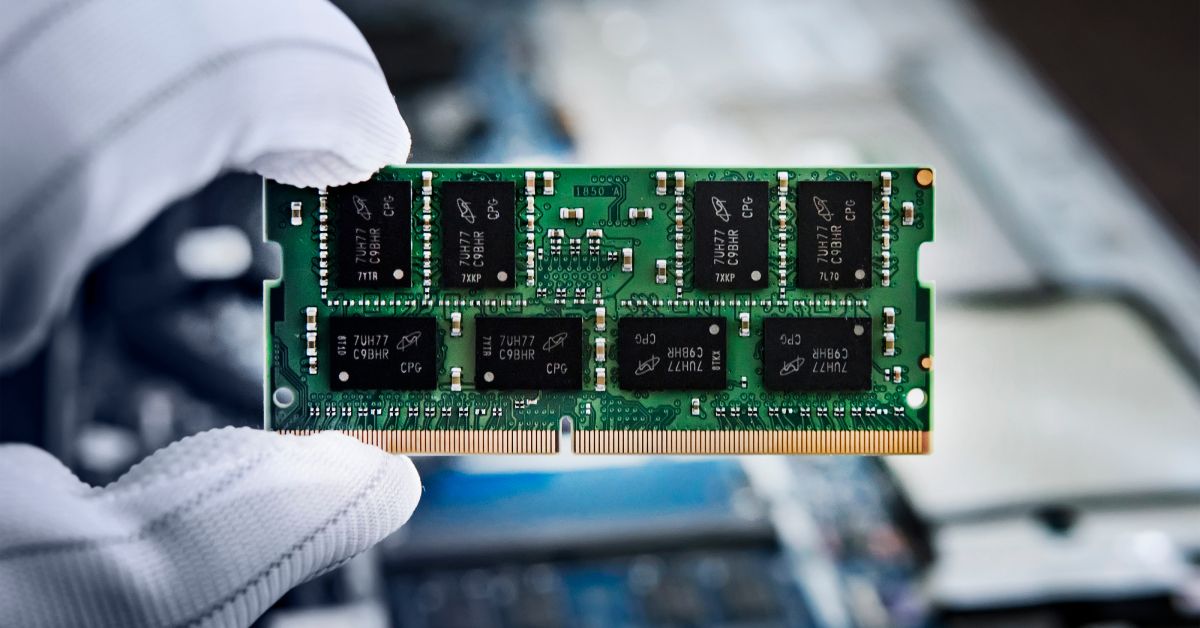

- Apacer D22.31491S.001, SO-DIMM DDR5-4800 de 8 GB. Una opción práctica de DRAM de “vinculación tardía” para diseños que pueden usar un módulo con zócalo, lo que da a compras más margen durante las sustituciones.

- MT60B2G8RZ-56B IT:D, SDRAM DDR5 de 16 Gbit (2G x 8), VFBGA de 78 bolas. Un CI DRAM DDR5 de clase x8 DDR5-5600 convencional que encaja en diseños de memoria personalizados a nivel de placa y ofrece una flexibilidad de segunda fuente más práctica que un SKU de módulo único.

- Macronix MX30LF4G28AD-XKI-TR, NAND SLC de 4 Gbit (VFBGA-63). Una buena opción para diseños NAND industriales y embebidos que necesitan resistencia y comportamiento predecible en una huella BGA compacta.

- Macronix MX60LF8G28AD-TI-T, NAND SLC de 8 Gbit (TSOP-48). Una elección práctica cuando necesitas una huella NAND paralela ampliamente compatible para ecosistemas de controladores maduros y una retrabajabilidad de placa más sencilla que con BGA de paso fino.

- Macronix MX52LM04A11XSI, eMMC 5.1 de 4 GB (BGA-153). Una opción sencilla de NAND gestionada cuando quieres menos dependencias del controlador y una sustitución más limpia que NAND sin procesar más una pila flash personalizada.

- Macronix MX52LM08A11XVW, eMMC 5.1 de 8 GB (BGA-153). Un punto de capacidad práctico para muchos sistemas embebidos Linux y de clase HMI, con las mismas ventajas de interfaz e integración que las piezas eMMC más pequeñas.

- Micron MT40A2G8SA-062E:F, DRAM DDR4 de 16 Gbit (2G x 8). Sigue siendo un componente de gran volumen para muchas plataformas y una opción pragmática de “enviar ahora” cuando DDR5 no es necesaria.

Guía de diseño: cómo los ingenieros incorporan flexibilidad

En este contexto, los ingenieros de hardware todavía pueden tomar muchas medidas para hacer que los diseños sean más resilientes.

- Estandariza interfaces y familias convencionales. DDR5, LPDDR5X, e.MMC, UFS y flash SPI/QSPI tienen ecosistemas profundos y muchas segundas fuentes. Mantenerse dentro de voltajes y encapsulados comunes maximiza el conjunto de componentes compatibles.

- Incorpora flexibilidad en el firmware y en los mapas de memoria. Evita codificar de forma rígida una sola densidad de DRAM o un único tamaño de flash SPI. Admite múltiples geometrías en tu código de inicialización para poder intercambiar alternativas.

- Prioriza memoria no volátil gestionada cuando encaje. e.MMC y UFS ocultan los detalles de gestión de NAND detrás de interfaces estables y a menudo ofrecen rutas de sustitución más claras que la NAND sin procesar ligada a un controlador específico.

- Planifica variantes con binning inferior. Diseña tu software para que las configuraciones con menos memoria sigan ofreciendo experiencias de usuario aceptables, quizá usando menor concurrencia por defecto, conjuntos de recursos más pequeños o escalonado de funciones.

- Usa memoria y almacenamiento modulares cuando sea posible. Los zócalos para SO-DIMM, UDIMM y SSD M.2 permiten definir la configuración más tarde y dan a compras más margen de maniobra. Reserva la memoria soldada para factores de forma restringidos donde realmente sea necesaria.

Guía de abastecimiento: cómo compras puede gestionar el riesgo

La situación exige atención. A finales de febrero de 2026, Lenovo advirtió a sus socios de canal que hicieran pedidos antes de fin de mes para evitar las subidas de precios de marzo, mientras que TrendForce proyectó que la DRAM para PC combinada (DDR4/DDR5) subiría entre un 105 % y un 110 % intertrimestral solo en el primer trimestre. La guía siguiente refleja esta nueva realidad.

- Asegura asignaciones y acuerdos a largo plazo para líneas críticas de DRAM y NAND, especialmente para servidores, equipos de IA y portátiles de gama alta. La inteligencia de mercado de firmas como TrendForce puede orientar cuándo comprometerse.

- Construye listas de proveedores aprobados en torno a familias, no a SKU individuales. Define clases aceptables de módulos, NAND y e.MMC, y trabaja con ingeniería para validar varias opciones por adelantado.

- Segmenta los productos según su sensibilidad a la memoria. Dirige la memoria escasa y cara a los SKU donde más afecta al rendimiento y al margen; aplica controles de costes más agresivos a los dispositivos menos sensibles a la memoria.

- Usa el inventario de memoria como cobertura estratégica para productos de ciclo de vida largo. Mantener un colchón de DRAM o NAND clave puede resultar más barato que rediseñar placas o reescribir firmware a mitad de vida si un componente pasa a estar restringido.

La flexibilidad es la estrategia

En la primera parte de esta serie, explicamos el porqué de la escasez de memoria. Y aquí hemos explorado qué hacer ahora. La respuesta es la misma tanto si eres ingeniero como si trabajas en compras: la flexibilidad es la mejor cobertura. Diseña para la sustitución, homologa ampliamente y usa herramientas como Octopart para mantener tus opciones visibles y actualizadas. Los equipos que saldrán de este ciclo en mejor posición serán los que hayan incorporado opcionalidad en sus diseños y cadenas de suministro desde el principio y sigan adaptándose a medida que evolucionen el suministro y los precios.

Preguntas frecuentes

¿Por qué sigue siendo difícil abastecerse de DRAM y NAND en 2026?

La escasez actual está impulsada por la asignación de obleas, no por límites tecnológicos. Los proveedores de memoria están priorizando la demanda de IA de alto margen, especialmente HBM y DRAM para centros de datos, bajo contratos plurianuales. Como HBM consume significativamente más capacidad de oblea por bit que la DRAM convencional, queda menos capacidad para DDR5, LPDDR y NAND, lo que mantiene la disponibilidad ajustada.

¿Deberían los ingenieros diseñar hoy con memoria de próxima generación como LPDDR6 o HBM4?

LPDDR6 y HBM4 indican hacia dónde se dirigen las plataformas, pero la mayoría de los productos de 2026 se enviarán con DDR5, LPDDR5X y NAND madura que ya está disponible. Los ingenieros deberían diseñar pensando en la compatibilidad futura mientras seleccionan componentes que puedan abastecerse de forma fiable durante la producción, en lugar de apostar por piezas que aún no están en distribución.

¿Cómo pueden hacerse los diseños de hardware más resilientes frente a la escasez de memoria?

Los diseños resilientes se centran en la flexibilidad y la sustitución. Esto incluye estandarizar interfaces convencionales, homologar múltiples densidades y proveedores, evitar supuestos rígidos sobre la memoria en el firmware y usar zócalos o módulos cuando sea posible. Admitir opciones de memoria con binning inferior garantiza que los productos puedan seguir enviándose cuando las piezas de mayor capacidad estén restringidas.

¿Cuál es la mejor manera de que los equipos de compras gestionen el riesgo de suministro de memoria?

Compras debe tratar la memoria como un recurso estratégico, no como un commodity. Entre las mejores prácticas se incluyen asegurar asignaciones a largo plazo para los SKU críticos, construir AVL en torno a familias en lugar de piezas individuales, supervisar el ciclo de vida y las alternativas con herramientas como Octopart, y mantener inventario de forma selectiva para productos de ciclo de vida largo a fin de evitar rediseños forzados.