Proyecto de diseño de PCB para módulo ADC dual

Los ADCs en un PCB son examinados en este proyecto, incluyendo la colocación y el enrutamiento que involucra un ADC aislado.

Haz clic aquí para saltar al incrustado del visor y explorar este proyecto

Si tu placa incluye un ADC, entonces tu placa califica como un sistema de señal mixta y necesitará algunas prácticas de diseño particulares para prevenir el exceso de ruido en las líneas analógicas. Los ADCs normalmente no son componentes aislados, pero también existen en variedad aislada, donde el componente proporciona aislamiento galvánico entre los lados analógico y digital.

En este proyecto, voy a mostrar un diseño de ejemplo que utiliza ambos tipos de ADCs en el mismo diseño de PCB. Estos componentes requieren diferentes prácticas de diseño, pero los implementaremos en la misma placa para proporcionar una buena comparación.

Como es el caso en todos nuestros proyectos, hay un enlace para descargar los archivos fuente de este proyecto al final del artículo. Para aprender más sobre el uso de estos tipos de componentes y seguir todo el proceso de diseño, puedes ver la lista de reproducción a continuación.

Iniciando el Módulo ADC

El módulo ADC que presentaré en este proyecto está destinado a recoger dos señales y pasar los datos a un conector de pines, que luego podría conectarse a una placa externa como un módulo de microcontrolador. El módulo incluirá el siguiente conjunto de componentes principales:

- ISL75051ASEHVFE - Módulo regulador de potencia rad-hard de 5V a 3V3

- ADC128S102CIMTX - ADC de 12 bits y 8 canales, de 0.5 a 1 MSps

- AMC1203BPSA - ADC de corriente aislada sigma-delta de 8 bits y 40 kSps de un solo canal

Las señales que se recogen están destinadas a ser de bajas frecuencias, como lo demuestran sus bajas tasas de muestreo. Ambos ADCs asumen fuentes de baja impedancia, por lo que no necesitamos un filtro activo con un búfer de impedancia, y podemos conectar directamente a las entradas del ADC si se desea. Finalmente, cualquiera familiarizado con los componentes de Intersil notará que el ISL75051ASEHVFE es un regulador rad-hard; este módulo podría usarse en un sistema espacial siempre que los otros dos componentes puedan calificarse para uso aeroespacial.

Esquemas de ADCs Aislados y No Aislados

Las imágenes a continuación muestran las dos partes principales de los esquemas para este módulo: los ADCs aislados y no aislados. Los demás componentes y circuitos se pueden ver en los archivos del proyecto.

Los esquemáticos son simples; solo necesitamos una página para todos los circuitos. Tenemos dos entradas de energía separadas, una para el lado aislado que viene a través de un SMA, y otra para el lado no aislado que viene a través del conector de pines.

Primero, echa un vistazo a los esquemáticos para el ADC aislado (AMC1203BPSA) como se muestra a continuación.

La referencia analógica para este componente se establece internamente, por lo que no necesitamos un chip de referencia de precisión para establecer el rango de medición. Ten en cuenta que el ADC aislado requiere dos redes de energía diferentes (+5V y +5V_AN), ambas a +5V según la hoja de datos; estas deben provenir de fuentes diferentes para asegurar que el aislamiento galvánico se mantenga a través del espacio de aislamiento en este componente. J1 y J3 son los conectores para la señal analógica entrante y la energía de entrada para el lado analógico del ADC.

Para proteger adecuadamente las señales entrantes, las señales que llegan a los ADCs aislados y no aislados se proporcionan usando cable coaxial con conectores SMA verticales (73251-1350 de Molex). Estos conectores y los cables coaxiales adjuntos tendrán una impedancia de 50 Ohms, pero las señales de entrada serán lo suficientemente bajas como para que la única interacción apreciable exista entre la fuente y la carga en el sistema.

A continuación, echa un vistazo al circuito para el ADC estándar.

En este circuito, la energía es suministrada por el regulador (red de 3V3), que a su vez recibe su energía de la conexión de +5V del conector de pines. La salida SPI utiliza una resistencia para reducir ligeramente la tasa de cambio de los bordes antes de enrutar la señal fuera de la placa. También se colocan capacitores específicamente para el desacoplamiento/bypass de los pines VA y VD.

Hay algunas suposiciones en los esquemáticos anteriores:

- La red +5V_AN nunca necesitará alta corriente en esta placa, por lo tanto, usar un cable SMA + coaxial para la alimentación es apropiado. Voltajes/corrientes más altos requerirán componentes diferentes.

- El ancho de banda de la señal de entrada solo está limitado por la tasa de muestreo de cada ADC. Si se necesita un ancho de banda más bajo, añadir un filtro RC de paso bajo y operar a la máxima tasa de muestreo para el anti-aliasing.

- Se asume que la conexión de +5V en el conector de pines está regulada y relativamente libre de ruido. Si no está regulada, será necesario un regulador de +5V en la entrada.

- Los pines VA y VD en U2 no están aislados porque U2 es el único componente que genera bordes digitales rápidos para su interfaz SPI. Si hubiera más componentes en el bus de 3V3, entonces definitivamente querríamos considerar limitar la banda de potencia al pin VA cerca de 1 MHz.

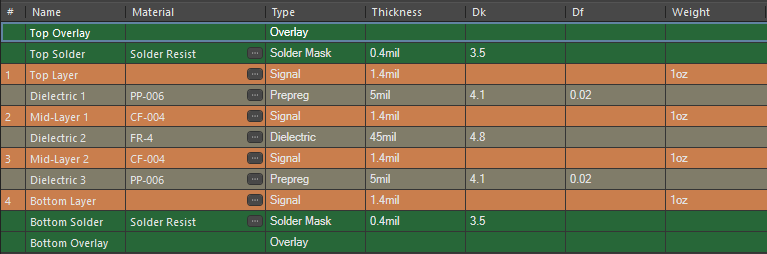

Con estos puntos fuera del camino, podemos proceder al apilamiento. Nuestro apilamiento necesitará soportar 2 interfaces digitales razonablemente rápidas (una para cada ADC) y dos líneas de alimentación separadas hacia los ADCs.

Planificación de la distribución y apilamiento de PCB

Debido a que esta placa contiene un componente aislado, necesita tener un plan de distribución particular que permita una región aislada. Podemos hacer todo en esta placa en una sola capa, pero necesitamos tierra para prevenir el acoplamiento inductivo entre las secciones analógicas y digitales, lo que exige un plano de tierra interno. Por lo tanto, podemos usar un apilamiento de PCB simple de 4 capas con GND interno.

El apilamiento finalizado se muestra a continuación. En este apilamiento, hemos utilizado un apilamiento SIG+PWR/GND/GND/SIG; los componentes estarán en el lado superior y el lado inferior se puede utilizar para enrutamiento adicional según sea necesario.

En este apilamiento, el valor de Dk no es tan importante ya que no tenemos requisitos de impedancia controlada. El punto importante aquí es la capa externa delgada, así como GND en L2 y L3. La capa externa delgada con tierra adyacente es clave para suprimir el ruido, como he señalado en un artículo diferente sobre extracción parasitaria.

A continuación, la sección aislada necesita ser colocada en su propia área con sus conectores SMA proporcionando energía y señal. He aislado esto en el lado izquierdo de la placa, mientras que los componentes restantes se ubicarán en el lado derecho. La colocación inicial se muestra a continuación.

La colocación inicial alinea todas las secciones analógicas en el lado izquierdo de la placa, mientras que el regulador y las líneas de E/S se enrutan directamente hacia el derecho (principalmente en la capa trasera). Esta es una estrategia típica para minimizar el acoplamiento de ruido entre las líneas digitales y las líneas de alimentación analógicas. La barrera de aislamiento corre verticalmente bajo U3, por lo que ahí es donde dividiremos las redes de tierra en GND y AGND para mantener el aislamiento requerido.

Para hacer esta división, he implementado una pequeña región de vertido de cobre que abarca las 4 capas en el PCB. La región proporciona conexiones AGND en J1 y J3, y las capas se conectarán con vías de cosido.

Las conexiones térmicas en los pads SMA serán eliminadas al cambiar las reglas de diseño. Utilizo una estrategia similar en la sección no aislada, pero con la diferencia de que el vertido en L2 corre bajo toda la conexión del ADC. También agregaré vías de cosido a esa sección para la supresión de ruido. Con este punto completado, ahora podemos enrutar el resto de las conexiones.

Un punto que me gustaría señalar aquí es la colocación de los capacitores. Al igual que ocurre con un componente digital, es importante colocar cualquier capacitor que suministre energía al pin de alimentación analógico cerca de esos pines. De esta manera, el subsistema analógico podrá extraer suficiente energía dentro de su intervalo de muestreo y habrá un mínimo dropout para cualquier referencia interna. A continuación, se muestra un ejemplo. Específicamente, hemos colocado C18 y C19 para la alimentación digital, y C16 y C17 para el lado analógico.

Enrutamiento y Diseño Finalizados

Después de algunos cambios en los componentes, pude mover los capacitores grandes (C9 y C13) para que se ubicaran más en el centro de la placa. Esto me permite reducir algo el tamaño de la placa para que no tengamos una gran área abierta sin componentes ni ruteo. Luego, en L2 y L3, he distribuido tierra por todas partes para mantener la distribución de cobre en el apilado mayormente simétrica. El ruteo finalizado, con vías de conexión incluidas, se muestra a continuación.

En esta vista, puedes ver la entrada de +5V y la salida de +3V3 ruteadas como polígonos grandes, mientras que los otros polígonos en la capa superior son GND o AGND. Todos los señales digitales están ruteadas en la capa inferior excepto en los puntos donde necesitan conectarse a los ADCs en L1.

Una vista 3D del diseño finalizado de la PCB se muestra en la imagen a continuación. Como es habitual, tenemos algunos logotipos, así como una leyenda de serigrafía para el pinout en el conector de pines. Los SMA colocados en el lado izquierdo tienen vías de conexión para unir esa región de tierra en todas las capas y para prevenir que la interferencia RF errante se propague en esa porción del sustrato. Estas líneas también no están diseñadas a una impedancia específica, y la suposición aquí es que las señales de entrada serán de frecuencias tan bajas que las líneas de alimentación son eléctricamente cortas.

¿Qué más podemos añadir a este módulo?

El diseño mostrado arriba está pensado para interactuar con un módulo microcontrolador externo para recopilar y procesar los datos a través del conector de pines. Para continuar desarrollando esta placa, se podría colocar una sección digital con un microcontrolador en la capa trasera, donde el microcontrolador acepte datos proporcionados por las salidas de los ADCs. Un microcontrolador pequeño como PIC (de Microchip) o un STM32 más pequeño (ST Microelectronics) sería apropiado para este módulo.

El diseño, tal como está ahora, asume una baja impedancia de fuente y no incluye filtrado para limitar el ancho de banda de la señal recogida por el dispositivo. Esto ya está limitado por la tasa de muestreo basada en la tasa de muestreo de Nyquist, pero las señales de baja frecuencia podrían ser sobremuestreadas y pasadas a través de un filtro anti-aliasing RC para reducir aún más el ruido.

Si utiliza un microcontrolador en la capa trasera, es probable que tenga su interfaz de salida para enviar datos a otro dispositivo, como una computadora. Esto podría hacerse a través de una interfaz UART, o directamente a través de USB. La opción UART es útil ya que podría entonces ser enrutada a un conector de 2 pines, que luego se conectaría al dispositivo de destino. Debido a que muchos microcontroladores tienen una opción UART, el próximo proyecto que presentaré será un módulo conversor de UART a USB que podría aceptar datos de un microcontrolador como he descrito aquí.

Siga este enlace para descargar un archivo ZIP con los archivos fuente del proyecto. También puede usar el enlace de descarga en el incrustado anterior para acceder a los archivos fuente.

Los componentes de alta densidad con secciones de RF son fáciles de colocar y enrutar con el conjunto completo de utilidades CAD en Altium Designer®. Cuando haya terminado su diseño y quiera liberar los archivos a su fabricante, la plataforma Altium 365™ facilita la colaboración y el compartir sus proyectos.

Solo hemos arañado la superficie de lo que es posible con Altium Designer en Altium 365. Comienza tu prueba gratuita de Altium Designer + Altium 365 hoy.