Parasitic Extraction with an Electromagnetic Solver in PCB Routing

Parasitic extraction: the integrated circuit design community must grapple with this task on a daily basis, especially once gate features are reduced below ~350 nm and chips run at high switching speeds. The PCB community also has to deal with this idea in order to better design power delivery networks, interconnects with precise impedance, and properly quantify crosstalk and coupling mechanisms. There are many 3rd party applications that can be used to extract parasitics from your layout for specific geometries, but the results from these tools are impractical for use in most design software.

Why worry about parasitics in a PCB and how can we deal with these in the design process? Intentional and unintentional parasitics are entirely responsible for signal and power behavior in a PCB. When you're calculating impedance, you're really calculating two important parasitics and you're using these as part of the routing engine. You can also use these values for things like crosstalk prediction, power simulations involving transients and ringing, or even coupling of ESD pulses into exposed traces.

Parasitic Extraction for Your Traces

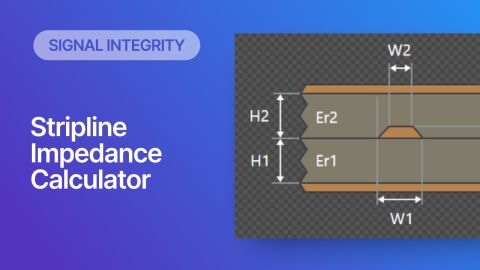

The PCB stackup you create will partially determine the parasitics that affect your conductors. You actually don't need a complex field solver to determine parasitics that arise in the PCB layout around specific traces. The traces you place in the PCB layout will have some natural parasitic capacitance and inductance that determines their impedance. However, if you bring some copper near a trace, their will be some additional mutual capacitance and inductance that will modify the impedance of the trace. It's actually possible to determine these parasitic values using impedance calculator tools, as well as some analytical formulas in the literature or field solver utilities (Ansys, COMSOL, etc.).

For a single trace on a PCB (regardless of its width), you can get the parasitic capacitance and inductance through two methods:

- Direct calculation, requiring a field solver or some complex analytical formulas found in journal articles

- Calculation through comparison, which involves comparing parasitic-free impedance calculations with couple trace impedance calculations

The first point, direct calculation, is very powerful and requires some expensive software. You can also find formulas for specific structures in the literature, but these are often very complex formulas that involve potentially dozens of parameters. Mutual coupling formulas for different structures also have very little generalization.

The second point, determination via comparison, is actually relatively simple if you have the formulas available, it's simply a matter of comparing impedance values from different calculators. This is basically what I did in a previous article on clearance between copper pour and 50 Ohm impedance microstrips/striplines; by comparing the impedance values for a specific width, it's possible to determine when parasitics create a noticeable effect on impedance.

In the next sections, I'll take a similar approach, but I'll use the field solver in Altium Designer to generate results. Using the results from single-ended trace impedance calculations, and then comparing these with other trace impedance calculations, you can quickly extract the values of parasitics with some simple formulas.

The Method

The method here is simple and relies on comparing impedance calculations for an isolated trace with the impedance calculation for a trace with parasitics. In this way, you can then calculate the values of the parasitics, which are just mutual capacitance and inductance. Note that in this example, we're using the lossless impedance as this is the value returned in Altium Designer. However, it does give you a very accurate estimate of parasitics up to GHz frequencies.

Note that any calculator application (such as the calculators I created in some other blogs) or the Layer Stack Manager in Altium Designer will only return L or Lp. Since the numerator is the propagation constant, we now have 2 equations and 2 unknowns, so the system can be solved to get the parasitics. This model was derived from the Telegraphers equations assuming a plane or nearby trace to the line in question, where the nearby conductor is held quiet.

You can find the values of L or Lp from the Impedance tab when you create an impedance profile in the Layer Stack Manager. This is shown below, where we are comparing a microstrip with a coplanar microstrip; both have the same width. Making this comparison allows us to determine exactly how much parasitic capacitance is introduced by the presence of nearby ground pour.

What this result shows is that a 14.423 mil wide microstrip on an 8 mil substrate with Dk = 4.2 that is placed 8 mil away from a nearby plane will have 64.5 fF of parasitic capacitance and 755 pH of parasitic inductance introduced by the nearby plane. This is much faster than using something like mutual and self impedances (Z-parameter matrix) for a trace and some other structure.

Single Trace Near a Plane

This involves a comparison between a single trace and a coplanar line impedances with the following procedure:

- Select a substrate thickness and trace width for a microstrip or stripline. Note the inductance and capacitance values.

- Set up the same trace with a coplanar line. Select a large spacing to the ground pour start. Note the inductance and capacitance values.

- Adjust the ground pour spacing and calculate the impedance.

- Use the data from 3 and the equations above to calculate the mutual impedance and capacitance.

- Go to Step 1 and repeat for a new substrate thickness/Dk value.

As you iterate through a series of values according to Step 5, you can build a graph that shows the mutual capacitance inductance values, as I've done below.

The graph below shows microstrip results for an 8 mil and 4 mil thick substrate with Dk = 4.2; the corresponding trace widths are 14 mil and 7 mil, respectively. The idea here was to maintain the same W/H ratio as this value is mostly responsible for setting the impedance of a trace. From the graph below, we can immediately see that the thinner substrate provides much lower parasitic capacitance, thus we expect much lower high-frequency crosstalk.

See if you can continue on this process of parameter variation to extract more trends for different substrate thickness values and trace widths. The results here could also be implemented for striplines, both symmetric and asymmetric.

Here, there is a clear solution to the problem of excess parasitic capacitance back to the nearby grounded copper pour region: use a thinner dielectric. Note that the effects on parasitic inductance becomes almost independent of spacing to the ground pour when spacing gets small, illustrating that ground pour is not so useful at suppressing lower speed crosstalk, but it might be much more useful for suppressing high-frequency noise.

Single Trace Near Another Trace (Same Widths)

For coupled lines, you can also get a mutual capacitance and inductance value between two traces. However, note that the model above deals with single-ended traces, whereas we are working with a differential model, thus we have to reduce the returned differential impedance by a factor 2 before solving our simultaneous equations to get the parasitics. In the below results, I used the same two substrate types for microstrip traces (again, Dk = 4.2) and iterated through trace separation to determine the parasitics. Note that this was not performed using spacing to any grounded copper pour (not coplanar).

As with the case of a single-ended microstrip, you could apply the same type of model and procedure to striplines. We see much higher mutual inductances as we would expect for narrower sections of conductor.

How do these values change if we were to use a lower Dk PCB laminate, such as a Rogers PCB material? In th graph below, I've run the above set of simulations again with the impedance tool in Altium Designer and transmission line impedance calculations assuming one quiet line, but I've done this assuming a Dk = 3 laminate. Because the Dk value is lower, we might expect two outcomes:

- Reduction in mutual capacitance because the laminate Dk value is lower

- Assuming we target the same impedance, we would expect lower mutual inductance

This is exactly what we see in the results below. The graph below shows the mutual capacitance and mutual inductance between two traces on a Dk = 3 PCB laminate material. Here we can see why some advanced systems employing signals with very fast edge rates tend to opt for a lower Dk laminate. The lower Dk value will provide lower mutual inductance for a given impedance. The results below only show microstrips, but we would expect to see similar results in striplines.

With striplines, reducing parasitic capacitance between two traces by simply changing the Dk and thickness, yet keeping the trace width constant, will give the same results. However, in microstrips, this is not quite the same straightforward trend. The reason for this is because of the classic effective Dk result that determines microstrip impedance. This creates a nonlinear dependence between the effective Dk value, the trace width, and the thickness of the dielectric:

This means that, as soon as you change the Dk value in your microstrip layer, and then you change the substrate thickness to maintain the same trace width, you may not see the expected reduction in parasitic capacitance or inductance. However, if you performed the same on striplines, we would not have this complication.

Despite the slight complication with microstrip traces, the following results generally hold:

- Reducing the distance to ground reduces trace-to-trace parasitics

- Reducing the Dk value surrounding the traces while maintaining the same impedance reduces the trace-to-trace parasitics

For advanced designs, where we require low crosstalk up to many GHz bandwidths, this should show that a simple stackup change can help with crosstalk reduction.

Parasitics and Signal Integrity

As we proceed through these points on interconnect design and determining acceptable trace density limitations, I'll use some of these results to analyze crosstalk in some upcoming articles. This comparison method is simple but powerful, and it can help you examine the level at which parasitics will start to create a bandlimiting effect in high-speed/high-frequency traces.

Aside from impedance and crosstalk, the other area where parasitics matter is in routing, specifically in differential pairs and high frequency signals. Parasitics affect signals in two ways:

- Skew in differential pairs: Parasitics (mostly capacitance) on one line will decrease the signal velocity relative to the other line, causing excess skew. This could cause the edge rates of each polarity signal to become misaligned if skew is excessive.

- Phase response in RF signals: A change in the propagation constant due to parasitics can create a change in the phase response of an interconnect. This is important in edge-coupled waveguides, surface-layer emitters, any circuit that relies on resonance to define its transfer function, and any of these elements arranged in a series cascade. This is a much more advanced topic I teach in my high frequency interconnect design class, but I'll create more articles about this in the future.

For digital signals carried on differential pairs, the solution is simple: maintain symmetry of and around the trace, and enforce length matching. Although length matching does not have to be perfect, CAD tools make it really easy to get close to perfect. There should always be some level of length matching enforced to ensure signal edge rates remain synchronized at the receiver. You'll notice the impedance calculator also gives a calculation of propagation delay that includes parasitics so that delay tuning can be performed. Time-based length tuning (a.k.a. delay tuning) ensure you always have an accurate length matching structure applied in your PCB layout.

The interactive routing and layer stackup creation features in Altium allow you to perform a range of parasitic extraction tasks. Simply use the built-in electromagnetic field solver in the Layer Stack Manager for various trace geometries and follow the steps above to determine parasitics to other traces or planes. When you’re ready to release your board fabrication files and drawings to your manufacturer, Altium makes it easy to collaborate and share your projects.