Cómo la IA rompió el mercado de la memoria: dentro de la escasez de DRAM y NAND de 2024–2026

Conclusiones clave

- Los centros de datos de IA se han convertido en el principal cliente del silicio de memoria, impulsando cambios en la asignación de obleas en DRAM, HBM y NAND al mismo tiempo.

- Este ciclo de oferta y demanda es diferente. La expansión limitada de las fábricas, la producción de NAND prácticamente agotada y los contratos plurianuales de HBM significan que la escasez probablemente persistirá hasta finales de 2027–2028.

- Los diseños heredados y embebidos son daños colaterales. DDR3, las primeras DDR4 y la NAND SLC enfrentan un mayor riesgo de EOL, plazos de entrega más largos y precios impredecibles, ya que los proveedores priorizan la memoria para IA de alto margen.

El giro inesperado de la memoria: de componente secundario a cuello de botella

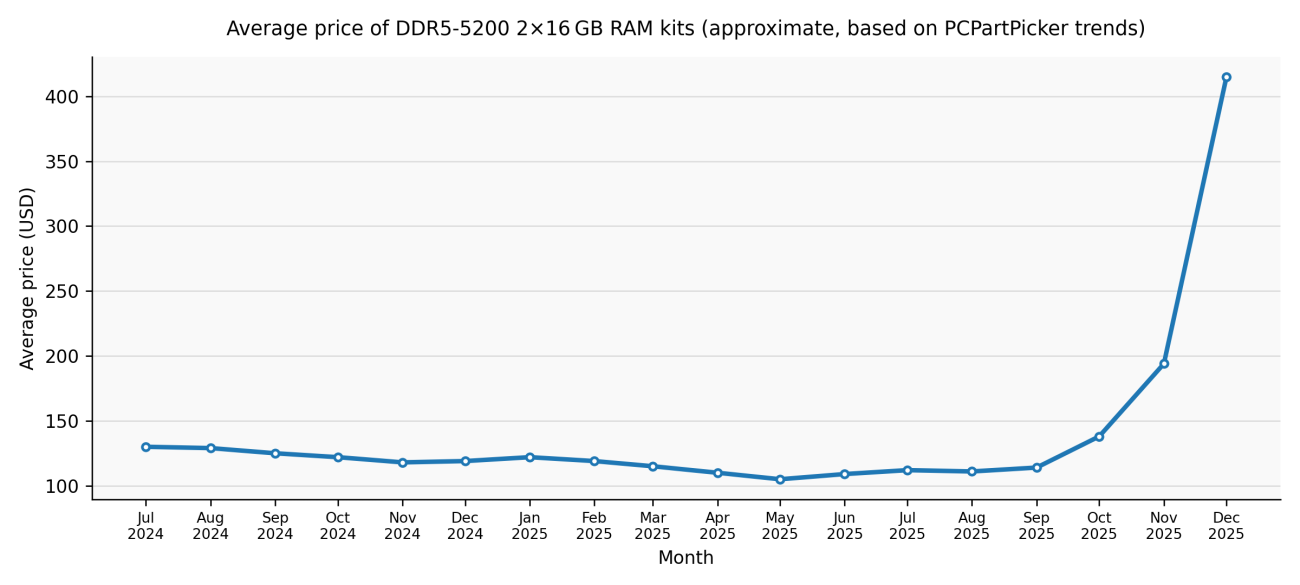

Durante la mayor parte de la era del PC, la memoria quedó en segundo plano. Entre 2024 y 2026, esa dinámica cambió por completo. La memoria se convirtió en la principal restricción del diseño de sistemas, y el costo de “simplemente añadir más RAM” aumentó bruscamente en apenas unos pocos trimestres.

Los precios han subido, la disponibilidad se ha reducido y los productos se envían cada vez más con la cantidad mínima de memoria, en lugar del margen holgado al que estábamos acostumbrados. Está en marcha un reequilibrio estructural sobre quién recibe las obleas y por qué.

Entonces, ¿qué cambió realmente y por qué esta escasez se siente distinta de las anteriores? Aquí lo analizaremos, en la primera parte de una serie de dos artículos que cubre las fuerzas que están alterando el suministro de memoria, desde los servidores en la nube hasta los sistemas embebidos. La segunda parte, Diseño de hardware en tiempos de escasez de memoria, profundiza en los componentes de memoria de próxima generación que apenas están entrando en producción, los productos de referencia líderes que puedes pedir hoy a tu distribuidor, patrones de diseño y tácticas de abastecimiento.

Cómo los centros de datos de IA reconfiguran el panorama de la demanda

En ciclos anteriores, la demanda de memoria estaba ampliamente distribuida entre PCs, teléfonos, servidores y electrónica de consumo. La oferta y la demanda se desalineaban, los precios subían o bajaban, y luego todo volvía a la normalidad a medida que las fábricas se ajustaban. La escasez de 2024–2026 no está siguiendo ese guion.

La diferencia está en quién compra. Los centros de datos centrados en IA ahora dominan el panorama de la demanda, y sus clústeres de entrenamiento y granjas de inferencia necesitan enormes cantidades de memoria de alto ancho de banda (HBM) y DRAM convencional por GPU o acelerador. La HBM consume significativamente más capacidad de oblea por bit que la DRAM estándar, lo que la hace extremadamente atractiva para los fabricantes que buscan asegurar contratos plurianuales y de alto margen con proveedores de infraestructura de IA.

Algunos analistas estiman ahora que los centros de datos consumirán hasta el 70 % de todos los chips de memoria de gama alta producidos en 2026, una fuerte inversión respecto a la época en que los dispositivos de consumo representaban la mayoría de esos chips. En este entorno, la memoria para PC y móviles pasa a ser un negocio secundario, mientras que los centros de datos de IA se convierten en el evento principal.

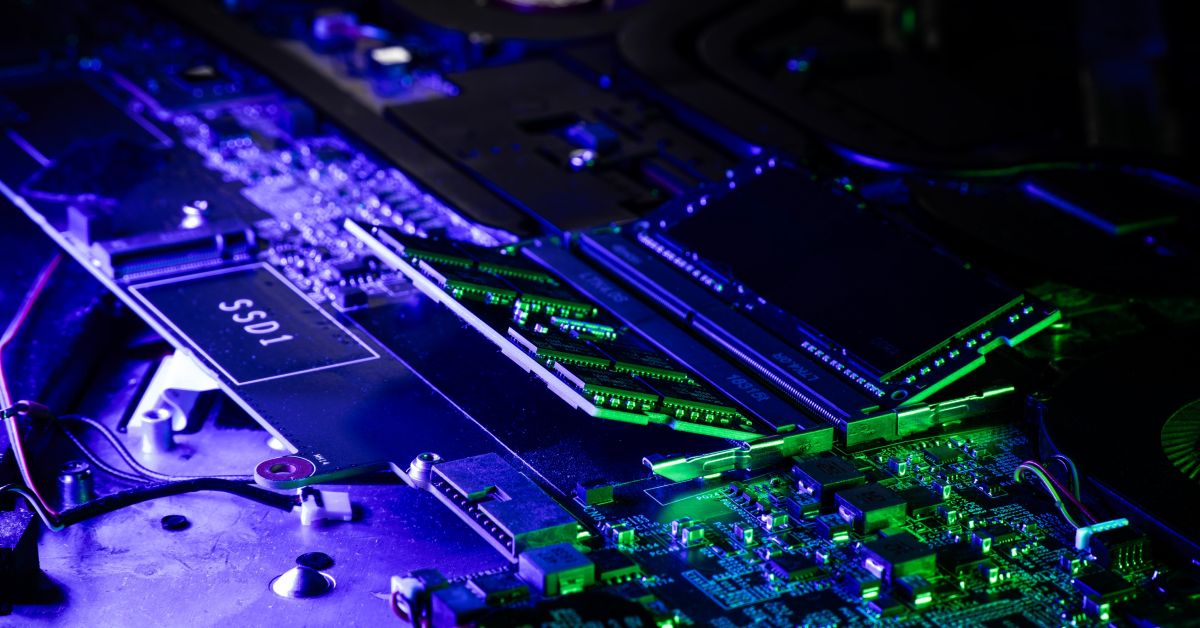

La generación HBM4 presentada en CES 2026 ilustra la magnitud de este cambio. SK Hynix mostró un dispositivo de 16 capas y 48 GB que ofrece más de 2 TB/s, aumentando significativamente el rendimiento de la HBM3 inicial utilizada en la primera ola de aceleradores de IA generativa. Cada oblea que se destina a estas pilas deja de producir DDR5 para tu próximo PC o LPDDR5X para un teléfono.

Diseños embebidos y heredados: presionados lateralmente

Los diseños embebidos e industriales, que a menudo dependen de estándares DRAM más antiguos o de NAND SLC madura, enfrentan sus propios desafíos. Muchos de estos productos utilizan DDR3 o las primeras DDR4, junto con memoria flash NAND paralela, que ya no ocupan un lugar central en las hojas de ruta de los proveedores.

A medida que los fabricantes priorizan la HBM de alto margen y la DRAM de clase servidor, están reduciendo o descontinuando las líneas heredadas. Lo que queda mantiene precios inesperadamente altos y plazos de entrega más largos, aunque la tecnología en sí sea madura.

Seguir de cerca el estado del ciclo de vida de los componentes con herramientas como Octopart ayuda a los equipos a detectar anuncios de EOL y restricciones de suministro antes de que se conviertan en emergencias.

Progreso bajo presión: DDR5, LPDDR6, NAND y HBM4

Las mismas transiciones tecnológicas que están dejando sin suministro a los diseños más antiguos están produciendo verdaderos avances de ingeniería. Comprender ambos lados de esta dinámica es importante porque los avances están cambiando lo que hay disponible para diseñar, mientras que la economía de las obleas que hay detrás explica por qué la memoria de uso general no será más barata en el corto plazo.

DRAM

Samsung está produciendo en masa la DRAM LPDDR5X de clase 12 nm más delgada para dispositivos móviles de próxima generación, combinando alto rendimiento con eficiencia energética y encapsulados delgados adecuados para teléfonos premium y equipos ultraportátiles. Las primeras piezas LPDDR6 llevan aún más lejos el ancho de banda y la eficiencia energética, apuntando a aplicaciones de IA en el dispositivo y automoción. La implementación LPDDR6 de Samsung ha ido ganando reconocimiento en eventos del sector, lo que indica hacia dónde se dirige la memoria móvil de gama alta.

HBM

En el extremo HBM del espectro, la cobertura de CES 2026 sobre HBM4 muestra que las pilas de memoria se están convirtiendo en subsistemas altamente integrados. Las pilas de 16 alturas de SK Hynix utilizan MR-MUF y obleas DRAM ultrafinas para mantenerse dentro de los límites de altura de JEDEC, mientras que Samsung apunta a su lógica de 4 nm (que comenzó la producción en masa en febrero de 2026) para mejorar la gestión térmica y la eficiencia energética. Todo ese esfuerzo de ingeniería y capacidad de obleas está claramente dirigido a los aceleradores de IA.

NAND

En el lado de NAND, los proveedores están apilando cada vez más capas. La V-NAND de décima generación con más de 400 capas e interfaces de alrededor de 5,6 GT/s se está incorporando en SSD PCIe 5.0 y futuros PCIe 6.0 para casos de uso de centros de datos e IA. La BiCS NAND de décima generación y 332 capas de Kioxia y Sandisk, que utiliza la interfaz Toggle DDR 6.0 a hasta 4,8 Gb/s por pin, demuestra cuánto ha avanzado la NAND de alto ancho de banda para SSD de centros de datos y clase empresarial.

La tecnología avanza, pero la capacidad no sigue el mismo ritmo. Según EE Times, Samsung y SK Hynix redujeron la producción de obleas NAND en 2024–2025 mientras apostaban por HBM y DRAM, y no han anunciado nueva capacidad NAND a pesar de controlar más de la mitad del mercado. Los datos de Omdia muestran que las obleas NAND de Samsung cayeron de 4,9 millones (2024) a 4,68 millones (2025), y las de SK Hynix de 1,9 millones a 1,7 millones.

Al mismo tiempo, la NAND se ha vuelto crítica para la inferencia de IA. A medida que la IA pasa del entrenamiento al servicio, los SSD respaldados por NAND de muchas capas son cada vez más el principal almacenamiento para los pesos de los modelos y los datos de trabajo. La dirección de Kioxia ha dicho que toda su producción NAND de 2026 ya está agotada, que BiCS10 se adelanta de la segunda mitad de 2027 a 2026 y que, en el futuro, casi la mitad de su demanda de NAND podría provenir de aplicaciones de IA. Especialistas en NAND como Kioxia y el negocio Sandisk, ahora independiente, antes vistos como actores rezagados en un mercado comoditizado, de repente están posicionados como ganadores del auge de los SSD para IA.

Por qué no llegará la recuperación habitual

Los analistas del sector señalan un crecimiento relativamente modesto de la oferta de DRAM y NAND hasta 2026 en comparación con las normas históricas. Mientras tanto, la demanda no cede. Las nuevas arquitecturas de modelos, las cargas de trabajo de inferencia y los despliegues de IA en el edge siguen elevando los requisitos de memoria en lugar de permitir que se estabilicen. Los proveedores de HBM4 están dedicando una capacidad sustancial de obleas a los requisitos de Nvidia y otros aceleradores y, como mencionamos en la sección anterior, proveedores de NAND como Kioxia ya tienen agotada su producción para 2026.

En diciembre de 2025, Micron mostró la naturaleza estructural de este cambio al anunciar su salida de su negocio de consumo Crucial para apoyar mejor a “clientes estratégicos más grandes”. Algunos proveedores, incluido Micron, han declarado públicamente que no esperan que la escasez de RAM para consumidores se alivie de forma material hasta alrededor de 2028, cuando se prevé que la nueva capacidad y las transiciones de proceso alcancen plenamente su ritmo de producción. La misma lógica se aplica cada vez más a la NAND: la inferencia de IA está absorbiendo el suministro futuro de clase SSD tan rápido como los proveedores pueden ponerlo en línea.

En diciembre de 2025, IDC caracterizó la escasez como “no solo una escasez cíclica, sino una reasignación estratégica potencialmente permanente de la capacidad mundial de obleas de silicio”. En febrero de 2026, TrendForce revisó fuertemente al alza su previsión del precio contractual de la DRAM convencional para el primer trimestre de 2026, desde una estimación previa de 55–60 % hasta 90–95 % intertrimestral. Dentro de ello, se proyectó que la DRAM para PC (mezcla de DDR4/DDR5) subiría 105–110 % intertrimestral, un nuevo récord trimestral.

Qué sigue: de la comprensión a la acción

En Diseño de hardware en tiempos de escasez de memoria, analizamos siete componentes de memoria de nueva ola que están entrando en diseños OEM y de centros de datos, ocho productos DRAM y flash de referencia fácilmente disponibles en los principales distribuidores, y estrategias concretas para trabajar dentro de estas limitaciones.

Preguntas frecuentes

¿Por qué hay escasez de memoria aunque la tecnología DRAM y NAND siga mejorando?

La escasez actual no está impulsada por límites tecnológicos, sino por la economía de asignación de obleas. Una proporción creciente de la capacidad mundial de obleas de memoria se está redirigiendo hacia memoria para IA de alto margen, especialmente HBM para aceleradores de centros de datos. Debido a que la HBM consume significativamente más área de oblea por bit utilizable que la DRAM convencional, cada oblea comprometida con la producción de HBM reduce la producción de DDR4, DDR5, LPDDR y NAND. Con una expansión limitada de nuevas fábricas y contratos de suministro de IA a largo plazo que bloquean la capacidad, las mejoras en densidad de memoria no se traducen en una mayor disponibilidad para los mercados generalistas o embebidos.

¿Por qué esta escasez de memoria se siente diferente de los ciclos anteriores?

A diferencia de los ciclos anteriores de auge y caída, esta escasez está determinada por una concentración estructural de la demanda más que por un sobreconsumo temporal. Las cargas de trabajo de entrenamiento e inferencia de IA siguen aumentando los requisitos de memoria, mientras que los proveedores han limitado deliberadamente el crecimiento de la capacidad. Los contratos plurianuales de HBM, la producción NAND agotada para 2026 y las orientaciones explícitas de los proveedores que apuntan a un alivio solo después de 2027–2028 significan que se trata de una reasignación de larga duración, no de un desequilibrio a corto plazo que se corregirá por sí solo únicamente mediante los precios.

¿Qué riesgos crea esto para los diseños embebidos y heredados que utilizan DDR3, DDR4 temprana o NAND SLC?

Los productos de memoria heredados son tratados cada vez más como no estratégicos por los principales proveedores. A medida que los fabricantes priorizan la DRAM avanzada y la HBM, los nodos de proceso más antiguos enfrentan tiradas de producción cada vez menores, cantidades mínimas de pedido más altas, plazos de entrega más largos y un mayor riesgo de fin de vida útil. Incluso cuando los componentes siguen técnicamente “en producción”, los precios se vuelven volátiles y la disponibilidad impredecible. Para los equipos de sistemas embebidos, esto aumenta la importancia de supervisar el ciclo de vida, contar con múltiples fuentes de suministro y planificar rediseños mucho antes en el ciclo de vida del producto que en generaciones anteriores.

¿Cuándo deberían esperar los ingenieros que se normalicen los precios y la disponibilidad de la memoria?

Según las declaraciones de los proveedores y las previsiones de los analistas, es poco probable que haya un alivio significativo antes de finales de 2027 o 2028. Están previstas nuevas ampliaciones de capacidad, transiciones de proceso y expansión de las líneas de encapsulado para HBM y NAND avanzada, pero tardarán varios años en entrar en operación. Al mismo tiempo, las cargas de trabajo de inferencia de IA están ampliando la demanda tanto de DRAM como de NAND de clase SSD, absorbiendo gran parte de esa capacidad futura. Los ingenieros deberían planificar sus diseños partiendo de la base de que la memoria seguirá siendo un coste del sistema limitado y de alto impacto durante el resto de esta década.