¿Qué son los chiplets y cómo se utilizan en el empaquetado?

Los chiplets son pequeños dados de CI con funcionalidad especializada. Están diseñados para combinarse y formar un circuito integrado más grande, siguiendo la tendencia de la industria de semiconductores hacia la integración heterogénea. La capacidad de seleccionar de un conjunto de chips pequeños y altamente especializados, y luego combinarlos para producir una funcionalidad general deseada, es un gran avance respecto al enfoque tradicional de sistema en chip (SoC) para el empaquetado de semiconductores. Los principales proveedores han producido procesadores de computadora que combinan un número selecto de chiplets, en lugar de seguir la ruta tradicional de fabricación de semiconductores monolíticos, donde el dispositivo se fabrica en una sola pieza de silicio.

Aunque la idea de los chiplets ha existido durante décadas, el empaquetado basado en chiplets está impulsando nuevos tipos de componentes, productos y sistemas para aplicaciones especializadas. Estos componentes están adaptados para aplicaciones específicas, y más empresas están entrando en el juego del diseño de chips con un enfoque en los chiplets como su procesador central. Basado en el número de trabajos de investigación, solicitudes de patentes y artículos técnicos que encontrarás en línea, está claro que los componentes basados en chiplets han llegado para quedarse.

Si eres un diseñador de sistemas y estás evaluando opciones de procesadores, es posible que no te des cuenta de que los chiplets constituyen la base de tu sistema. Sin embargo, los chiplets son la columna vertebral que permite la diversa funcionalidad encontrada en los chips modernos, y el concepto de empaquetado continúa impulsando la integración de nuevas características en los diseños de chips. Ejemplos incluyen la integración de bloques FPGA y bloques aceleradores de IA en el mismo paquete que memorias, una CPU e incluso componentes RF.

¿Por qué Chiplets?

El costo y el rendimiento son los dos problemas más apremiantes en el diseño y fabricación de chips. Los últimos años han visto cómo la escalabilidad de Dennard y la Ley de Moore se han ralentizado, resultando en lapsos de tiempo más largos entre nodos de tecnología de proceso. Además, la integración de transistores en un chip monolítico se está volviendo cada vez más desafiante ya que hay pocas opciones disponibles para la escalabilidad del dispositivo. Estos desafíos han disminuido el ROI para los semiconductores monolíticos debido a procesos de fabricación más costosos.

La única manera de aumentar el número de unidades funcionales integradas con el mismo tamaño de transistor es expandir el área del chip, ya sea en el plano del dispositivo o verticalmente. El problema de aumentar el área del chip es que los chips más grandes son más susceptibles a defectos de fabricación, lo que limita el rendimiento de obleas y aumenta el precio de los productos entregados a los clientes. En consecuencia, los chips monolíticos son cada vez más incapaces de proporcionar el rendimiento deseado a la luz de las crecientes demandas de computación.

Por lo tanto, para apoyar aplicaciones de alta computación como IA/ML en dispositivo, redes ultrarrápidas, fusión de sensores y dispositivos móviles de próxima generación, hemos visto la aparición de sistemas basados en chiplets para el desarrollo rentable de electrónica de alto rendimiento. Esto ha abarcado desde SoCs avanzados hasta procesadores de escritorio/servidor y GPUs.

Superando la "Muralla de Área"

El problema de la "muralla de área" es el resultado de una discrepancia entre la necesidad de chips de gran área por parte de los sistemas de computación de alto rendimiento y el bajo rendimiento de la fabricación de semiconductores. La muralla de área se refiere a este desafío en la fabricación de semiconductores monolíticos, donde se utilizan chips más grandes para aumentar la densidad de características, pero el conteo de defectos también aumenta. A medida que las capacidades de procesamiento de fabricación avanzan hacia nodos más avanzados, el rendimiento del proceso disminuye, y por lo tanto, el costo para el cliente final aumenta. Por lo tanto, siempre hay una motivación para desriesgar la fabricación de estos productos eliminando las posibilidades de defectos.

Una solución a la muralla de área reduciría el costo total de un producto final al reducir el desperdicio durante la fabricación. Los chiplets esencialmente diversifican el perfil de riesgo de un producto al distribuirlo a través de múltiples dados de semiconductores. El resultado final es una reducción de costos y la capacidad de diversificar enormemente la funcionalidad en una medida mucho mayor que en un componente monolítico.

Reducción de Costos

Varios chiplets se combinan con técnicas especiales de empaquetado para formar un IC más grande como alternativa a una estructura monolítica. Dado que los chiplets se fabrican en un área menor, generalmente en obleas circulares, el impacto de los defectos de fabricación se reduce y la utilización del área aumenta. En consecuencia, el costo se reduce porque el rendimiento de la oblea es significativamente más alto cuando se utilizan chiplets para crear un componente.

La integración heterogénea es otra ventaja significativa de los chiplets, particularmente en términos de reducción de costos de diseño y producción de IC. Cada chiplet puede ser fabricado usando diferentes nodos de proceso, algo que AMD reveló que se hizo con su producto Ryzen 7. Otro ejemplo de AMD es una patente reciente para una GPU basada en chiplets; la arquitectura para este sistema se muestra en la obra de arte original a continuación:

Varios materiales (por ejemplo, chiplets de GaN y Si) también pueden combinarse en el mismo paquete con este enfoque. El uso de diferentes nodos de tecnología de proceso reduce el riesgo general incorporado en el producto; el riesgo más alto solo se confina al chiplet que se está produciendo en el nodo de proceso más avanzado, en lugar de en todo el chip.

Reutilización de Diseño

Una vez que se desarrolla un chiplet, este puede reutilizarse, reduciendo el costo de pruebas y verificación. La eficiencia en costos del proceso de diseño de chips es significativamente mayor mediante el uso de módulos chiplet porque pueden reutilizarse. Un escenario de reutilización de chiplets es diseñar y fabricar solo el chiplet central para un CI, mientras que los chiplets restantes en el paquete se adquieren de otro proveedor. Usar este enfoque con chiplets prefabricados de múltiples proveedores, o reutilizando IP en un nuevo diseño, reduce grandemente los costos totales de diseño y verificación del producto.

En caso de que se requiera alguna actualización al sistema, un chiplet puede ser intercambiado por otro dentro del empaque. Note que el empaque en sí mismo podría necesitar ser actualizado, pero esto es mucho menos difícil que rediseñar un componente monolítico completo. Una pequeña porción del sistema también podría rediseñarse sin incurrir en nuevos costos de verificación que surgirían en paquetes semiconductores monolíticos. Este método de reutilización de chiplets se denomina “reutilización heterogénea”.

Otro escenario de reutilización de chiplets es integrar múltiples chiplets idénticos en el mismo sistema. Este método es ideal para sistemas escalables y mejora significativamente su eficiencia mientras reduce costos. Esto se refiere como el método de reutilización homogénea y la principal ventaja es que aumentar el número de chiplets en la arquitectura es todo lo que se necesita para cumplir con los diversos requisitos de rendimiento y potencia.

Tecnologías de Empaquetado de Chiplets

Para hacer productos basados en chiplets, se necesitan habilidades de diseño, dados, conexiones entre los dados y una estrategia de producción. El rendimiento, precio y madurez de las tecnologías de empaquetado de chiplets tienen un impacto sustancial en la aplicación de chiplets. De acuerdo con las diferencias en medio de conexión y métodos, las tecnologías de empaquetado usadas para la interconexión de chiplets pueden clasificarse en tres grupos:

-

Empaquetado en sustrato

-

Empaquetado con interconector de silicio

-

Empaquetado con capa de redistribución (RDL)

-

Puente de interconexión multi-die embebido (EMIB)

Empaquetado Basado en Sustrato

En el empaquetado basado en sustrato, la elección popular de sustrato es un material orgánico ya que estos están fácilmente disponibles. Similar a las PCBs convencionales, las conexiones de cableado se realizan a través de un proceso de grabado que es independiente de otros procesos usados en la fabricación de semiconductores. Esto es mejor conocido como la primera encarnación de la integración heterogénea 2D.

A través del diseño flip-chip o apilamiento, varios dados pueden unirse fácilmente a un sustrato con una alta densidad. Además, los costos de materiales y fabricación asociados con esto son mínimos porque esta tecnología no depende del proceso de fabricación de chips. El principal inconveniente de usar esta tecnología es la baja densidad de pines de E/S y la limitación resultante en el ancho de banda de las interconexiones en estos paquetes.

Empaquetado con Interconector de Silicio

Esta tecnología abarca las tecnologías de empaquetado 2.5D y 3D, donde los chips se construyen lateralmente en un interposer (2.5D) o apilados verticalmente (3D). Para implementar interconexiones y comunicación entre los dies, la capa de interposer de silicio se coloca entre el sustrato y los dies. El interposer es como una miniatura de placa de circuito impreso, proporcionando esencialmente un sustrato para conexiones eléctricas entre chiplets. La tela de interconexión está construida a partir de contactos metálicos (llamados microbumps) y vías a través de silicio (TSV) que corren internamente en el paquete. Estos se utilizan para conectar el die al interposer, y los conectores del interposer a un sustrato del paquete con un patrón de tierras BGA.

Estos productos tienen una mayor densidad de E/S con un consumo de energía reducido y un menor retraso en la transmisión. Esto se habilita por la menor longitud de traza y el paso entre microbumps y TSVs. El único inconveniente significativo de esta tecnología es el aumento de los costos de fabricación.

Empaquetado RDL

La tecnología de empaquetado de capa de redistribución (RDL) no utiliza un sustrato, en cambio, implica la deposición directa del dieléctrico y el metal directamente en la superficie superior del wafer. Esta tecnología también se conoce como tecnología de ‘fanout’. Para llevar el diseño del cable, se construye una capa de redistribución de tal manera que los puertos de E/S en cada chiplet se forman alrededor del dispositivo. Al acortar la longitud del circuito, RDL proporciona una mayor integridad de señal (menor pérdida y distorsión).

Puente de Interconexión Multi-die Integrado

EMIB es una tecnología que utiliza secciones delgadas de obleas de silicio incrustadas en materiales orgánicos como sustratos para interconexiones de die a die. El problema de costos más altos en productos avanzados puede abordarse mediante el uso de empaquetado de puente con chiplets diversos. Esta tecnología de empaquetado híbrido es una combinación de empaquetado basado en sustrato e interposer. Capas delgadas de silicio, generalmente de menos de 75 micrones, se revisten sobre el sustrato y se utilizan para formar conexiones entre dies, y estas capas están incrustadas en una capa de sustrato orgánico.

El concepto sigue las mismas ideas en ELIC utilizadas en PCBs HDI, donde una tela de interconexión de cada capa conecta múltiples dies a capas internas en un sustrato aislante (orgánico). La parte EMIB del paquete es un puente de silicio que proporciona conexiones de alto ancho de banda entre chiplets.

Conclusión

Se espera que los chiplets continúen revolucionando aplicaciones que requieren componentes de alta computación así como funcionalidad diversa en un solo paquete. Estos productos actualmente están dirigidos a tecnologías avanzadas como 5G, IoT, automotriz, computación periférica, imagen médica, computación en el borde, IA, dispositivos móviles y mucho más.

Hoy en día, grandes fabricantes de semiconductores como Intel, Marvell y AMD se han aventurado en la tecnología de chiplets, y podemos esperar que más empresas exploren esta opción. A medida que se desarrolla un mercado para la propiedad intelectual (IP) de chiplets, de manera similar a cómo se ha desarrollado un mercado para muchos otros componentes, más compañías de semiconductores sin fábricas podrían adoptar un enfoque de semiconductores personalizados en lugar de construir sistemas con componentes discretos.

Ahora que Intel, AMD y TSMC han acordado un estándar común para las interconexiones de chiplets, ¿veremos una mayor proliferación de estos diseños por parte de otras empresas? Uno puede esperar que se desarrolle un mercado para estos componentes, ya que esto fomentará más innovación a nivel de empaquetado más allá de los grandes fabricantes de semiconductores.

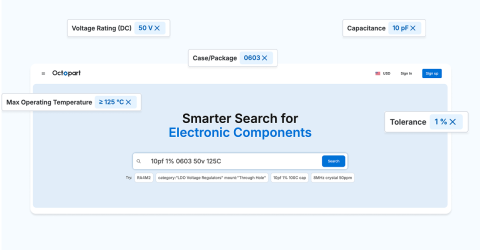

A medida que los componentes basados en chiplets con empaquetado avanzado salen al mercado, los diseñadores de sistemas pueden usar las funciones avanzadas de búsqueda y filtrado en Octopart para encontrar todos los componentes avanzados que necesitan para diseños avanzados. Cuando usas el motor de búsqueda de electrónica de Octopart, tendrás acceso a datos de precios de distribuidores actualizados, inventario de partes y especificaciones de partes, y todo es libremente accesible en una interfaz amigable para el usuario. Echa un vistazo a nuestra página de circuitos integrados para encontrar los componentes que necesitas.

Mantente al día con nuestros últimos artículos suscribiéndote a nuestro boletín.