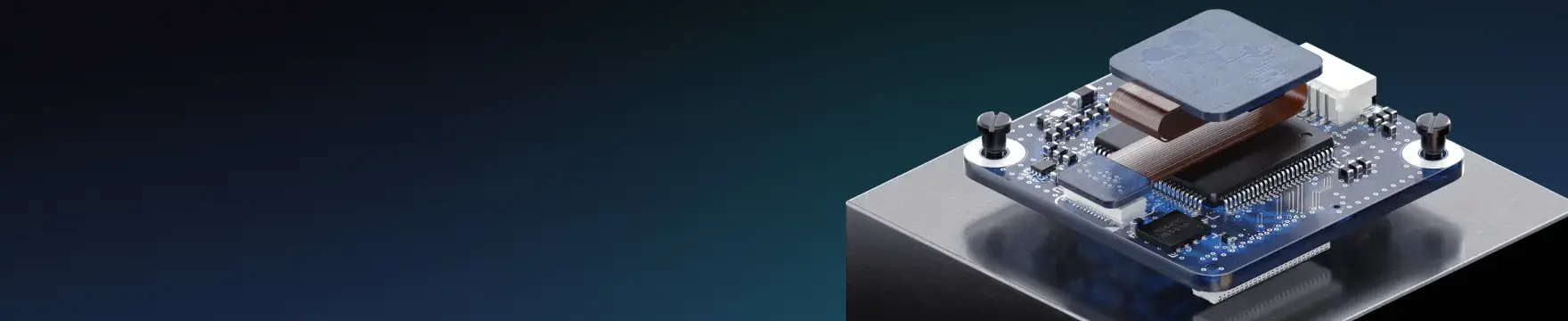

Plongée dans les contraintes de conception et de fabrication de circuit imprimé - partie 2

1. Introduction

Dans l’article précédent, nous avons vu les contraintes liées à la largeur des conducteurs en terme de fabrication (assemblage des composants par brasage – par refusion ou à la vague – ou par insertion en force – i.e. Press-Fit) mais aussi bien évidemment en termes de capacité à faire circuler un courant donné (en régime établi comme en cas de court-circuit – cf. Formule d’Onderdonk). En parallèle de ces problématiques techniques, nous avons vu la manière de les traiter sous Altium Designer.

Dans ce deuxième article, nous abordons la problématique de la tenue en tension (en particulier en haute tension) et donc de l’isolation entre des conducteurs placés à des potentiels très différents. Il s’agit là encore d’aspects importants de la conception d’une carte électronique qui touchent à des problèmes de sécurité et pour lesquels on doit autant que possible s’appuyer sur les outils offerts par le logiciel pour correctement les prendre en compte.

Nous verrons donc à la section 3 les notions de “clearance” et de “creepage” mais avant cela, à la section 2, nous allons voir la manière de récupérer des règles générales de fabrication (incluant celles vues dans le premier article) soit d’un projet précédent soit celles provenant d’un fabricant de circuits imprimés fournissant directement ces informations dans un format exploitable par Altium Designer.

2. Règles et fichiers de fabrication

L’interaction entre le concepteur et le site de fabrication (en interne ou en externe) passe essentiellement par les fichiers de fabrication (carte + assemblage des composants). Historiquement et même encore très majoritairement à l’heure actuelle, le format GERBER s’avère le plus employé pour la réalisation des circuits imprimés (+ fichiers de perçage : NC Drill, Excellon...).

L’impact des contraintes de fabrication sur l’étape de conception se traduit essentiellement en terme de :

-

largeur minimale de pistes (élément qui a été traité dans l’article précédent) ;

-

espacement minimal entre pistes (point traité dans le présent article) ;

-

diamètre minimal de perçage ;

-

etc...

Toutes ces données sont fournies par le fabricant et dans certains cas (par exemple la société Sunstone), celui-ci les met à disposition de l’utilisateur directement dans le format natif de son outil de CAO. Dans le cas d’Altium Designer, il s’agit de fichiers .RUL pouvant être chargés dans la fenêtre “PCB Rules Contraints Editor” avec le menu contextuel et sa commande Import Rules… Il suffit alors de sélectionner les contraintes que l’on souhaite configurer (click + Ctrl) dans la liste disponible à partir du fichier .RUL (cf. figure 1).

Figure 1. Importation sélective de règles de fabrication (fichier .RUL)

Remarque 1 : Les contraintes d’espacement entre les pistes ne sont pas uniquement liées à un fabricant de PCB donné. Elles sont aussi liées à l’épaisseur de cuivre utilisée : en pratique, l’espacement minimal requis entre les pistes (indépendamment de la tension présente) est d’autant plus grand que les épaisseurs de cuivre sont grandes du fait du process de gravure chimique. Une lecture attentive des performances offertes par le fabricant est alors requise (e.g. indications fournies ici dans le cas de la société PCBWay) et si ces informations ne sont pas explicitement données, il est préférable de prendre contact le plus tôt possible avec le fabricant pour éviter de mauvaises surprises au moment de la commande !

Remarque 2 : L’exportation des règles de fabrication est également possible à partir d’un projet. Pour cela, il suffira d’utiliser la commande Export Rules… présente dans le même menu contextuel que la commande Import Rules…

2. Contraintes physiques associées aux isolants

2.1. Espacement des conducteurs : « Clearance »

La tenue en tension d’un isolant dépend de plusieurs facteurs : la nature du matériau utilisé (l’air ou un isolant solide par exemple), la géométrie de l’interface entre isolant et conducteur (effet de pointe) ainsi que son éventuelle contamination. Tout ceci rend le dimensionnement complexe et on s’appuie classiquement sur des recommandations telles que celles de la figure 2.

Figure 2. Proposition d’isolations sans et avec composants (source : Gold Phoenix PCB [1])

Pour définir ces règles d’espacement (clearance), on peut les déclarer de la même manière que celles des largeurs de pistes (commande Design > Rules…) – cf. figure 3. Bien évidemment, plusieurs règles de clearance (avec des niveaux de priorité distincts) peuvent être créées.

Figure 3. Création d’une règle d’écartement de conducteurs (pas uniquement de pistes)

On constate, à la lecture du tableau, que les couches internes sont mieux isolées que les couches externes : cela est dû au fait que l’époxy est un meilleur isolant que l’air mais cela est également dû à la possible contamination en surface (poussière, humidité, etc.). Ce problème est en partie solutionné par l’usage d’un revêtement enrobant (conformal coating) tel qu’observé à la figure 4.

Figure 4. « Conformal coating » à la surface d’un PCB (Dymax Corporation)

Pour la définition de ce « coating » (cas d’un revêtement sélectif), il suffit de créer une couche supplémentaire (couche mécanique que l’on pourra par exemple nommer ConformalCoating – cf. figure 5) dans laquelle on ajoutera des polygones (Place > Solid Region) ou des rectangles (Place > Fill).

Figure 5. Création d’une couche ConformalCoating (commande Add Mechanical Layer du menu contextuel)

Remarque : Comme le montre le tableau de la figure 1, la tenue en tension est d’autant plus faible que l’altitude est élevée. Cela peut sembler contre-intuitif mais la rigidité diélectrique d’un gaz n’est pas une fonction linéaire de la pression. Ces deux grandeurs sont liées par la loi de Paschen comme le montre la caractéristique donnée à la figure 6 pour différents gaz. Avec cette relation ainsi qu’avec le lien entre altitude et pression, on peut retrouver ce résultat (qui justifie l’emploi quasi-systématique du « conformal coating » dans le domaine aéronautique1).

2.2. Encoches et « creepage »

Néanmoins, l’air peut être considéré comme un meilleur isolant que la surface d’un PCB (donc pour les couches TOP et BOTTOM) sans coating. C’est pourquoi on trouve couramment des découpes dans des circuits imprimés soumis à des tensions élevées pour éviter la formation d’un arc électrique à leur surface. Une illustration avec une résistance CMS 2512 est proposée à la figure 7. La distance entre deux conducteurs en ligne droite (clearance) est inchangée mais celle à la surface de la résine époxy est rallongée (creepage).

Figure 7. Découpes sur une carte de driver d’IGBTs.

Remarque : Les encoches n’ont pas toujours pour but l’augmentation de la tenue en tension. Elles peuvent aussi assurer une fonction mécanique – pour éviter une “collision” potentielle avec un autre élément (e.g. élément de fixation/boîtier, composant de forte épaisseur sur une carte en mezzanine). Elles peuvent également avoir un rôle de « barrière » limitant le stress mécanique transmis à des composants sensibles (e.g. référence Linear Technology LTZ1000 – cf. figure

Plusieurs options sont envisageables pour définir des encoches :

- importation d’un modèle 3D avec encoches du PCB ;

-

définition manuelle de type « Board Cutout » ;

-

ajout de trous de perçage (oblongs) ;

-

découpes intégrées dans les empreintes des composants.

La première solution (utilisant un fichier de modélisation 3D de type STEP, Parasolid ou Solidworks) offre l’avantage de définir aisément la forme du PCB à l’aide d’un outil de CAO mécanique. Un tel fichier peut aussi être disponible chez certains fabricants de boîtiers tels que Schroff comme on peut le voir à la figure 9.

Remarque : A l’exception de l’import du modèle 3D du PCB, les deux autres solutions proposées (ajout d’un « Board Cutout » ou d’un trou non métallisé) pour réaliser une découpe sont utilisables lors de la création d’une empreinte physique (footprint) au sein d’une bibliothèque de composants (.PcbLib).

Figure 9. Exemple de boîtier pour lequel le fabricant fournit des fichiers de CAO mécaniques (site Schroff)

Une fois le fichier (par exemple .STP pour le format STEP) créé ou récupéré chez un fournisseur, il faut le placer (en définissant un contour quelconque) dans le fichier du PCB à l’aide de la commande Place > 3D Body. En mode 2D, le corps 3D est représenté par son contour hachuré (figure 10).

Il s’agit ensuite de passer en mode 3D en pressant la touche « 3 » (la touche « 2 » permettant de repasser en 2D). Si l’objet n’est pas correctement orienté, il suffit de le sélectionner (double-clic) pour faire apparaître l’onglet « Properties » correspondant sur le bord droit de l’écran (figure 11). On peut alors lui faire subir des rotations suivant les 3 axes ainsi qu’une élévation (Standoff height) qui, dans le contexte de la définition du contour de carte, n’a pas réellement d’utilité.

Figure 10. Insertion d’un objet 3D dans un fichier .PcbDoc

Figure 11. Orientation de l’objet 3D pour correspondre au plan du PCB

Une fois l’objet correctement orienté, il ne reste plus (toujours en mode 3D) qu’à utiliser la commande Design > Board Shape > Define from 3D body (figure 12). Il est alors possible d’aligner au choix l’objet 3D sur la face TOP, la face BOTTOM ou le laisser inchangé.

Figure 12. Contour de carte définie ainsi que les découpes internes

En pratique, cela n’est pas nécessaire car une fois le contour du PCB défini, on peut l‘effacer pour ne plus avoir à l’écran qu’un contour noir (en mode 2D) ou une vue 3D (PCB vert par défaut).

Si cette solution est simple, elle n’est malheureusement pas très bien adaptée à l’objectif visé ici. Si dans le cas de découpes réalisées pour des raisons mécaniques, leur localisation dès le début de la conception du PCB est possible, ce n’est pas le cas lorsque ces encoches doivent être placées entre des composants dont le placement n’est pas figé. Dans ce cas, il faudra directement mettre en œuvre des objets de type Board Cutout (comme ceux créés automatiquement à partir du modèle 3D). Pour cela, on peut utiliser tout naturellement la commande Design > Board Shape > Define Cutout mais on peut également utiliser les commandes alternatives suivantes :

-

Place > Solid Region ;

-

Place > Polygon Pour Cutout.

Bien que ces deux types de polygones n’aient pas par défaut la fonction de découpe de PCB, ils disposent tous les deux de la propriété « Kind », comme illustré à la figure 13, dont une des valeurs possibles est « Board Cutout ».

Figure 13. Possibilités de découpes « manuelles » dans un PCB

Au niveau des fichiers de fabrication, il sera ensuite nécessaire de transcrire ces découpes en contours de carte dans une couche mécanique comme indiqué à la figure 14. Par défaut, seul le contour externe du PCB sera réalisé et pour inclure les découpes internes, il ne faut pas oublier de cocher la case « Include Cutouts ». Après validation, les contours sont représentés dans la couleur de la couche mécanique sélectionnée (ici en rose) avec la largeur de traits spécifiée (ici 20 mils, i.e. 20 millièmes de pouces soit approximativement 0.5 mm).

Figure 14. Définition des contours de la carte dans la couche « Mechanical 1 »

Mis à part les Board Cutouts, une autre solution pour réaliser des découpes consiste tout simplement à insérer des trous non métallisés dans le PCB à l’aide de « Place Pad » présent dans le bandeau de commandes à accès rapide ci-dessous :

Il s’agit ensuite de configurer (toujours avec le même onglet « Properties » à la droite de l’écran) ce pad pour réaliser la fonction d’isolation désirée :

-

le nommer (par exemple « ISO1 ») ;

-

le configurer en slot (rubrique « Hole Information ») ;

-

configurer dans cette rubrique le diamètre de fraise « Hole Size » ainsi que la longueur de la rainure (« Length ») ;

-

décocher la case « Plated » pour que ce trou d’isolation ne soit bien évidemment pas métallisé ;

-

ramener la taille de la pastille de cuivre à zéro (rubrique « Size and Shape »).

2.3. Soldermask

En pratique, on considère que le vernis épargne (soldermask) n’apporte pas d’amélioration (ou presque) de la tenue en tension d’un circuit électrique. Par contre, il peut s’avérer gênant dans certaines applications (effet en hautes fréquences) de telle sorte qu’il est courant de l’enlever dans ces cas (cf. figure 15).

Figure 15. Circuit radiofréquence incluant des filtres sans vernis épargne – source : Wikipédia (article : Distributed element filter)

Dans ce genre de configuration, il est simple d’éliminer le vernis épargne en définissant une zone (à l’aide d’un bloc rectangulaire « Fill » ou polygonal « Solid Region » placé dans la couche de soldermask (Top Solder ou Bottom Solder) comme le montre l’image de la figure 16.

Figure 16. Ouverture placée dans le soldermask (en mauve)

Par contre, si une élimination du vernis uniquement à la surface d’une piste (comme pour un circuit de garde2 tel qu’à la figure 8) est souhaitée, l’approche est différente : il est nécessaire de sélectionner cette piste puis d’aller dans l’onglet « Properties » (figure 17) pour modifier les paramètres « Solder Mask Expansion ». En cochant la case, une ouverture du masque est automatiquement pratiquée au-dessus de la piste et par ailleurs, elle déborde sur une largeur spécifiée (ici 1 mil – on peut d’ailleurs voir le liseré mauve de la couche « Top Solder » autour de la bande rouge – couleur associée au cuivre de la couche « Top Layer »).

Figure 17. Élimination du vernis épargne au-dessus d’une piste

2.4. Protections contre les surtensions

Les surtensions sont des évènements rares mais néanmoins inévitables contre lesquels on cherche à protéger les circuits électroniques. Les mesures prises pour assurer la tenue en tension d’un PCB ne sont pas à proprement parler des éléments de protection mais elles doivent accompagner des éléments prévus à cet effet dans lesquels on assurera une décharge. De tels composants, plus ou moins rapides (diodes transil, MOV, GDT) n’entrent pas dans le cadre de cet article mais ils doivent être utilisés en conjonction d’un circuit imprimé correctement conçu.

Dans les cas de circuits à très bas coût, on peut néanmoins trouver des protections directement intégrées au PCB : il s’agit de d’éclateurs à air (spark gap). Dans ce cas, on utilise directement l’air ambiant (ou plutôt les impuretés à la surface du PCB) comme isolant entre deux pastilles à nu sur le circuit imprimé comme illustré à la figure 18.

Figure 18. Exemple de « spark gap » (source : https://atadiat.com/en/e-four-pcb-marks-part-2/)

Le problème d’un tel circuit (qui devrait être proscrit !) est que la maîtrise de la tension de claquage entre les deux électrodes implique de contrôler l’atmosphère autour du PCB complet (poussière, pression, humidité) alors que ces conditions sont bien mieux garanties dans un GDT au boîtier scellé.

2.5. Nouvelles règles de « creepage » (Mise à jour relative à AD 20)

Depuis la sortie d’Altium Designer 20, les contraintes d’écartement entre les pistes pour les applications à haute tension sont désormais prises en compte dans les règles de conception du PCB (Design > Rules…), rubrique Creepage Distance – cf. figure 19). Comme cela est évoqué au paragraphe 2.2., le creepage correspond à une longueur à parcourir entre deux conducteur en restant à la surface du substrat isolant, c’est-à-dire en évitant les cavités (contours du bord de la carte ou découpes internes). Cette définition est parfaitement illustrée par le dessin présenté dans la fenêtre de configuration dans laquelle on spécifie les deux objets entre lesquels la règle doit être respectée (ici deux « nets ») ainsi que la distance souhaitée (fonction de la tension à supporter et des conditions environnementales : altitude/pression atmosphérique…).

Figure 19. Configuration de la règle de creepage

Cette règle peut alors être testée hors ligne (batch) mais aussi et surtout en ligne (online) – cf. figure .

Figure 20. Configuration en ligne (online) ou hors ligne (batch) des règles de conception (commande Tools > Design Rules Check…)

Cela permet de vérifier en temps réel (cf. figure 21) que cette règle est bien respectée lorsque l’on positionne un composant, en particulier lorsqu’il est « à cheval » sur une encoche réalisée dans la carte (soit un « internal cutout » soit une forme particulière du contour de carte).

Figure 21. Affichage en temps réel de la violation de la règle indiquant la distance effective entre les objets spécifiés dans la règle (ici 2 nets)

3. Conclusion

Nous avons vu dans cet article les moyens d’assurer une bonne tenue en tension d’un circuit imprimé. Dans le cas des « clearances », il est possible de fixer une ou plusieurs règles pour s’en assurer étant donné qu’elles sont appliquées en temps réel pendant le routage (même manuel – cf. figure 22).

Figure 22. Routage manuel (clearance visible autour des conducteurs en pressant Ctrl + W)

Pour le « creepage », une solution équivalente existe depuis la version 20 d’Altium Designer comme le montre le paragraphe 2.5. Pour les version antérieures, il est toujours possible d’employer la méthode proposée ici ou bien de directement mesurer les distances (comme à la figure 23) si le nombre de tests à effectuer est faible.

Figure 23. Mesure de distances (Reports > Measure Distance ou Ctrl + M)

Références

[1] Printed Circuit Design Tutorial, Gold Phoenix PCB, https://www.goldphoenixpcb.com/html/Support_Resource/downloads/downloads.html

[2] Low Level Measurements Handbook, 7ème édition, Tektronix / Keithley, https://download.tek.com/document/LowLevelHandbook_7Ed.pdf

1 Sans même tenir compte des problématiques de condensation qui viennent aggraver le problème.

2 Circuit piloté pour compenser les courants de fuite à la surface d’un circuit imprimé – cf. [2].