Directives de routage des PCB pour les dispositifs de mémoire DDR4

La marine américaine (Navy) utilise des désignations alphabétiques pour classer les types de coque. Par exemple, la Navy a utilisé BB comme désignation pour les cuirassés et DD pour les destroyers. Au début des années 1950, peu de temps après le début de la guerre froide, la Navy a équipé le premier destroyer Radar Picket de systèmes spéciaux de communication radar. Les DDR disposaient d'antennes radar supplémentaires et servaient d'unités d'alerte rapide.

Dans le monde des dispositifs de mémoire, la désignation "DDR" a une signification différente pour les systèmes de communication, les horloges, les ordinateurs personnels, les smartphones, les tablettes et les serveurs. Plutôt que de fournir des alertes précoces sur les forces ennemies potentielles, les dispositifs de mémoire DDR ont évolué et changé notre perception de la performance lorsqu'il s'agit de transfert de données de circuits imprimés, de consommation d'énergie et de technologie basée sur la mémoire.

La DDR4 mérite une attention particulière

En 2014, la quatrième génération de mémoire DDR (DDR4) a été introduite, offrant une consommation d'énergie réduite, des vitesses de transfert de données plus élevées et des densités de puces supérieures. La mémoire DDR4 offre également une meilleure intégrité des données avec l'ajout de contrôles cycliques de redondance sur les données d'écriture et la détection de la parité sur les puces.

Avec des améliorations notables en termes de vitesse, de performances et de bande passante, la mémoire DDR4 mérite une attention particulière. Pour comprendre la différence entre les dispositifs DDR3 et DDR4, imaginez que vous échangiez votre berline familiale quatre portes actuelle pour une super voiture de sport unique en son genre. Tout comme la super voiture de sport roule à des vitesses plus élevées et nécessite d’une aérodynamique différente, la DDR4 offre une très bonne performance en termes d'intégrité du signal et implique des débits de données élevés.

Nous pouvons pousser l'analogie de la super voiture de sport un peu plus loin en examinant la conception. Comparée à la berline familiale, la super voiture de sport nécessite une aérodynamique plus avancée et des composites en fibre de carbone pour sa carrosserie et ses composants. De même, les conceptions de PCB construites autour d’une mémoire DDR4 nécessitent des méthodes de routage différentes de celles des PCB standards.

En l'absence de méthodes de routage spécialisées et de règles de conception spécifiques à la DDR4, la qualité du signal entre l'émetteur et le récepteur peut en souffrir. Comment aborder la conception spécifique à la DDR4 du point de vue de la topologie des PCB ? Quelles règles seraient les mieux adaptées pour garantir que votre appareil fonctionne avec ses données comme prévu ?

Règles de conception pour la DDR4

La synchronisation peut être l’élément l'essentiel lorsque l'on travaille avec des signaux sensibles et la technologie des horloges. Assurez-vous que votre carte de circuit imprimé a la capacité de gérer efficacement ses données en suivant des directives modèles pour le routage et la conception des PCB avec la DDR4. Sinon, vous risquez d'être confronté à un retard de conception ou à des problèmes répétés d'interférences électromagnétiques et d'autres vulnérabilités perturbatrices du signal.

Vous devez vous souvenir que les débits de données allant de 1,6 Gbit/s à 3,2 Gbit/s, les sortances à grande échelle et les vitesses de montée plus élevés nécessitent de techniques spécifiques pour maintenir au minimum les taux d'erreur binaires nécessaires à l'intégrité du signal. Par exemple, un manque d'attention aux règles de conception peut conduire à un couplage capacitif et inductif d'un signal à l'autre. Au fur et à mesure que ce couplage augmente, la diaphonie devient de plus en plus problématique.

Pour réduire les possibilités de couplage capacitif, vous pouvez retirer de votre conception toutes les pastilles via inutilisées. Le découplage des condensateurs entre la tension de terminaison (VTT) et la masse minimise le couplage inductif. Le VTT alimente la mémoire et est séparé de la tension d'entrée/sortie (VIO) et de la tension centrale (VCORE).

Les horloges et les interfaces basées sur des horloges sont omniprésentes dans la technologie de transmission de signaux et de données

Plans de routage pour différentes topologies DDR4

Les SDRAM DDR4 fonctionnent soit avec une topologie à coquille, soit avec une topologie fly-by. Les deux topologies comportent des avantages et des inconvénients. La topologie à coquille utilise deux couches et moins d'espace sur la carte, mais nécessite un plan de routage complexe. L'encombrement du routage entre les couches supérieure et inférieure sous les dispositifs de mémoire peut entraîner une congestion du routage et de plus grandes traces sur le stub (tronçon de ligne de trasmission).

En revanche, la topologie fly-by permet un routage facile et assure une meilleure intégrité du signal. Cependant, la topologie fly-by, avec une couche de dispositifs de mémoire en ligne, nécessite plus d'espace. En fin de compte, le choix de l'option qui convient le mieux à votre réseau dépend de la fonction de l'appareil.

Lorsque vous configurez le routage pour votre conception de PCB, acheminez toujours le même groupe de réseau sur la même couche. Utilisez des angles de 45° plutôt que des angles de 90° et évitez les jonctions en T pour vos réseaux essentiels et vos horloges. N'acheminez pas les signaux de mémoire à moins de 0,025 pouce de votre PCI ou de l’horloge et assurez-vous que votre routage reste à une distance minimale de 30 mm du plan de référence et des bords vides. D’ailleurs, respectez la distance entre les signaux de réinitialisation du système et les autres signaux.

L'espacement et la longueur sont des éléments importants

Les SDRAM DDR4 nécessitent d’acheminements plus courtes et un espacement correct pour une synchronisation optimale et une meilleure intégrité du signal. Évitez toujours de router deux couches de signaux l'une à côté de l'autre et acheminez les lignes de signaux sur un plan de référence solide. Lorsque vous construisez votre plan de routage, évitez de router les lignes de signaux sur des espaces vides ou au delà des fentes du plan de référence.

Tous les signaux relatifs à l'interface mémoire doivent être acheminés entre les couches GND ou les couches de puissance appropriées. Acheminez les signaux DQ, DQS et DM à l'intérieur d'un groupe d'octets donné sur la même couche pour réduire ou éliminer les différences de vitesse de transmission entre couches. Comme le signal d'horloge doit avoir un retard de propagation plus grand que le signal DQS, la trace du signal d'horloge doit avoir une longueur plus grande que la trace DQS la plus longue pour les DIMM. Les lignes d'horloge différentielles ont une plus grande résistance au bruit ainsi que d'autres impacts négatifs sur l'intégrité du signal.

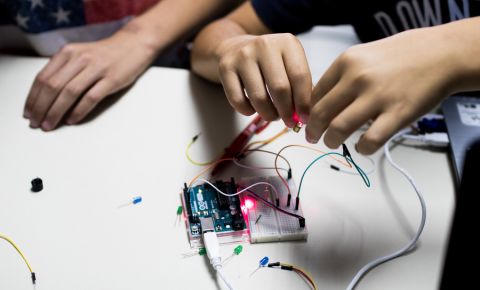

Un logiciel de routage performant vous aidera à vous assurer que toute conception avec un signal intensif peut fonctionner sans problème

Pour planifier l'espacement entre les traces dans la disposition, vous devez utiliser comme facteur la distance verticale par rapport au chemin de retour le plus proche pour une trace particulière. La pratique consiste à utiliser une "H" pour représenter le facteur. Multipliez cette longueur par cinq pour trouver l'espacement minimal entre les deux paires d'horloges ou une paire d'horloges. Rappelez-vous que les traces Adresse/Commande/Contrôle et DQ/DQS/DM nécessitent un minimum de 3H entre les traces.

Pour simplifier les choses, vous pouvez facilement simuler l'intégrité du signal dans Altium Designer® pour les phases de capture de conception et de topologie des cartes de votre processus de conception de PCB. Le simulateur calcule l'impédance caractéristique des traces et utilise ces informations, ainsi que les informations du macro-modèle tampon E/S, comme entrées.

Altium vous aide également à définir les largeurs des traces et les épaisseurs de routage grâce à son option Characteristic Impedance Driven Width dans la règle de conception Routing Width. La topologie des PCB n'a jamais été aussi simple pour les circuits imprimés avec une mémoire volatile, une mémoire non volatile, des dépendances de synchronisation et d'horloge, ou pour les paires différentielles. Utilisez un logiciel de conception de PCB qui peut effectuer le travail avec précision et efficacité pour vous.

Pour en savoir plus sur les directives de routage des PCB pour les dispositifs de mémoire DDR4, consultez un expert d’Altium.