Design for Test: Determining the Value of the JTAG Interface During the Schematic Stage

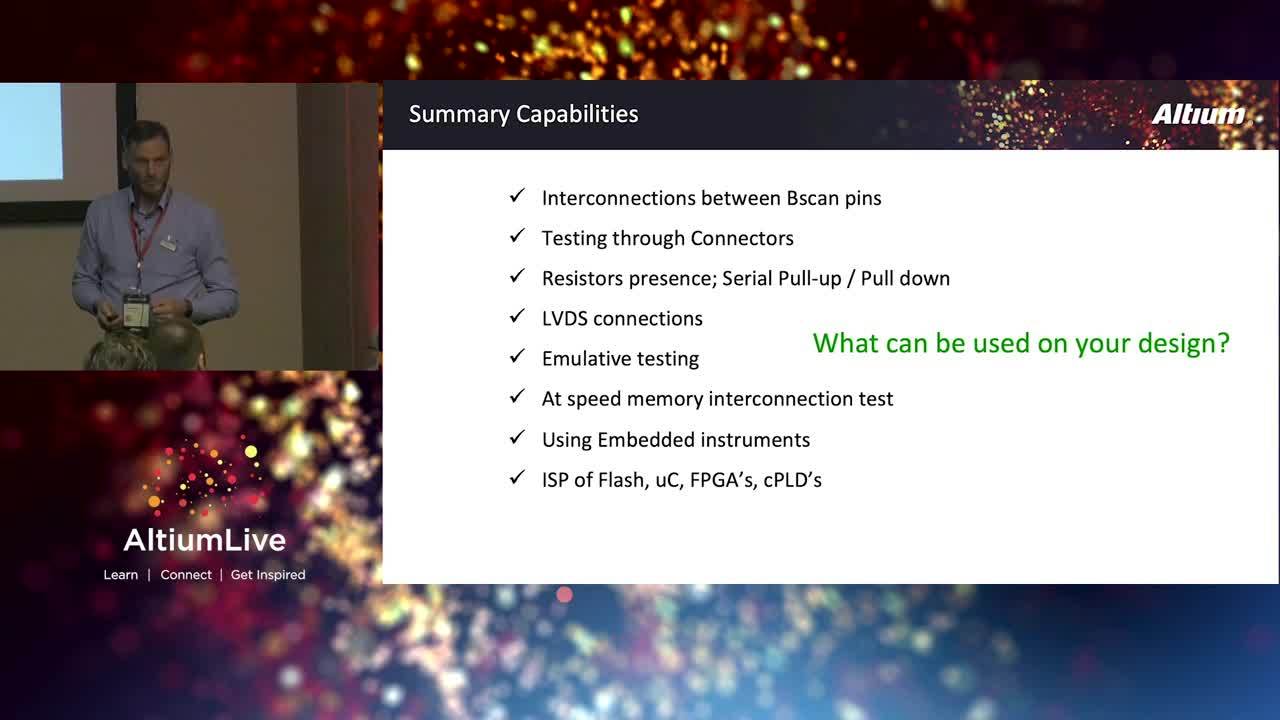

After a brief explanation about modern test methodologies and in-system programming capabilities via the JTAG interface on chip, board, and system level, the focus of this presentation will be on the necessity and ways for improving your design for testing (DFT) and fast in-system programming. This is best done during the schematic stage. Studies and experience show that if you do, your company will substantially save engineering time and build more reliable products.

View the presentation slides:

Sign up to pre-register for AltiumLive next year or try Altium Designer today.

About Author

About Author

Since 1995 Rik Doorneweert has helped and advised HW design teams and test engineering teams around the globe, adding Boundary scan tools or services from JTAG Technologies to their boards and system designs, thus improving their Design for Manufacturing and test processes. This helped the HW engineers to validate their prototypes without firmware and increase the reliability of their products while reducing their overall production and development cost.

Related Resources

Table of Contents

<ul><li class="b-hide__item"><a href="#view-the-presentation-slides">View the presentation slides: </a></li></ul>

Design to Release, Without the Friction

- Keep reviews tied to the right version

- Reduce handoff confusion and rework

- Spot sourcing and release risk earlier

- Work solo, share when needed

Get Started