Como a IA Quebrou o Mercado de Memória: Por Dentro do Aperto de DRAM e NAND de 2024–2026

Principais conclusões

- Os data centers de IA tornaram-se o principal cliente do silício de memória, impulsionando mudanças na alocação de wafers em DRAM, HBM e NAND simultaneamente.

- Este ciclo de oferta e demanda é diferente. A expansão limitada das fabs, a produção de NAND praticamente toda já comprometida e os contratos plurianuais de HBM significam que a escassez provavelmente persistirá até o fim de 2027–2028.

- Projetos legados e embarcados são danos colaterais. DDR3, DDR4 inicial e NAND SLC enfrentam risco crescente de EOL, prazos de entrega mais longos e preços imprevisíveis, à medida que os fornecedores priorizam memória para IA de alta margem.

A reviravolta da memória: de componente secundário a gargalo

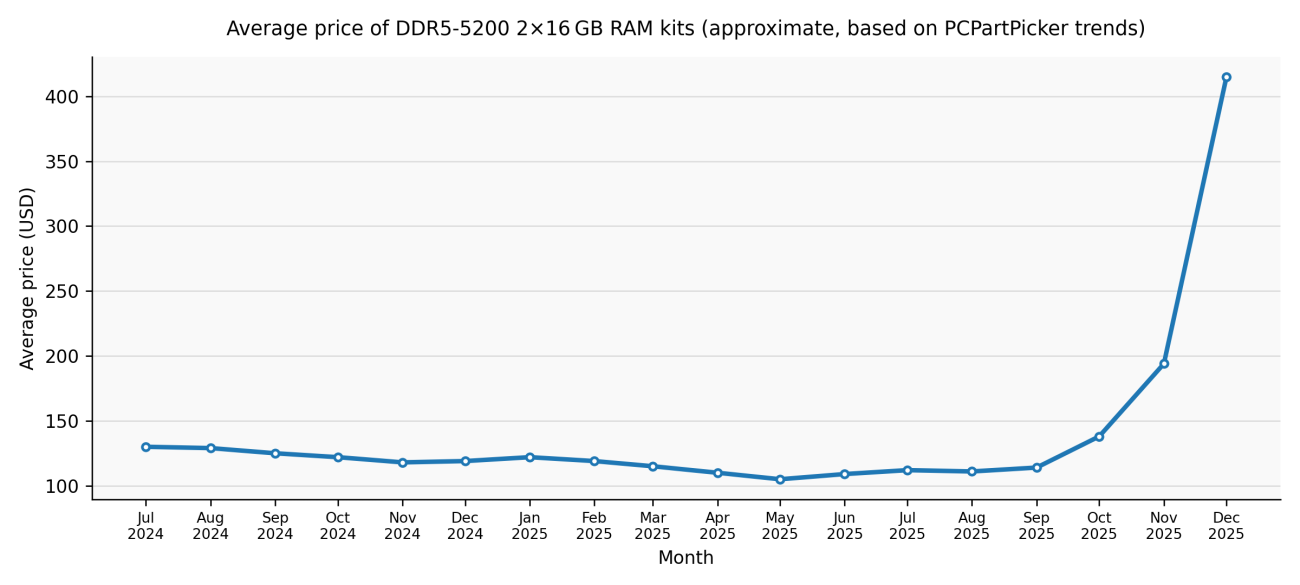

Durante a maior parte da era do PC, a memória ficava em segundo plano. Entre 2024 e 2026, essa dinâmica se inverteu. A memória tornou-se a principal restrição no projeto de sistemas, e o custo de “simplesmente adicionar mais RAM” subiu acentuadamente em apenas alguns trimestres.

Os preços subiram, a disponibilidade diminuiu, e os produtos estão sendo enviados cada vez mais com o mínimo indispensável de memória, em vez da folga confortável a que estávamos acostumados. Está em curso um rebalanceamento estrutural sobre quem recebe os wafers e por quê.

Então, o que realmente mudou, e por que essa escassez parece diferente das anteriores? Vamos explicar isso aqui, na primeira de uma série em duas partes que aborda as forças que estão desestabilizando o fornecimento de memória, dos servidores em nuvem até os sistemas embarcados. A segunda parte, Projetando hardware em meio à escassez de memória, aprofunda o tema com uma análise detalhada dos componentes de memória de próxima geração que estão começando a entrar em operação, dos principais produtos consolidados que você pode encomendar ao seu distribuidor hoje, de padrões de projeto e de táticas de sourcing.

Como os data centers de IA reconfiguram o cenário da demanda

Em ciclos anteriores, a demanda por memória era amplamente distribuída entre PCs, telefones, servidores e eletrônicos de consumo. Oferta e demanda saíam de sincronia, os preços disparavam ou caíam, e depois tudo se normalizava à medida que as fabs se ajustavam. A escassez de 2024–2026 não está seguindo esse roteiro.

A diferença está em quem está comprando. Os data centers centrados em IA agora dominam o quadro da demanda, e seus clusters de treinamento e fazendas de inferência precisam de enormes quantidades de memória de alta largura de banda (HBM) e DRAM convencional por GPU ou acelerador. A HBM consome significativamente mais capacidade de wafer por bit do que a DRAM padrão, tornando-se extremamente atraente para fabricantes que buscam fechar contratos plurianuais de alta margem com provedores de infraestrutura de IA.

Alguns analistas agora estimam que os data centers consumirão até 70% de todos os chips de memória de ponta produzidos em 2026, uma reversão acentuada em relação à época em que os dispositivos de consumo respondiam pela maioria desses chips. Nesse ambiente, a memória para PCs e dispositivos móveis torna-se um negócio secundário, enquanto os data centers de IA passam a ser o foco principal.

A geração HBM4 apresentada na CES 2026 ilustra a escala dessa mudança. A SK Hynix mostrou um dispositivo de 16 camadas e 48 GB que entrega mais de 2 TB/s, aumentando significativamente o desempenho da HBM3 inicial usada na primeira onda de aceleradores de IA generativa. Cada wafer destinado a essas pilhas deixa de produzir DDR5 para o seu próximo PC ou LPDDR5X para um telefone.

Projetos embarcados e legados: pressionados lateralmente

Projetos embarcados e industriais, que muitas vezes dependem de padrões DRAM mais antigos ou de NAND SLC madura, enfrentam seus próprios desafios. Muitos desses produtos usam dispositivos DDR3 ou DDR4 inicial, juntamente com flash NAND paralela, que já não estão mais no centro dos roadmaps dos fornecedores.

À medida que os fabricantes priorizam HBM de alta margem e DRAM de classe servidor, eles estão reduzindo ou descontinuando linhas legadas. O que permanece carrega preços inesperadamente altos e prazos de entrega mais longos, embora a tecnologia em si seja madura.

Acompanhar de perto o status do ciclo de vida dos componentes com ferramentas como Octopart ajuda as equipes a identificar anúncios de EOL e restrições de fornecimento antes que se tornem emergências.

Progresso sob pressão: DDR5, LPDDR6, NAND e HBM4

As mesmas transições tecnológicas que estão privando os projetos mais antigos de fornecimento estão produzindo avanços reais de engenharia. Entender os dois lados dessa dinâmica é relevante porque os avanços estão mudando o que está disponível para projetar, enquanto a economia dos wafers por trás disso explica por que a memória commodity não ficará mais barata tão cedo.

DRAM

A Samsung está produzindo em massa a DRAM LPDDR5X classe 12 nm mais fina para dispositivos móveis de próxima geração, combinando alto desempenho com eficiência energética e encapsulamento fino adequado para telefones premium e ultraportáteis. Os primeiros componentes LPDDR6 elevam ainda mais a largura de banda e a eficiência energética, visando aplicações de IA no dispositivo e automotivas. A implementação de LPDDR6 da Samsung vem ganhando reconhecimento em eventos do setor, sinalizando para onde a memória móvel de ponta está caminhando.

HBM

Na extremidade HBM do espectro, a cobertura da CES 2026 sobre HBM4 mostra que as pilhas de memória estão se tornando subsistemas altamente integrados. As pilhas 16-high da SK Hynix usam MR-MUF e wafers DRAM ultrafinos para permanecer dentro dos limites de altura da JEDEC, enquanto a Samsung está olhando para sua lógica de 4 nm (que entrou em produção em massa em fevereiro de 2026) para melhorar a térmica e a eficiência energética. Todo esse esforço de engenharia e capacidade de wafer está claramente direcionado a aceleradores de IA.

NAND

No lado da NAND, os fornecedores estão empilhando cada vez mais camadas. A V-NAND de 10ª geração com mais de 400 camadas e interfaces em torno de 5,6 GT/s está sendo projetada em SSDs PCIe 5.0 e futuros PCIe 6.0 para casos de uso em data centers e IA. A BiCS NAND de 10ª geração com 332 camadas da Kioxia e Sandisk, usando a interface Toggle DDR 6.0 a até 4,8 Gb/s por pino, demonstra o quanto a NAND de alta largura de banda avançou para SSDs de data center e classe empresarial.

A tecnologia está avançando, mas a capacidade não acompanha o ritmo. Segundo a EE Times, Samsung e SK Hynix reduziram a produção de wafers NAND em 2024–2025 enquanto perseguiam HBM e DRAM, e não anunciaram nova capacidade de NAND apesar de controlarem mais da metade do mercado. Os dados da Omdia mostram os wafers NAND da Samsung caindo de 4,9 milhões (2024) para 4,68 milhões (2025), e os da SK Hynix de 1,9 milhão para 1,7 milhão.

Ao mesmo tempo, a NAND tornou-se crítica para a inferência de IA. À medida que a IA passa do treinamento para a disponibilização de modelos, os SSDs baseados em NAND de muitas camadas tornam-se cada vez mais o principal armazenamento para pesos de modelos e dados de trabalho. A administração da Kioxia afirmou que toda a sua produção de NAND de 2026 já está vendida, que a BiCS10 está sendo antecipada do 2º semestre de 2027 para 2026 e que, no futuro, quase metade de sua demanda por NAND poderá vir de aplicações de IA. Especialistas em NAND como a Kioxia e o negócio Sandisk recém-independente, antes vistos como azarões em um mercado comoditizado, de repente estão posicionados como vencedores do boom dos SSDs para IA.

Por que a recuperação habitual não virá

Analistas do setor apontam para um crescimento relativamente modesto da oferta de DRAM e NAND até 2026 em comparação com os padrões históricos. Enquanto isso, a demanda não dá sinais de desaceleração. Novas arquiteturas de modelos, cargas de trabalho de inferência e implantações de IA de borda continuam elevando os requisitos de memória, em vez de permitir que se estabilizem. Os fornecedores de HBM4 estão dedicando capacidade substancial de wafer às exigências da Nvidia e de outros aceleradores e, como mencionamos na seção anterior, fornecedores de NAND como a Kioxia já estão com 2026 totalmente comprometido.

Em dezembro de 2025, a Micron demonstrou a natureza estrutural dessa mudança ao anunciar sua saída do negócio de consumo Crucial para dar melhor suporte a “clientes maiores e estratégicos”. Alguns fornecedores, incluindo a Micron, declararam publicamente que não esperam um alívio material na escassez de RAM para consumidores até por volta de 2028, quando nova capacidade e transições de processo estiverem totalmente aceleradas. A mesma lógica se aplica cada vez mais à NAND: a inferência de IA está comprometendo o fornecimento futuro de classe SSD tão rapidamente quanto os fornecedores conseguem colocá-lo em operação.

Em dezembro de 2025, a IDC caracterizou a escassez como “não apenas uma escassez cíclica, mas uma realocação estratégica potencialmente permanente da capacidade mundial de wafers de silício”. Em fevereiro de 2026, a TrendForce revisou fortemente para cima sua previsão de preços contratuais de DRAM convencional para o 1º trimestre de 2026, de uma estimativa anterior de 55–60% para 90–95% trimestre a trimestre. Dentro disso, projetava-se que a DRAM para PC (mistura de DDR4/DDR5) subiria 105–110% QoQ, um novo recorde trimestral.

O que vem a seguir: da compreensão à ação

Em Projetando hardware em meio à escassez de memória, analisamos sete componentes de memória da próxima onda entrando em ramp-up em projetos OEM e de data center, oito produtos DRAM e flash consolidados prontamente disponíveis nos principais distribuidores e playbooks concretos para trabalhar dentro dessas restrições.

Perguntas frequentes

Por que há escassez de memória mesmo com a tecnologia de DRAM e NAND continuando a melhorar?

A escassez atual não é causada por limites tecnológicos, mas pela economia da alocação de wafers. Uma parcela crescente da capacidade global de wafers de memória está sendo redirecionada para memória de IA de alta margem, especialmente HBM para aceleradores de data center. Como a HBM consome significativamente mais área de wafer por bit utilizável do que a DRAM convencional, cada wafer destinado à produção de HBM reduz a produção de DDR4, DDR5, LPDDR e NAND. Com expansão limitada de novas fabs e contratos de fornecimento de IA de longo prazo travando a capacidade, melhorias na densidade de memória não se traduzem em maior disponibilidade para os mercados convencionais ou embarcados.

Por que essa escassez de memória parece diferente dos ciclos anteriores?

Ao contrário dos ciclos anteriores de boom e queda, esta escassez é moldada por uma concentração estrutural da demanda, e não por um excesso temporário de consumo. As cargas de trabalho de treinamento e inferência de IA continuam ampliando os requisitos de memória, enquanto os fornecedores restringiram deliberadamente o crescimento da capacidade. Contratos plurianuais de HBM, produção de NAND de 2026 já esgotada e orientações explícitas dos fornecedores apontando para alívio apenas após 2027–2028 significam que esta é uma realocação de longa duração, não um desequilíbrio de curto prazo que se corrigirá sozinho apenas por meio de preços.

Que riscos isso cria para projetos embarcados e legados que usam DDR3, DDR4 inicial ou NAND SLC?

Os produtos de memória legados estão sendo cada vez mais tratados como não estratégicos pelos principais fornecedores. À medida que os fabricantes priorizam DRAM avançada e HBM, os nós de processo mais antigos enfrentam lotes de produção menores, quantidades mínimas de pedido mais altas, prazos de entrega mais longos e maior risco de EOL. Mesmo quando os componentes permanecem tecnicamente “em produção”, os preços tornam-se voláteis e a disponibilidade, imprevisível. Para as equipes de sistemas embarcados, isso aumenta a importância do monitoramento do ciclo de vida, do multisourcing e do planejamento de redesign muito mais cedo no ciclo de vida do produto do que em gerações anteriores.

Quando os engenheiros devem esperar que os preços e a disponibilidade de memória se normalizem?

Com base nas declarações dos fornecedores e nas previsões dos analistas, é improvável que haja um alívio significativo antes do fim de 2027 ou de 2028. Estão planejadas novas adições de capacidade, transições de processo e expansão das linhas de encapsulamento para HBM e NAND avançada, mas isso leva vários anos para entrar em operação. Ao mesmo tempo, as cargas de trabalho de inferência de IA estão ampliando a demanda tanto por DRAM quanto por NAND da classe SSD, absorvendo grande parte dessa capacidade futura. Os engenheiros devem planejar seus projetos partindo do pressuposto de que a memória continuará sendo um custo de sistema restrito e de alto impacto pelo restante desta década.