FPGA: Tạo Ống Dẫn Tích Hợp Liên Tục cho Hệ Thống Nhúng hoặc PCB

Trong bài viết này, Ari Mahpour hướng dẫn bạn cách tạo các đường ống Tích hợp Liên tục được nhắm mục tiêu cho FPGA

Field Programmable Gate Arrays (FPGA), hay các Mạch điều khiển logic có thể lập trình được, đã trở nên phổ biến trong các hệ thống số tốc độ cao và thời gian thực. Chúng có thể được sử dụng cho các ứng dụng quan trọng về thời gian, xử lý tín hiệu số hoặc thậm chí là khai thác tiền mã hóa. Hiệu suất về tốc độ và công suất của chúng làm cho FPGA trở nên hoàn hảo cho các ứng dụng tốc độ cao có thể tái sử dụng. Tốc độ hoạt động của FPGA liên tục tăng với tốc độ chóng mặt, nhưng việc tích hợp chúng vào các quy trình Continuous Integration (CI) dường như chưa theo kịp. Trong bài viết này, chúng ta sẽ xem xét khái niệm về quy trình CI, ứng dụng của nó vào FPGA và ví dụ về cách thiết lập.

Continuous Integration và FPGA

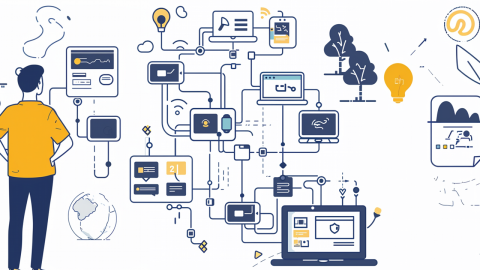

Nếu bạn chưa để ý, tôi gần như sống và thở với Continuous Integration. Dù là CI cho thiết kế PCB hay CI cho Hệ thống nhúng, tôi luôn tìm cách để cải tiến liên tục và tự động hóa các bản build cho mọi loại hệ thống. Một số phản hồi gần đây mà tôi nhận được là chưa có nhiều tiến bộ với FPGA và các hệ thống CI. Nguyên tắc thực sự đằng sau CI và FPGA giống như tất cả các hệ thống CI khác: tạo ra một môi trường build có thể lặp lại, có thể làm tất cả những công việc nặng nhọc cho chúng ta. Trong một hệ thống CI dựa trên FPGA, chúng ta thường sẽ thấy ba giai đoạn sau:

Hình 1: Các giai đoạn của một quy trình CI FPGA

Mỗi giai đoạn đều quan trọng và đều yêu cầu sự thiết lập riêng. Hãy cùng xem xét từng giai đoạn để hiểu chúng đại diện cho điều gì và làm thế nào để triển khai chúng.

Mô phỏng

Mô phỏng là một phần không thể thiếu của thiết kế FPGA. Xây dựng một hình ảnh FPGA để nạp vào mục tiêu có thể mất rất nhiều thời gian. Thay vì viết mã, xây dựng, và thử nghiệm nó trên phần cứng, mô phỏng cho phép chúng ta nhanh chóng kiểm tra mã của mình, hoặc Register-Transfer Level (RTL), trong một môi trường mô phỏng hành vi của FPGA. Thông thường điều này được thực hiện ở cấp độ người dùng, nhưng ngày càng trở nên phổ biến hơn khi tích hợp mô phỏng FPGA vào các quy trình CI. Điều này có nghĩa là ai đó sẽ đẩy mã của họ lên kho lưu trữ và một pipeline sẽ bắt đầu để chạy mô phỏng (tự kiểm tra) ở đâu đó trên đám mây. Để thực sự làm điều này “ở đâu đó trên đám mây”, cần phải tạo ra một môi trường có thể đóng gói hoặc container hóa thành một môi trường tự cung cấp. Chúng ta làm điều này bằng cách sử dụng thứ gọi là Docker container. Những thứ này hoạt động gần giống như các máy ảo có thể chạy ở bất cứ đâu. Container Docker này, ví dụ, tạo ra một môi trường container hóa cho phép người dùng chạy Icarus Verilog trong bất kỳ hệ thống Linux nào. Sau đó, chúng ta lấy container đó và sử dụng nó để tạo pipeline mô phỏng FPGA. Trong ví dụ này, bạn có thể thấy một pipeline “Hello World” đơn giản đang diễn ra trên đám mây sử dụng Icarus Verilog. Lưu ý rằng điều này có thể được thực hiện với bất kỳ công cụ mô phỏng FPGA nào.

Hình 2: Pipeline mô phỏng FPGA chạy bằng GitLab CI

Xây dựng

Giai đoạn thứ hai, cũng rất quan trọng trong pipeline FPGA, là giai đoạn xây dựng. Chúng ta muốn có thể tổng hợp, đặt và định tuyến, cũng như tạo ra một tệp bitstream cho thiết kế FPGA của mình. Thông thường, điều này được thực hiện bởi người dùng trong công cụ được cung cấp bởi nhà cung cấp (ví dụ: Xilinx, Intel, Microchip, v.v.). Thay vì xây dựng cục bộ, chúng ta muốn thực hiện quá trình xây dựng ở một nơi khác. Tuy nhiên, điều này có thể khá phức tạp vì các công cụ FPGA thường rất lớn về kích thước. Một phương pháp mà nhiều người dùng áp dụng là có một "máy xây dựng" chuyên dụng để chạy tất cả các pipeline xây dựng. Phương pháp này không tệ nhưng cũng không mở rộng được và có thể trở thành điểm hỏng duy nhất. Một số người đã thử container hóa các công cụ FPGA nhưng những hình ảnh đó có thể vượt quá 100 GB, khiến chúng không sử dụng được cho các ứng dụng đám mây. Một giải pháp trung gian mà tôi thấy hiệu quả là phương pháp cài đặt mạng. Ví dụ, tôi đã tạo một container chạy Vivado 2019.1 nhưng công cụ không được cài đặt trong hình ảnh (do đó kích thước hình ảnh nhỏ hơn 300 MB). Tôi đã cài đặt Vivado lên ổ đĩa mạng (trong trường hợp này là EFS trong AWS) và sau đó gắn nó trong container Docker của tôi. Vì tôi đang chạy pipeline của mình trong AWS nên độ trễ giữa EFS và EC2 (Nút Kubernetes) là không đáng kể.

Trong ví dụ này, tôi sử dụng một thiết bị Arty A7 từ Digilent để tạo bộ lọc số. Tôi đang sử dụng kịch bản xây dựng tự động để tạo tệp bitstream cho thiết bị của mình mỗi khi đẩy mã lên repository. Như bạn có thể thấy trong đầu ra, tôi đã thành công khi gọi Vivado mặc dù nó không tồn tại trong container Docker (tức là nó được gắn dưới dạng ổ đĩa ngoài).

Hình 3: Pipeline chạy xây dựng FPGA sử dụng Gitlab CI

Kiểm tra

Giai đoạn kiểm tra thực sự phụ thuộc vào từng cá nhân và dự án cụ thể. Mục tiêu của kiểm tra trong pipeline CI là tự động hóa càng nhiều càng tốt. Giống như tôi đã tự động hóa ví dụ DSP cho Arduinos với Analog Discovery 2, tôi cũng có thể làm điều tương tự ở đây. Để bao quát giải pháp kiểm tra tự động cho FPGA thì có thể sẽ vượt quá phạm vi của bài viết này. Nguyên tắc chính ở đây là đảm bảo rằng nó có thể lặp lại và chạy trong một môi trường được đóng gói hoặc container hóa. Điều quan trọng cần nhớ là kiểm tra là một phần quan trọng của pipeline CI và nên được triển khai ở bất kỳ mức độ nào mà người dùng có thể xử lý.

Kết luận

Trong bài viết này, chúng ta đã thảo luận về khái niệm các pipeline CI cho FPGA. Chúng ta đã xem xét ba giai đoạn quan trọng cấu thành pipeline FPGA: mô phỏng, xây dựng và kiểm tra. Chúng ta đã xem các ví dụ về pipeline mô phỏng và xây dựng, và thảo luận về tầm quan trọng của kiểm tra. Sau khi xem xét bài viết và các ví dụ, người dùng sẽ có thể hiểu được cấu trúc cơ bản để tạo ra một pipeline CI dựa trên FPGA.

Khi bạn đã sẵn sàng để xây dựng bảng FPGA tùy chỉnh của mình để hỗ trợ hệ thống nhúng, hãy sử dụng đầy đủ các tính năng thiết kế và bố trí PCB trong Altium Designer®. Khi bạn hoàn thành PCB và sẵn sàng chia sẻ thiết kế với cộng tác viên hoặc nhà sản xuất, bạn có thể chia sẻ các thiết kế đã hoàn thiện thông qua nền tảng Altium 365™. Tất cả những gì bạn cần để thiết kế và sản xuất các thiết bị điện tử tiên tiến đều có thể tìm thấy trong một gói phần mềm.

Chúng ta mới chỉ lướt qua bề mặt những gì có thể làm được với Altium Designer trên Altium 365. Bắt đầu dùng thử miễn phí Altium Designer + Altium 365 ngay hôm nay.