Bắt đầu với MCU nRF52 trên PCB

Xem cách bắt đầu với nRF52 trong bố trí PCB. Chúng tôi sẽ hướng dẫn cách sử dụng phiên bản gói BGA có chân cắm mảnh của linh kiện này.

Nhấn vào đây để chuyển đến phần nhúng trình xem và duyệt qua dự án này

Hầu hết các nhà sản xuất bán dẫn đã phát triển và tung ra dòng vi điều khiển của riêng họ, và Nordic Semiconductor cũng không ngoại lệ. Một trong những sản phẩm nổi tiếng nhất của họ là nRF52, một SoC có khả năng RF với bộ thu phát tích hợp. Linh kiện này nhỏ gọn, cung cấp số lượng I/O cao và có số phần mà được đóng gói trong BGA mảnh.

Trong bài viết này, tôi sẽ trình bày một ví dụ về bố trí PCB sử dụng phiên bản đóng gói BGA mảnh của nRF52. Cuối bài viết, bạn sẽ có cơ hội tải về các tệp nguồn cho dự án này. Không chần chừ nữa, hãy bắt đầu với một ví dụ về bố trí PCB bao gồm nRF52.

Đối với những người xem muốn theo dõi toàn bộ quá trình thiết kế cho linh kiện này, chúng tôi đã tạo danh sách phát sau đây hướng dẫn người dùng qua quá trình sử dụng nRF52 trong bố trí PCB. Cụ thể, chúng tôi sẽ hướng dẫn cách sử dụng phiên bản có mật độ cao (khoảng cách giữa các bóng 0,35 mm) của linh kiện này trong một thiết kế yêu cầu một số kỹ thuật thiết kế HDI. Chúng tôi cũng sẽ trình bày toàn bộ hành trình kỹ thuật mà chúng tôi đã trải qua để đạt được phiên bản cuối cùng của mô-đun nRF52 của chúng tôi.

Thiết kế Phía Trước

nRF52 có một số gói khác nhau với kích thước nhỏ gọn. Con chip này đã trở nên phổ biến như một vi điều khiển có khả năng Bluetooth với số lượng chân vừa phải và các giao diện kỹ thuật số tiêu chuẩn, bao gồm khả năng sử dụng USB trong thiết bị. Linh kiện này nhắm đến các thiết bị nhúng nhỏ với kết nối Bluetooth 5.

Trong dự án này, linh kiện chúng tôi sẽ sử dụng là nRF52840-CKAA-R7, một WLCSP 93 chân với dấu chân BGA. Bộ xử lý này được biết đến với khả năng hoạt động ở mức công suất thấp khi không phát sóng, vì vậy có thể sử dụng nó với một pin nhỏ. Chúng tôi sẽ thêm một số mạch điều chỉnh pin và bảo vệ cực cho hệ thống này để nó có thể hoạt động thành công với nguồn pin.

Dấu chân nRF52840 WLCSP

Dấu chân cho nRF52840-CKAA-R7 được hiển thị dưới đây. Thanh đo giữa các bóng cho thấy khoảng cách là 0.35 mm. Đây là một khoảng cách rất nhỏ và sẽ yêu cầu một số kỹ thuật thiết kế được sử dụng trong các thiết kế HDI.

Các Linh Kiện Quan Trọng Khác

Chúng tôi sẽ đi vào chi tiết về bố trí chân và phân phối chân cho linh kiện này trong một trong những phần dưới đây. Hiện tại, sẽ có một số linh kiện khác xuất hiện trong thiết kế:

- TPS70933DBVR - Bộ điều chỉnh tuyến tính dòng thấp

- FR015L3EZ - Bảo vệ cực ngược dòng thấp

- BD33HC0MEFJ-ME2 - Bộ điều chỉnh 3V3/1A cho mạch logic

- PCF8523TK - Đồng hồ thực tế (RTC) với giao diện I2C

- CAT24C512WI-GT3 - EEPROM 512 KB

Thiết bị ban đầu sẽ cần kết nối với pin LiPo thông qua một kết nối 2 chân tiêu chuẩn, và chúng tôi sẽ cần bao gồm ít nhất một tiêu đề để truy cập I/O và lập trình bo mạch. Số lượng I/O lớn hơn so với chúng tôi thường lắp vào một tiêu đề duy nhất, vì vậy đó là quyết định liệu có nên bao gồm thêm một tiêu đề thứ hai chỉ để truy cập I/O hay không. Tạm thời, chúng tôi sẽ tiếp tục với kết nối pin và một tiêu đề I/O duy nhất, và chúng tôi luôn có thể thêm một kết nối khác sau này.

Bắt đầu: Sơ đồ

Sơ đồ cho thiết bị này không quá phức tạp và tất cả các mạch sẽ vừa vặn trên một trang. Tôi sẽ hiển thị các khu vực khác nhau của sơ đồ một cách riêng biệt để toàn bộ thiết kế được rõ ràng và dễ đọc.

Đầu tiên, hãy xem xét phần nguồn. Trong thiết bị này, nguồn 3V3 được cung cấp bởi một LDO ít nhiễu, dòng điện thấp với dòng điện định mức 150 mA. LDO lấy nguồn điện từ pin (VBAT) làm đầu vào và chuyển đổi này thành đầu ra 3V3 mong muốn.

Dựa vào các kết nối mạng cho VBAT và VDD1, chúng ta thấy rằng có hai cách để cung cấp nguồn cho bảng mạch:

- Áp dụng 3V3 trực tiếp vào VDD1, chẳng hạn qua một cổng pin

- Áp dụng điện áp trực tiếp vào mạng VBAT, cũng qua một trong các kết nối

Trong trường hợp đầu tiên, bạn chỉ cấp nguồn cho MCU và RTC; sẽ không có nguồn cho các thiết bị ngoại vi. Trong trường hợp sau, bạn sẽ cung cấp nguồn cho toàn bộ hệ thống, và bây giờ VDD1 sẽ là một đầu ra chứ không phải là một đầu vào.

Bạn sẽ nhận thấy rằng một bộ điều chỉnh thứ hai đang cung cấp nguồn 3V3 cho mạch VDD2. Bộ điều chỉnh này bao gồm một chân enable, vì vậy thiết bị có thể khởi động đầu tiên sử dụng VDD1, và sau đó các thiết bị ngoại vi (trong trường hợp này là EEPROM) có thể được cấp nguồn sử dụng VDD2. Điều này cho phép thiết bị có khả năng tắt các thiết bị ngoại vi của mình khi thiết bị không được sử dụng bằng cách chuyển đổi chân VDD2_ENABLE. Nếu chúng ta có bất kỳ thiết bị ngoại vi nào khác mà chúng ta muốn bao gồm trong thiết kế này không trung tâm với việc khởi động thiết bị, chúng ta sẽ muốn kết nối những thiết bị này với VDD2 thay vì VDD1.

Tiếp theo, hãy xem các kết nối nRF52840. Những kết nối này được mượn từ bảng phát triển Nordic và bộ kết nối gốc trên các thành phần của họ có thể được truy cập trong các tệp thiết kế Altium của họ.

Ở đây, tôi đã phân loại một số giao diện, và mạch hỗ trợ chủ yếu bao gồm các tinh thể tham chiếu và một số tụ điện. Các tụ điện có kích thước từ lớn cho việc giảm nhiễu tổng thể, xuống đến kích thước nhỏ (0201) cho việc lọc trên đường ray VDD1. Vẫn còn rất nhiều chân còn lại trong thành phần này, và chúng có thể được sử dụng cho các thiết bị ngoại vi khác. Cuối cùng, tôi sẽ phân chia một số I/O bổ sung và giao diện SPI ra một tiêu đề chân như được hiển thị sau này trong loạt video.

Nếu bạn xem chân E1, bạn sẽ thấy kết nối ăng-ten. Ban đầu, bắt đầu từ sơ đồ và bố trí gốc trong thiết kế tham khảo, mạng lưới khớp trở kháng này đã sử dụng các giá trị tụ đầu ra khác nhau. Mạng lưới khớp trở kháng được hiển thị dưới đây được xác định bằng cách đảo ngược kỹ thuật ăng-ten trở kháng với một máy tính trực tuyến và chỉnh sửa mạng lưới khớp sao cho nó đối xứng. Việc thay thế tụ đầu ra 0.8 pF trong thiết kế tham khảo bằng tụ đầu ra 1.2 pF được hiển thị dưới đây tạo ra hiệu suất cơ bản giống nhau.

Điều này cơ bản kết thúc phần thu thập sơ đồ, và các mạch còn lại đều đơn giản để triển khai. Chúng ta giờ có thể chuyển sang bố trí PCB.

Bố Trí PCB

Một khi trong bố trí PCB, chúng ta có một số nhiệm vụ quan trọng cần hoàn thành để sử dụng nRF52840 trong WLCSP:

- Xác định một cấu trúc xếp chồng và phân loại BGA

- Đặt ăng-ten như một yếu tố in

- Đặt và định tuyến các IC khác sao cho chúng không gây cản trở cho phần RF

Cấu Trúc Xếp Chồng và Phân Loại

Yếu tố chính quyết định chiến lược xếp chồng và phân bố là khoảng cách giữa các chân trên gói nRF52. Người đọc có thể chú ý ở trên rằng khoảng cách giữa các chân là 0.35 mm. Kích thước pad trong bản vẽ chân của tôi là 0.212 mm, đây là kích thước phù hợp theo tiêu chuẩn IPC đối với bản vẽ chân BGA. Khoảng cách chéo qua các pad là 0.495 mm. Các phép đo này được hiển thị bên dưới.

Nếu chúng ta cố gắng sử dụng phương pháp phân bố dạng xương cá với vias xuyên lỗ để định tuyến vào các chân bên trong, chúng ta chỉ còn lại khoảng 1-2 mils không gian giữa các vias và các pad lân cận. Đây là khoảng cách quá nhỏ để hầu hết các nhà sản xuất có thể khắc chính xác. Điều này cũng đòi hỏi kích thước mũi khoan rất nhỏ khoảng 4 mil với đường kính pad từ 8 đến 9 mil. Những giá trị này quá nhỏ để có thể làm việc trong sản xuất tiêu chuẩn.

Do đó, tôi đã sử dụng phương pháp phân tán qua lỗ trên pad với các lỗ vias mù và vias chôn để kết nối tới các lớp bên trong. Vì kích thước pad khoảng 8.3 mil, chúng ta có thể sử dụng vias mù/chôn 4 mil với pad 8 mil. Để duy trì tỷ lệ khía cạnh 1:2, chúng ta sẽ cần độ dày lớp ngoài 4 mil cho các vias mù/chôn. Điều này sẽ tạo ra tổng cộng 6 lớp như được hiển thị trong bản xếp chồng dưới đây.

Đặt Vị Trí Linh Kiện và Ăng-ten

Sau khi hoàn thành bản xếp chồng và phân tán, vị trí đầu tiên của tôi cho bảng mạch này được hiển thị dưới đây. Tôi đã bao gồm một số đa giác cho việc định tuyến nguồn trước khi hoàn thành các kết nối còn lại. Vị trí ban đầu của tiêu đề 6 chân được sử dụng cho việc lập trình và đọc điện áp. Điểm tiếp theo cần xem xét là vị trí đặt ăng-ten, và cuối cùng, chúng ta có thể hoàn thành với việc phá vỡ I/O ra các kết nối.

Trong thiết kế này, chúng ta sẽ sử dụng ăng-ten in để gửi và nhận tín hiệu không dây. Vị trí tốt nhất để đặt ăng-ten in cho nRF52 là dọc theo mép bảng mạch. Điều này sẽ giữ ăng-ten tránh xa khỏi phần kỹ thuật số. ăng-ten kết nối với chân E1 trên nRF52840.

Nếu bạn xem thiết kế tham khảo của nRF52, bạn sẽ thấy họ cung cấp một ví dụ về ăng-ten in có thể được tích hợp vào các thiết kế khác. ăng-ten này là một ăng-ten bốn phần sóng, và điều này có thể được xác minh bằng cách tính toán chiều dài của ăng-ten và so sánh nó với bước sóng của tín hiệu 2.45 GHz trong cấu hình microstrip không có đất. Mạng lưới khớp trở kháng được hiển thị trong sơ đồ trên nên cung cấp đủ sự khớp nối cho phép, xét đến sự khác biệt trong cấu trúc xếp chồng của bo mạch này.

Header Lập Trình SWD và Header I/O

Nếu bạn quyết định sản xuất bo mạch này, bạn sẽ cần phải lập trình nó. Tài liệu nRF52840 cung cấp hướng dẫn lập trình thiết bị thông qua giao thức SWDIO chỉ sử dụng 4 chân:

- VDD (nguồn hệ thống)

- SWDIO (J2)

- SWDCLK (H2)

- GND

Vì vậy, tôi đã thay thế header 1x6 chân bằng một header SWD vì đây là một cáp tiêu chuẩn được sử dụng để lập trình nhiều bo mạch vi điều khiển (tôi cũng có một số cáp SWD trong phòng thí nghiệm của mình). Lưu ý rằng chân nReset (K6) là tùy chọn cho việc lập trình, nhưng tôi sẽ bao gồm nó trong bố trí chân của header SWD cùng với một kết nối VBAT. Bố trí chân cuối cùng trên header SWD của tôi được hiển thị dưới đây.

Lập trình viên mà tôi thích sử dụng cho loại thiết bị này là lập trình viên PRESTO, có thể tìm mua tại ASIX.net. Lập trình viên này hỗ trợ một danh sách dài các thiết bị, bao gồm nRF52840 và một số sản phẩm khác của Nordic. Bạn sẽ phải tạo ra các cấu hình chân cắm tùy chỉnh cho cáp trên PRESTO, nhưng việc này khá đơn giản khi sử dụng dây dẫn linh hoạt.

Sau đó, tôi quyết định thay đổi lựa chọn ban đầu từ header 1x6 sang header 2x7 để có thể mở rộng thêm các I/O. Header được đặt ở góc trên bên trái của bảng mạch. Tôi đã thêm các điện trở nối tiếp 22 Ohm trên các I/O này để làm chậm tín hiệu vào hoặc ra khỏi bảng mạch trong trường hợp EMI trở nên vấn đề với các kết nối này. Nếu hóa ra chúng không cần thiết, tôi luôn có thể thay thế chúng bằng điện trở 0 Ohm.

Bố Cục Hoàn Thiện

Bố cục PCB đã hoàn thiện được hiển thị trong hình dưới đây. Tôi đã thêm một số logo, đặt số phận trong phần dưới bên phải của bảng mạch, và căn chỉnh các điện trở trên các dòng I/O dọc theo nửa dưới của tiêu đề pin. Tôi cũng đã làm một số công việc dọn dẹp cuối cùng trên silkscreen để tất cả các chỉ định đều rõ ràng và không có sự chồng chéo. Tại thời điểm này, thiết kế đã vượt qua DRC cuối cùng và sẵn sàng để sản xuất.

Tệp Nguồn và Các Phiên Bản Cải Tiến Tương Lai

Mặc dù việc định tuyến có thể được cải thiện ở một số nơi chỉ để làm sạch truy cập I/O, bảng mạch sẽ hoạt động và tôi hài lòng với kết quả cuối cùng. Một số tính năng bổ sung có thể được thêm vào bao gồm một cổng USB và IC quản lý sạc USB để thiết bị có thể được sạc từ bus 5V tiêu chuẩn trên một cắm USB.

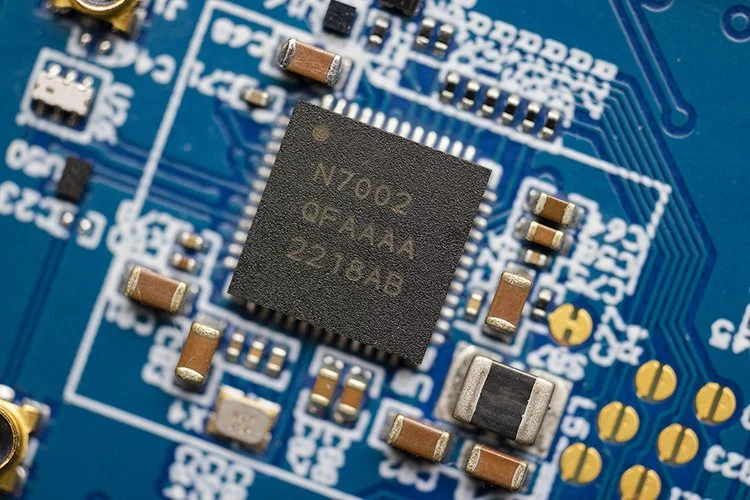

Một thành phần khác có thể được thêm vào thiết kế là IC đồng hành Nordic cung cấp quyền truy cập WiFi cho các MCU thuộc dòng nRF52. Vào tháng 8 năm 2022, Nordic đã công bố việc phát hành phiên bản mới nhất của dòng nRF: nRF7002. SoC này cung cấp hỗ trợ WiFi 6 hai băng tần với mức tiêu thụ điện năng cực thấp như một thiết bị đồng hành cho các sản phẩm nRF52 hoặc nRF53. Tôi sẽ xem xét IC đồng hành này trong một dự án và video sắp tới.

Hiện tại, nhấn vào liên kết này để tải xuống một tệp lưu trữ ZIP với các tệp nguồn của dự án. Bạn cũng có thể sử dụng liên kết tải xuống ở phần nhúng phía trên để truy cập các tệp nguồn.

Các thành phần mật độ cao với các phần RF dễ dàng được đặt và định tuyến với bộ công cụ CAD đầy đủ trong Altium Designer®. Khi bạn đã hoàn thành thiết kế và muốn gửi các tệp cho nhà sản xuất, nền tảng Altium 365™ giúp bạn dễ dàng hợp tác và chia sẻ các dự án của mình.

Chúng tôi mới chỉ khám phá bề mặt của những gì có thể thực hiện với Altium Designer trên Altium 365. Bắt đầu dùng thử miễn phí Altium Designer + Altium 365 ngay hôm nay.