Cách Thiết Kế Phiếu Kiểm Tra PCB Của Bạn Và Những Gì Bạn Có Thể Kiểm Tra

Khi tốc độ hoạt động của các linh kiện tăng lên, việc kiểm soát trở kháng trở nên phổ biến hơn trong các hệ thống số, tương tự, và tín hiệu hỗn hợp. Nếu giá trị trở kháng kiểm soát cho một kết nối liên lạc không chính xác, việc xác định vấn đề này trong quá trình kiểm tra mạch có thể rất khó khăn. Những sai lệch nhỏ có thể không khiến cho bảng mạch bị lỗi, nhưng việc xác định trở kháng không chính xác là nguyên nhân của bất kỳ sự cố kiểm tra nào cũng khó khăn, đặc biệt là nếu không đặt các điểm kiểm tra và cấu trúc kiểm tra chính xác trên bảng mạch để hỗ trợ kiểm tra trở kháng trên bảng mạch trống.

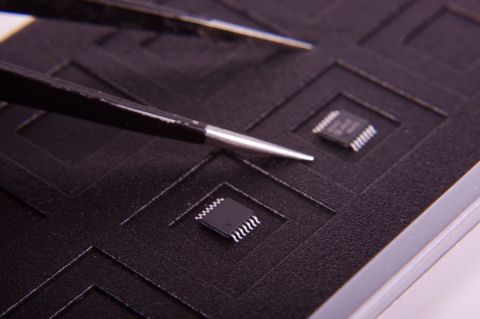

Vì trở kháng phụ thuộc vào nhiều tham số (hình dạng dấu vết, độ dày lớp cách điện, và giá trị Dk của lớp cách điện), do đó, phần lớn các PCB hiện nay được kiểm tra về trở kháng kiểm soát. Tuy nhiên, việc kiểm tra thường được thực hiện trên một phiếu kiểm tra PCB, được sản xuất trên cùng một tấm với PCB (thường dọc theo một cạnh). Nếu bạn muốn nhanh chóng hoàn thành các vòng thiết kế bảng mạch và hỗ trợ cho các thiết kế tương lai, bạn có thể cân nhắc thiết kế một phiếu kiểm tra và giữ nó sẵn sàng cho các thiết kế tương lai. Ngoài ra, việc cung cấp cho nhà sản xuất của bạn đủ tài liệu về hình dạng kết nối liên lạc đề xuất của bạn là một sự hỗ trợ lớn trong việc đảm bảo nhà sản xuất tạo ra phiếu kiểm tra chính xác.

Mẫu thử PCB tách biệt hay tích hợp?

Mục tiêu của bất kỳ phiếu thử nghiệm nào là để chính xác bắt được cấu trúc chồng chất dự định của bảng mạch và tạo điều kiện cho việc kiểm tra trở kháng kết nối chính xác. Có một số cách để làm điều này. Trong một phiếu thử nghiệm cho trở kháng kiểm soát, nhà sản xuất có thể để lại một ít không gian ở rìa bảng để đặt một số cấu trúc thử nghiệm cho việc kiểm tra trở kháng kiểm soát. Phiếu thử nghiệm cũng có thể được chọn từ thư viện của nhà cung cấp, được thiết kế theo tiêu chuẩn công nghiệp (ví dụ, phiếu D của Phụ lục A IPC 2221B), hoặc được tạo ra bằng cách sử dụng một số phần mềm (ví dụ, Bộ sinh phiếu thử nghiệm Gerber IPC 2221B).

Đôi khi, một phiếu kiểm tra được tích hợp trực tiếp vào PCB thực tế, thay vì được tạo ra như một phần riêng biệt trên cùng một tấm. Trong trường hợp này, phiếu kiểm tra có thể không có vẻ ngoài điển hình mà người ta mong đợi từ một phiếu kiểm tra được tạo ra hoặc cung cấp bởi nhà cung cấp. Kella Knack mô tả các cấu trúc kiểm tra phổ biến để bao gồm trong một phiếu kiểm tra riêng biệt (nếu bạn là nhà sản xuất) hoặc trực tiếp trên một bảng mạch nguyên mẫu (nếu bạn là nhà thiết kế) trong một bài viết gần đây.

TRANSLATE:

Việc đặt các cấu trúc kiểm tra trực tiếp trên một tấm mạch có vẻ như là lãng phí không gian, nhưng nó thực sự hỗ trợ rất nhiều cho việc kiểm tra mạch trong quá trình chế tạo mẫu và thậm chí trong suốt quá trình sản xuất quy mô lớn. Nếu bạn đang thiết kế các hình dạng kết nối không phổ biến, bạn cần đánh giá trở kháng trước khi sản xuất hàng loạt. Việc thiết kế một tấm mạch với các thiết kế kết nối của bạn và kiểm tra chúng ngay tại nơi làm việc không phải là ý kiến tồi. Bạn sẽ phải trả trước cho một tấm mạch kiểm tra, nhưng bạn có thể tiết kiệm được một lần chỉnh sửa mạch sau này nếu bạn có thể lấy được các số đo cần thiết trước khi sản xuất.

Hơn cả Trở Kháng

Trở kháng kết nối, dung lượng PDN, tổn thất dẫn điện, và độ trễ truyền dẫn đều có thể được đo lường với các cấu trúc thử nghiệm phù hợp. Các cấu trúc thử nghiệm khác được đặt trên một phiếu thử nghiệm được thiết kế riêng có ích cho việc xác định hằng số điện môi của lớp cách điện. Khi bạn bước vào lĩnh vực sóng vi ba/sóng mm, các yếu tố như tổn thất chèn và bức xạ khoang nên được kiểm tra để đảm bảo các tín hiệu tương tự trên các đường dẫn có trở kháng kiểm soát không trải qua sự suy giảm đáng kể.

Phiếu thử nghiệm cũng có thể được đưa qua các bài kiểm tra sốc nhiệt, mô phỏng tái hợp, đo nhiệt độ chuyển pha kính, đo điện trở DC của dẫn điện, hoặc bất kỳ bài kiểm tra nào bạn có thể tưởng tượng. Một phiếu thử nghiệm cũng cho nhà sản xuất cơ hội để đánh giá quy trình sản xuất và chất lượng, đảm bảo rằng bảng mạch mới của bạn đáp ứng các tiêu chuẩn độ tin cậy. Kết quả từ các bảng phải nằm trong khoảng 5% giá trị của thông số kỹ thuật.

Đổi mới ở Tần số Cao

Nếu bạn bắt đầu làm việc với các tần số cực cao và cần thực hiện chuyển đổi lớp, sử dụng các vật liệu đặc biệt, hoặc làm việc với các bảng mạch HDI, tần số cao có thể tạo ra các vấn đề về tính toàn vẹn tín hiệu khác mà khó có thể giải quyết. Trong các bảng mạch hoạt động ở hàng 10 GHz, tất cả các điểm được kiểm tra trên một phiếu kiểm tra tiêu chuẩn cho hệ thống số tốc độ cao đều quan trọng và nên được xem xét trên một phiếu kiểm tra tần số cao. Có những phép đo quan trọng khác cần được thu thập để đảm bảo tính toàn vẹn tín hiệu và EMI phát ra thấp.

Sau một số bài viết trước đây về các vấn đề SI/EMI trong các hệ thống analog tần số cao khác nhau, tôi đã nhận được một số câu hỏi về các loại via được sử dụng trong các bảng mạch mmWave, cụ thể là liệu các via xuyên lỗ có mạ nên được sử dụng ở những tần số này hay không. Jon Coonrod đã thảo luận về điểm này và một số điểm quan trọng về việc xác định tính nhất quán của hằng số điện môi trong suốt các kết nối. Việc kích thước hóa và khoan lùi các via này để sử dụng ở những tần số này là rất quan trọng vì một via có kích thước không phù hợp với một đoạn stub dài có thể tạo ra phản xạ quá mức, xuất hiện như là tổn hao chèn đạt ~6 dB hoặc hơn.

Với một kế hoạch thông minh, bạn có thể đặt tất cả các mạch vi sóng/mm sóng quan trọng của mình lên lớp bề mặt và tránh chuyển đổi lớp. Trong trường hợp bạn cần sử dụng chuyển đổi lớp hoặc kiểm tra một cấu trúc kết nối độc đáo (ví dụ, hướng dẫn sóng tích hợp vào vật liệu nền), điều này nên được kiểm tra trên một coupon kiểm tra về trở kháng, tổn thất chèn, và tổn thất tổng thể. Cụ thể, các chuyển đổi lớp có thể được kiểm tra bằng phép đo phản xạ thời gian miền (TDR). Sự không khớp trở kháng cao giữa các phần đường truyền và cấu trúc via sẽ xuất hiện như một điểm giảm trong tín hiệu phản xạ, cho phép bạn đánh giá các cấu trúc này để sử dụng trong đợt sản xuất.

Nếu bạn cần thiết kế một PCB test coupon hoặc bao gồm các cấu trúc kiểm tra trong một PCB sản xuất, các công cụ sắp xếp và phân tích trong Altium Designer® cung cấp cho bạn khả năng tạo ra bất kỳ cấu trúc kiểm tra nào bạn có thể tưởng tượng cho một test coupon hoặc một bảng mạch hoàn chỉnh. Bạn sẽ có thể thiết kế các kết nối và cấu trúc xếp chồng của mình để đáp ứng tất cả các yêu cầu về hiệu suất quan trọng, và bạn sẽ có tất cả các tính năng thiết kế cần thiết để chuẩn bị cho việc sản xuất các bảng mạch mới của mình.

Bây giờ bạn có thể tải về một phiên bản dùng thử miễn phí của Altium Designer và tìm hiểu thêm về các công cụ sắp xếp, mô phỏng và lập kế hoạch sản xuất tốt nhất trong ngành. Nói chuyện với một chuyên gia Altium ngày hôm nay để tìm hiểu thêm.