Hướng dẫn Đặt Tụ Bù và Tụ Nối Song Song

Vấn đề về tính toàn vẹn của nguồn điện thường được nhìn nhận từ góc độ của nguồn cung cấp, nhưng việc xem xét đầu ra từ các IC cũng quan trọng không kém. Tụ bù và tụ lọc được thiết kế để bù đắp cho sự biến động của nguồn điện trên PDN, điều này đảm bảo mức tín hiệu của bạn ổn định và một điện áp liên tục được nhìn thấy tại các chân nguồn/đất trên một IC. Chúng tôi đã tổng hợp một số hướng dẫn thiết kế tụ bù và tụ lọc quan trọng để giúp bạn sử dụng thành công các linh kiện này trong PCB tiếp theo của mình. Trong blog này, chúng tôi sẽ giải quyết vấn đề tụ bù so với tụ lọc.

Hai Vấn Đề Liên Quan Đến Tính Toàn Vẹn Nguồn Điện

Tụ ghép nối và tụ lọc được sử dụng để giải quyết hai vấn đề khác nhau liên quan đến tính toàn vẹn của nguồn điện. Mặc dù những vấn đề về tính toàn vẹn nguồn điện này có liên quan, chúng biểu hiện theo những cách khác nhau. Điểm đầu tiên cần lưu ý là các thuật ngữ “tụ ghép nối” và “tụ lọc” khi được sử dụng cho tính toàn vẹn nguồn điện là không chính xác; chúng không ghép nối hay lọc bất cứ thứ gì. Chúng cũng không truyền “nhiễu” xuống mặt đất; chúng chỉ đơn giản là sạc và xả theo thời gian để bù đắp cho sự biến động của nhiễu. Những thuật ngữ này đề cập đến chức năng của các tụ điện này như một phần của chiến lược tính toàn vẹn nguồn điện.

Đầu tiên, hãy xem xét tụ bù. Nói chung, mục đích của việc đặt tụ bù trên PCB là để đảm bảo điện áp giữa đường ray/ mặt phẳng nguồn và mặt phẳng đất luôn ổn định trước tiếng ồn nguồn cung cấp tần số thấp, tiếng vang trên PDN, và bất kỳ biến động điện áp nào khác trên PDN. Khi được đặt giữa mặt phẳng nguồn và đất, tụ bù hoạt động song song với các mặt phẳng, làm tăng tổng dung lượng của PDN. Thực tế, chúng bù đắp cho sự thiếu hụt dung lượng giữa các mặt phẳng và giảm trở kháng PDN sao cho bất kỳ tiếng vang nào trong điện áp PDN đều được giảm thiểu.

Giờ hãy xem xét tụ điện bypass. Chúng cũng được thiết kế để duy trì một điện áp ổn định trong mạng lưới phân phối điện (PDN) và một mạch tích hợp (IC) điều khiển, nhưng điện áp mà chúng bù đắp là giữa chân ra của IC và mặt đất của PCB. Mặc dù chúng được đặt giữa chân cấp điện của IC và kết nối mặt đất, chúng thực hiện một chức năng khác, đó là chống lại hiện tượng nhảy điện áp từ tụ điện xuống mặt đất. Khi một IC số chuyển mạch, độ tự cảm nhiễu trong dây kết nối, gói, và chân gây ra điện áp giữa đầu ra của bộ điều khiển và mặt đất tăng lên. Tụ điện bypass phát ra một điện áp hướng ngược lại với điện áp nhảy mặt đất, lý tưởng là khiến tổng biến động điện áp cộng dồn thành không.

Trong mô hình trên, có một vòng kín bao gồm tụ điện bypass (CB) và độ tự cảm lạc đường L1 trên kết nối gói IC/mặt đất. Lưu ý rằng điện áp nảy mặt đất V(GB) được đo giữa chân đầu ra và mặt phẳng mặt đất. Các độ tự cảm còn lại đều là các thành phần nhiễu, ảnh hưởng đến thời gian phản ứng của tụ điện bypass để bù đắp cho điện áp nảy mặt đất. Trong một mô hình lý tưởng, điện áp mà tụ điện bypass nhìn thấy sẽ bù đắp cho điện áp nảy mặt đất được tạo ra bởi cuộn cảm lạc đường L1 trong quá trình chuyển mạch.

Hướng dẫn Đặt Tụ Điện Bypass

Nếu bạn xem xét cách xảy ra hiện tượng nảy mặt đất của tụ điện, bạn sẽ thấy rõ nên đặt tụ bypass ở đâu. Do sự cảm ứng nhiễu phụ trong mô hình mạch trên, một tụ bypass nên được đặt càng gần các chân nguồn và mặt đất càng tốt để giảm thiểu những cảm ứng này. Điều này phù hợp với lời khuyên bạn sẽ tìm thấy trong nhiều ghi chú ứng dụng và bảng dữ liệu linh kiện.

Có một khía cạnh khác cần xem xét, liên quan đến cảm ứng nhiễu phụ, đó là cách kết nối được định tuyến đến IC. Thay vì định tuyến một đường dẫn ngắn từ tụ đến chân IC, bạn nên kết nối tụ trực tiếp với các lớp nguồn và mặt đất thông qua vias. Hãy chắc chắn tuân thủ yêu cầu về khoảng cách pad và đường dẫn trong sắp xếp này.

Tại sao lại như vậy? Lý do là bởi vì sự sắp xếp của mặt đất/mặt nguồn (miễn là các lớp nằm cạnh nhau) sẽ có độ tự cảm nhiễu rất thấp. Thực tế, đây là nguồn gốc của độ tự cảm nhiễu thấp nhất trên bảng mạch của bạn. Bạn có thể thực hiện một sắp xếp tốt hơn nếu bạn có thể đặt tụ bypass ở mặt dưới của bảng mạch.

Hướng dẫn Thiết kế Tụ Decoupling

Sau khi bạn xác định kích thước tụ bù PCB mà bạn cần trong PDN của mình, bạn sẽ cần phải đặt nó ở đâu đó để đảm bảo rằng nó có thể bù đắp cho sự biến động điện áp đầu vào. Thực tế, tốt nhất là sử dụng nhiều tụ, vì chúng sẽ được sắp xếp song song, và sự sắp xếp song song sẽ cung cấp độ cảm kháng mắc nối tiếp thấp hơn.

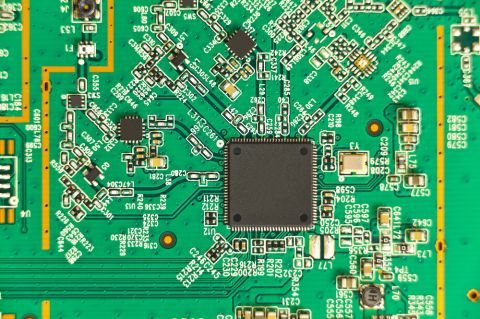

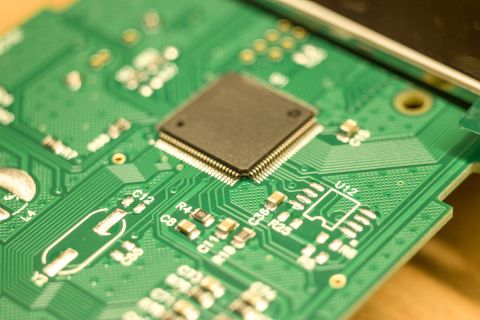

Các hướng dẫn cũ sẽ nói rằng bạn có thể đặt chúng ở bất cứ đâu trên bảng mạch. Tuy nhiên, hãy cẩn thận với điều này vì điều này có thể làm tăng cảm kháng nhiễu mà tụ bù và IC mục tiêu gặp phải, điều này làm tăng trở kháng PDN và sự nhạy cảm với EMI. Thay vào đó, đối với các IC có tốc độ biên nhanh, bạn nên đặt chúng gần IC mục tiêu hơn. Hình ảnh dưới đây cho thấy một sắp xếp điển hình của tụ bù và tụ bù gần một IC. Đây là một sắp xếp tối ưu cho các mạch tốc độ cao vì sẽ có cảm kháng nhiễu rất thấp giữa các tụ và IC cho tất cả các đường tín hiệu.

Lưu ý rằng đây là hình ảnh nhìn từ bên và cho thấy một sắp xếp các pad có vẻ lạ, nhưng các kết nối giữa các lớp và lớp bề mặt là những điểm quan trọng. Điều hướng trở lại lớp bên trong thay vì lớp bề mặt giúp giảm tối thiểu độ tự cảm của vòng.

Hãy Cẩn Thận Khi Mô Phỏng Trở Kháng PDN

Hãy nhớ rằng trở kháng PDN quyết định kích thước của bất kỳ dao động điện áp tạm thời nào trên PDN (được đo giữa nguồn và mặt đất). Tuy nhiên, các tụ điện bypass cũng được kết nối giữa nguồn và mặt đất, vì vậy chúng cũng là một phần của PDN! Việc đặt tụ điện bypass và decoupling, cũng như dung kháng và cảm kháng nhiễu, sẽ cùng nhau quyết định phổ trở kháng của PDN, tạo ra một cấu trúc phức tạp của cộng hưởng và chống cộng hưởng.

Mặc dù bạn có thể tìm thấy một số công cụ tối ưu hóa PDN trực tuyến, chúng giả định rằng tất cả các yếu tố mạch nhiễu đều bằng không, điều này không phản ánh thực tế. Trong một mô hình mạch, cách bạn sắp xếp các tụ điện decoupling/bypass (từ nhỏ đến lớn hoặc từ lớn đến nhỏ) không quan trọng. Trong một bố cục thực tế, các yếu tố nhiễu quan trọng (như đã được thảo luận ở trên), đặc biệt là đối với các IC tốc độ cao/mức độ thấp.

Với các công cụ thiết kế bố trí và sơ đồ mạch trong Altium Designer®, bạn có thể dễ dàng áp dụng các hướng dẫn thiết kế tụ bù và tụ lọc mạch in PCB tốt nhất cho PCB tiếp theo của mình. Bộ công cụ mô phỏng mạch sẽ giúp bạn có cái nhìn về cấu trúc cộng hưởng PDN của mình. Bạn cũng sẽ có quyền truy cập vào một loạt các công cụ để quản lý dữ liệu linh kiện, chuẩn bị cho sản xuất, cũng như thông tin về việc chọn tụ lớn so với tụ lọc.

Bây giờ bạn có thể tải về bản dùng thử miễn phí của Altium Designer và tìm hiểu thêm về các công cụ thiết kế bố trí, mô phỏng và lập kế hoạch sản xuất tốt nhất trong ngành. Nói chuyện với một chuyên gia Altium ngày hôm nay để tìm hiểu thêm.