PCB用のスキーマティック・ネットリストとは何ですか?

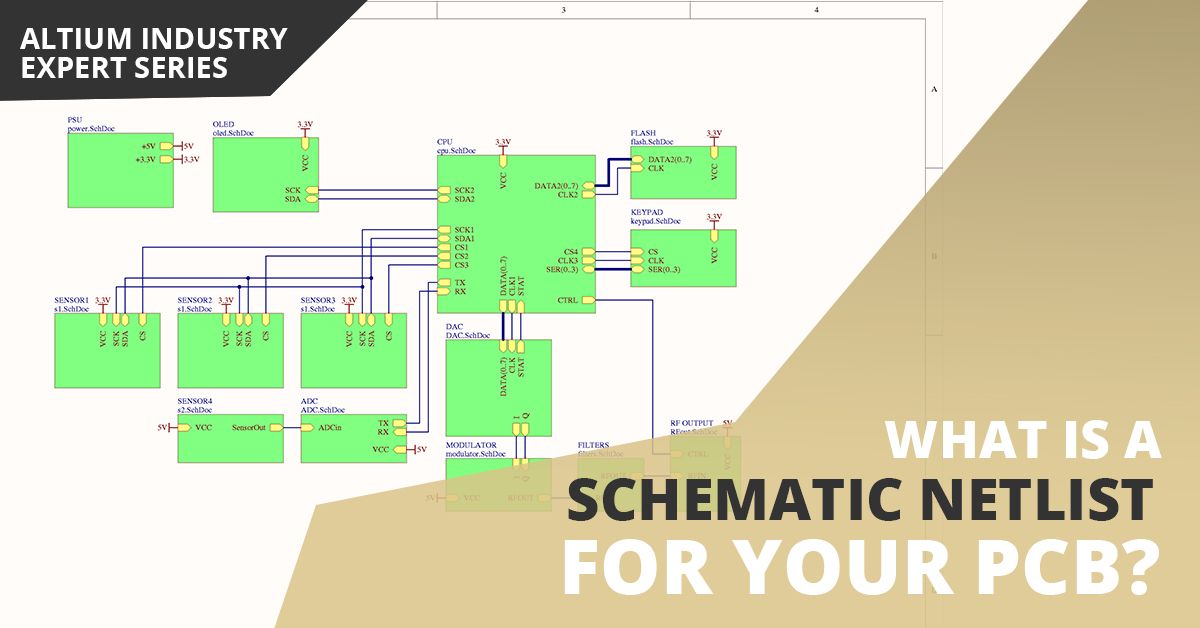

次の素晴らしい回路図を作成した場合、設計ソフトウェアの背後には多くのことが行われています。回路図内のコンポーネント間の接続は、少数の論理的および電気的識別子に還元することができます。回路図は異なるコンポーネントとピン間の接続を示すグラフィカルな画像を提供するかもしれませんが、設計についてすべてを本当に理解するためには、重要な文書が必要になります。

回路図のネットリストは、実際のPCBを作成するために設計ソフトウェアの複数の機能で使用される中心的な情報の一つです。回路図のネットリストは、電気的接続情報を提供するとともに、設計データの機能構造を単一のデータセットで反映します。データを再利用する必要がある場合や、シミュレーションツールで電気的接続を迅速に定義する必要がある場合、ネットリストは回路図設計からこれらの他のツールへの移行を助けてくれます。また、設計レビューの一環として、製造業者にネットリストのコピーを提供する必要もあります。PCB設計ソフトウェア内のネットリストの正確な構造をもう少し詳しく見てみましょう。

スキーマティックネットリストには何が含まれていますか?

さらに進む前に、EDAソフトウェアで使用されるネットリストには、IC設計やPCB設計用の異なるタイプがあることを理解しておく必要があります。これらのネットリストは、ロジック、コンポーネント間の接続、および階層的な関係を定義することができます。ネットリストは、設計の構造と機能を要約するための強力なツールです。ネットリストにはグラフィカルな情報は含まれていません。これはスキーマティックドキュメント自体に含まれています。

それはそうと、回路図とそのネットリストは密接に関連しています。ネットリストは回路図から生成することができるし、回路図(フラットまたは階層的)はネットリストから生成することもできます。PCB回路図の情報に関して言えば、ネットリストには複数のデータエントリが含まれ、各エントリには以下の情報が含まれます:

- ネットラベル:スキーマティック内の特定のネットに付ける名前です

- 参照指定子:ネット上に接続されたコンポーネントのための指定子です

- ピン番号:ネット上の各コンポーネントはいくつかのピンを持っているため、ネット上の各コンポーネントのピン番号がネットリストに表示されます

スキーマティックのネットリストの読み方を知っていれば、回路がシミュレーションの準備時にSPICEネットリストにどのように変換されるかを見ることができます。また、サードパーティのライブラリからのネットリストに見つかるかもしれないエラーをトラブルシューティングすることもできます。

回路図をキャプチャして初期レイアウトにインポートすると、回路図のネットリストデータが使用されて、未配線のレイアウトで見られる接続線が作成されます。回路図にこれ以上の変更を加える必要がない限り、ボードを配線する際に設計データが一貫していることを確信できます。ただし、製造前にBOMとガーバーファイルが回路図とネットリストの情報と一致していることを確認する必要があります。

製造業者がネットリストをどのように使用するか

設計レビュー中に、回路図のネットリストのデータがGerber、BOM、および回路図のデータと比較されます。ネットリストとこれらのドキュメントの1つ以上の間に不一致が見られることはよくあります。これは、ほとんどの場合、設計が完了する前にネットリストとBOMをエクスポートした結果であり、設計を送信する直前の最後の変更により、BOM、ネットリスト、およびGerberを再構築して、すべてのデータが一致していることを確認する必要があります。これが繰り返しに聞こえるかもしれませんが、低品質の製造業者を使用して不良のボードのバッチを郵送で受け取るよりはましです。

製造業者は、ネットリストを使用してベアボードテストの要件を定義します。ネットリストの接続性は、ベアボードテストプロセスに使用されるテストフィクスチャにプログラムされます。ODB++データファイル形式は、ネットリストをパッケージから生成できるため、製造において好ましい形式です。それ以外の場合は、Gerberファイルと一緒にIPC-D-356ネットリストを送信することをお勧めします。これにより、ベアボード製造前に徹底的な比較が可能になります。

古いプロジェクトのネットリストを捨てないでください

デザインの再利用は新しい概念ではなく、頻繁に使用するライブラリや回路ブロックを保持することから全てに及びます。異なるEDAアプリケーションからの設計データを希望のプラットフォームにインポートすることは難しい場合があります。次の設計は古い設計のバリアントであるかもしれませんし、元の回路図/レイアウトの特定の機能ブロックを参照する必要があるかもしれません。古いプロジェクトからのネットリストを保持しておくことで、元のレイアウトや/および回路図データが破損しているかアクセスできない場合でも、新しい設計プラットフォームでそれらを再構築するのに役立ちます。

回路網リストに配置されたデータは特定の形式で高度に構造化されているため、異なる設計プラットフォームは新しい設計を構築する際に互いの回路網リストを再利用することができます。古い設計のコンポーネントに対してモデル、回路図シンボル、PCBフットプリントを持っていれば、新しいソフトウェアで元の設計を手動で再構築する必要はありません。回路網リストからネット名、参照指定子、ピン番号を読み取ることはできますが、古い回路網リストから設計を迅速に再構築できる設計ソフトウェアを使用する方がはるかに良いでしょう。

Altium Designer®の回路図設計およびシミュレーション機能により、新しい設計をエンジニアリングする際に、回路図が自動的にコンパイルされるようになりました。プロジェクトドキュメントを手動でコンパイルしたり、プロジェクト内のネットリストの不一致について心配する必要がありません。Altium Designerを使用すると、他のEDAプラットフォームからの設計データを簡単にインポートできるため、古い設計の再利用時に時間を節約できます。また、コンポーネントデータの管理や生産準備のための幅広いツールにアクセスできます。

今すぐ無料トライアルをダウンロードして、業界最高のレイアウト、シミュレーション、および生産計画ツールで作業できます。今日Altiumの担当者と話をして、詳細を学びましょう。