Was ist eine integrierte Entwicklungsumgebung für die Elektronik?

Das späte Erkennen mechanischer Randbedingungen ist eine häufige Ursache für Terminverzögerungen und Nacharbeit in Elektronikprojekten.

Betrachten wir ein typisches Szenario: Drei Monate nach Projektbeginn ist der Schaltplan fertig und das PCB-Layout weitgehend abgeschlossen. Erst dann erwähnt der Kunde, dass einige Millimeter über der Hauptplatine eine zweite Leiterplatte montiert wird – etwas, von dem er annahm, dass es aus früheren Fotos offensichtlich sei. Zu diesem Zeitpunkt sind die zuvor ausgewählten Steckverbinder und Bauteile zu hoch, was eine Neuauswahl von Teilen erzwingt, die aufgrund der Spannungs- und Stromanforderungen ohnehin bereits schwer zu beschaffen sind. Mehrere Wochen Arbeit gehen verloren, um eine Randbedingung zu berücksichtigen, die nie formell erfasst wurde.

Diese Art von Problem ist nicht ungewöhnlich. Sie ist eine vorhersehbare Folge voneinander getrennter Design-Workflows.

Wichtige Erkenntnisse

- Eine integrierte Designumgebung vereint Schaltplanerfassung, PCB-Layout, Simulation, MCAD-Zusammenarbeit und Datenmanagement, sodass Ingenieure nicht zwischen voneinander getrennten Tools wechseln müssen.

- Designregeln und Randbedingungen (wie Freiräume, Abstände und Bauteilhöhen) müssen während des Designs in Echtzeit geprüft werden, nicht erst nachdem Dateien zur Fertigung freigegeben wurden.

- Mechanische und Firmware-Randbedingungen müssen zu Beginn eines Projekts eingebracht werden. Werden sie erst nach der Bauteilauswahl erkannt, führt das zu unnötiger Nacharbeit und Verzögerungen.

Das Problem: Sechs Tools für eine einzige Platine

In vielen Hardware-Teams ist der Design-Workflow auf mehrere voneinander getrennte Tools verteilt. Padstack-Definitionen liegen möglicherweise in einer Anwendung. Schaltplansymbole und Bibliotheken werden in einem separaten Tool verwaltet und oft in unterschiedlichen lokalen oder Netzwerkordnern gespeichert. Das PCB-Layout wird an anderer Stelle erstellt. Systemintegration, Signalintegrität und EMI-Analyse werden typischerweise in zusätzlichen, spezialisierten Anwendungen durchgeführt. Projektverfolgung und Aufgabenmanagement sind häufig webbasiert und nicht immer zugänglich, wenn Ingenieure offline arbeiten.

Das Ergebnis: Ingenieure müssen mindestens fünf verschiedene Tools beherrschen und aktuell halten, nur um ein Design von der Schaltplanerfassung bis zu einer fertigungsgerechten Leiterplatte zu bringen.

In kleinen Teams erzeugt diese Fragmentierung zusätzlichen Aufwand. Der Wechsel zwischen Tools erfordert häufige Datei-Exporte und -Importe, wobei bei jedem Schritt Übersetzungsfehler auftreten können. Bibliotheken und Footprints müssen in bestimmten Verzeichnisstrukturen abgelegt werden, damit sie nutzbar bleiben; eine falsch abgelegte Datei kann verhindern, dass ein Bauteil korrekt vom Schaltplan ins Layout übertragen wird.

Viel Zeit geht für das Auffinden von Schaltplansymbolen, PCB-Footprints und den richtigen Dateiversionen verloren – Aufgaben, die eigentlich trivial sein sollten, sich im Verlauf eines Projekts aber oft auf Tage oder Wochen summieren.

Trotz der Vielzahl eingesetzter Tools basiert die abschließende Abstimmung immer noch auf E-Mails und Tabellen. Die Tools selbst bleiben weitgehend voneinander getrennt und bieten nur wenig gemeinsame Transparenz über den gesamten Designprozess hinweg.

Was eine integrierte Designumgebung tatsächlich bedeutet

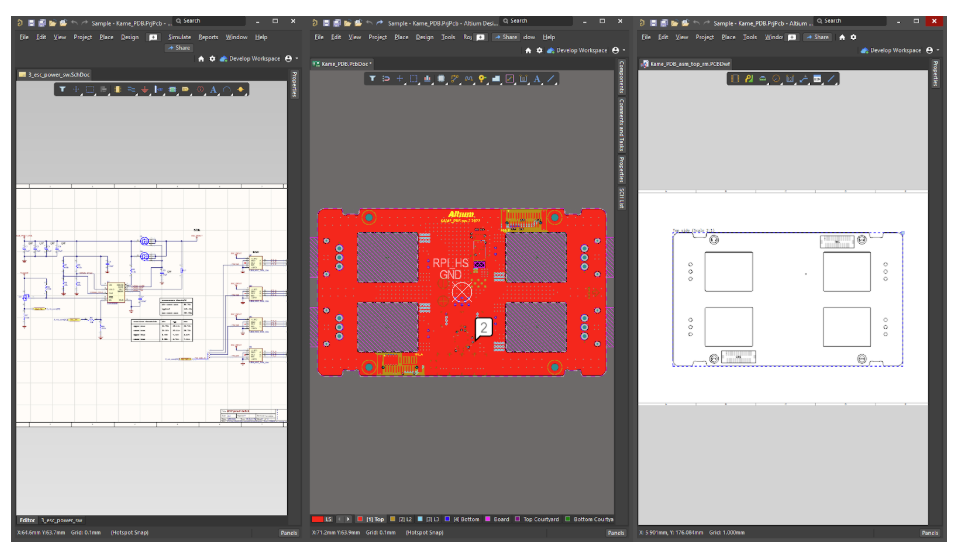

Eine integrierte Designumgebung für Elektronik ist eine einzelne Anwendung oder ein eng gekoppeltes Toolset, das den vollständigen Hardware-Design-Workflow unterstützt:

- Schaltplanerfassung für den Schaltungsentwurf

- PCB-Layout für Bauteilplatzierung und Routing

- Simulation zur Validierung vor der Fertigung

- ECAD-MCAD-Zusammenarbeit, damit Elektro- und Mechanikteams mit denselben Daten arbeiten

- Datenmanagement für Bauteilbibliotheken, Projektdateien und Designanforderungen

In einer integrierten Umgebung werden in allen Designphasen dieselben zugrunde liegenden Daten verwendet. Änderungen im Schaltplan werden direkt ins PCB-Layout übernommen. Mechanische Randbedingungen wie Platinenkonturen oder Gehäusefreiräume sind in der elektrischen Designumgebung sichtbar, sobald sie aktualisiert werden.

Dadurch entfallen manuelle Exporte, Dateiimporte und Versionskonflikte, wie sie in Toolchains auf Basis voneinander getrennter Anwendungen häufig vorkommen.

- Eine detaillierte Erklärung, wie dies in der Praxis zwischen Elektro- und Mechanikteams funktioniert, finden Sie unter ECAD-MCAD collaboration in Altium Develop.

Wie Integration den Feedback-Loop schließt

Hier ein typisches Szenario in einem Leistungselektronikprojekt: Das PCB-Layout wird in einem Tool erstellt, die Schaltplanerfassung erfolgt in einem anderen, und das Gehäuse wird vom Konstrukteur separat in PTC Creo entworfen. Keine dieser Umgebungen teilt Live-Designdaten.

In diesem Fall bot das Gehäuse nur knapp Platz für die Leiterplatte, und Kabelbaugruppen verletzten die Abstandsanforderungen. Diese Probleme waren für sich genommen keine Designfehler. Sie traten auf, weil keine einzelne Umgebung Transparenz über den vollständigen mechanischen und elektrischen Kontext bot. Die Auflösung der Konflikte erforderte mehrere Abstimmungsschleifen zwischen Elektro- und Mechanikteams und verlängerte den Zeitplan um zwei bis drei Wochen.

Wenn ECAD- und MCAD-Tools integriert sind, schließt sich dieser Feedback-Loop. Der Konstrukteur definiert Platinenkontur und Randbedingungen direkt aus dem Gehäusemodell, und diese Randbedingungen werden an das PCB-Layout weitergegeben. Der Elektroingenieur sieht sofort die verfügbare Platinenfläche, validierte Positionen der Befestigungsbohrungen und Grenzen für die Bauteilhöhe, bevor er sich auf die Bauteilauswahl oder Routing-Entscheidungen festlegt.

Diese bidirektionale Synchronisierung reduziert Iterationen, verhindert Konflikte in späten Phasen und verkürzt die gesamten Designzyklen.

- Weitere Details zur ECAD-MCAD-Zusammenarbeit finden Sie in der MCAD CoDesigner documentation.

Echtzeit-Validierung von Designregeln rettet Ihre Leiterplatten

Rückstrompfad-Vias, Freiraumverletzungen sowie Abstandsfehler im Hinblick auf Design for Fabrication oder Design for Assembly sind häufige Ursachen für PCB-Nacharbeit und Re-Spins. Diese Probleme bleiben oft unentdeckt, wenn Designregeln erst nach Abschluss des Layouts geprüft werden.

Die Echtzeit-Validierung von Designregeln kennzeichnet Verstöße genau in dem Moment, in dem sie entstehen. Wird eine Freiraumvorgabe verletzt, ist das sofort sichtbar. Entspricht eine Leiterbahnbreite nicht den Anforderungen ihrer zugewiesenen Netzklasse, wird der Fehler direkt im Layout hervorgehoben.

Dieser Ansatz unterscheidet sich von stapelbasierten Design Rule Checks, die Probleme erst erkennen, nachdem die Designarbeit abgeschlossen ist. Batch-Prüfungen decken Probleme auf, die möglicherweise Stunden oder Tage zuvor eingeführt wurden. Die Echtzeitprüfung verhindert, dass sich diese Fehler fortpflanzen, indem sie Randbedingungen bereits während des Layouts durchsetzt.

Die tatsächlichen Kosten von „funktioniert schon“

„Unsere aktuelle Toolchain funktioniert doch“ bedeutet oft, dass der Prozess fragil ist.

In einem Projekt wurde Schaltplansoftware für das Design von Kabeln und Kabelbäumen verwendet. Technisch war das zwar möglich, aber das Tool war nicht für diesen Zweck ausgelegt. Dadurch wurden elektrische Änderungen nicht automatisch in die Zeichnungen übernommen, und jedes Label sowie jedes Textfeld musste manuell aktualisiert werden.

Das führte zu vorhersehbaren Fehlern. Mehrere Kabelbaugruppen wurden mit falscher Verdrahtung gefertigt, weil die Dokumentation nicht mit dem tatsächlichen Design synchron war. Ingenieure verbrachten viel Zeit damit, Fehler zu prüfen, erneut zu prüfen und zu korrigieren, die eigentlich vom Tool selbst hätten verhindert werden müssen. Die individuelle Produktivität sank aufgrund des ständigen Aufwands für manuelle Aktualisierungen und Verifikation schätzungsweise auf 40–50 %.

Das System funktionierte – aber nur in dem Sinne, dass es nicht sofort ausfiel. Die tatsächlichen Kosten von „funktioniert schon“ wurden in Form von Nacharbeit, Verzögerungen und verringerter Engineering-Kapazität bezahlt.

Wenn Firmware und Mechanik zu spät ins Spiel kommen

In einem aktuellen Projekt war das Design der Hauptplatine abgeschlossen, die Stückliste finalisiert, und das Design war bereit zur Freigabe für die Fertigung.

Zu diesem Zeitpunkt tauchte eine neue Randbedingung auf: Eine sekundäre LED-Platine sollte auf der Hauptplatine montiert werden, bei nur 10 mm vertikalem Freiraum.

Diese späte Anforderung erzwang eine Neugestaltung des betroffenen Bereichs. Vorhandene Steckverbinder überschritten die zulässige Höhe. Bauteile mit ausreichender Stromtragfähigkeit waren nicht in flachen Gehäusen verfügbar. Alternative Teile, die die Höhenanforderung erfüllten, hatten unpraktische Mindestbestellmengen oder waren bereits abgekündigt.

Etwa vier Wochen wurden für die Bewertung von Alternativen aufgewendet, was zu zusätzlichen Beratungskosten von 2.000 US-Dollar führte (rund 10 % des Gesamtbudgets des Projekts) – nur um festzustellen, dass der ursprüngliche Designansatz nicht tragfähig war.

Zusätzlich verzögerten Stillstände zum chinesischen Neujahr die Fertigung. Leiterplatten, die eigentlich im Oktober oder November hätten ausgeliefert werden sollen, wurden erst im März geliefert.

Die eigentliche Ursache war kein technisches Versagen, sondern ein Prozessversagen. Mechanische Randbedingungen wurden zu Projektbeginn nicht kommuniziert, und es gab keine gemeinsame Umgebung, in der Elektro-, Mechanik- und Firmware-Teams Anforderungen auf Systemebene früh im Designzyklus einsehen und validieren konnten.

Warum alles zusammenarbeiten muss

Softwaresysteme können oft einen teilweisen Ausfall tolerieren. Wenn eine Funktion ausfällt, können andere Teile der Anwendung weiterlaufen, sodass Probleme schrittweise behoben werden können.

Hardware-Systeme verhalten sich nicht so.

Wenn die Leistungsarchitektur falsch ist, wenn Pegelwandler falsch eingesetzt werden oder wenn grundlegende Schnittstellen versagen, funktionieren große Teile der Platine nicht – oder das System startet überhaupt nicht. Hardware erfordert einen hohen Grad an Korrektheit über alle Subsysteme hinweg, bevor überhaupt sinnvolle Tests beginnen können.

Weil Hardware von Natur aus integriert ist, muss auch der Entwicklungsprozess integriert sein. Anforderungen dürfen nicht in E-Mail-Threads verborgen bleiben. Designregeln dürfen nicht erst am Ende des Layoutprozesses geprüft werden. Mechanische Randbedingungen dürfen nicht erst Monate nach Entwicklungsbeginn entdeckt werden, ohne Nacharbeit und Verzögerungen zu verursachen.

Design-Tools sollten diese Realität widerspiegeln. Elektrische, mechanische und Bauteildaten müssen über den gesamten Designzyklus hinweg verbunden, sichtbar und zugänglich sein – nicht als voneinander getrennte Dateien und Übergaben verwaltet werden.

Für Teams, die die fragmentierte Toolchain hinter sich lassen möchten, ist Altium Develop ein guter Ausgangspunkt.

Ganz gleich, ob Sie zuverlässige Leistungselektronik oder fortschrittliche digitale Systeme entwickeln möchten: Altium Develop vereint jede Disziplin zu einer gemeinsamen kollaborativen Kraft. Frei von Silos. Frei von Grenzen. Hier arbeiten Ingenieure, Designer und Innovatoren als Einheit zusammen, um ohne Einschränkungen gemeinsam Neues zu schaffen. Erleben Sie Altium Develop noch heute!

Häufig gestellte Fragen

Was ist eine integrierte Designumgebung für Elektronik?

Eine integrierte Designumgebung vereint Schaltplanerfassung, PCB-Layout, Simulation, ECAD-MCAD-Zusammenarbeit und Datenmanagement in einem einzigen, verbundenen Workflow. Statt Dateien zwischen separaten Tools zu verschieben, arbeiten Ingenieure mit gemeinsamen Daten, sodass Änderungen automatisch über die Designphasen hinweg übernommen werden.

Wie reduziert eine integrierte Umgebung Nacharbeit und Terminverzögerungen?

Durch die Echtzeitvalidierung elektrischer, mechanischer und fertigungstechnischer Randbedingungen werden Probleme wie Freiraumverletzungen, Grenzen der Bauteilhöhe oder Routing-Konflikte in dem Moment erkannt, in dem sie auftreten – nicht erst Wochen später. Das verhindert Neugestaltungen in späten Phasen, die typischerweise zu Terminüberschreitungen und Mehrkosten führen.

Warum ist die ECAD-MCAD-Integration zu Beginn eines Projekts so wichtig?

Mechanische Randbedingungen wie Gehäusegeometrie, Board-Stacking und Steckverbinder-Ausrichtung wirken sich direkt auf die Bauteilauswahl und Layoutentscheidungen aus. Wenn diese Randbedingungen von Anfang an sichtbar sind, vermeiden Teams die Auswahl von Teilen oder Architekturen, die sich später als nicht umsetzbar erweisen.

Worin unterscheidet sich die Echtzeit-Designregelprüfung von herkömmlichen Batch-Prüfungen?

Die Echtzeitprüfung kennzeichnet Fehler sofort, sobald gegen eine Regel verstoßen wird, sodass Ingenieure Probleme beheben können, bevor sie sich fortpflanzen. Batch-Prüfungen identifizieren Probleme erst nach Abschluss des Layouts, was häufig erhebliches Zurückverfolgen und Nacharbeit erfordert.