Length Matching en Buses de Alta Velocidad

Con el continuo aumento de la velocidad en los sistemas de datos de alta velocidad, vienen asociados un par de retos a la hora de realizar el layout del PCB. Los buses de alta velocidad como DDR, VME o PCIe por mencionar algunos, pueden llegar a alcanzar velocidades de transmisión de datos que requieren una sincronización enorme con muy poco margen de tolerancia. Es por esto que en tales casos no hay demasiado margen de maniobra a la hora de realizar el layout del PCB. Únete a nosotros en este webinar y aprende por qué es imperativo hacer coincidir la longitud de las pistas en los sistemas de datos de alta velocidad y en señales diferenciales. En este webinar verás cómo definir correctamente las reglas de Length Matching y Time Delay, y cómo enrutar señales de alta velocidad de manera efectiva con Altium Designer®.

Aquí enumeramos algunos de los puntos sobre los que hablaremos:

-

¿Por qué es importante hacer coincidir la longitud de las pistas cuando se trabaja con señales de alta velocidad?

-

Length matching y time delay tuning en buses de alta velocidad y señales diferenciales.

-

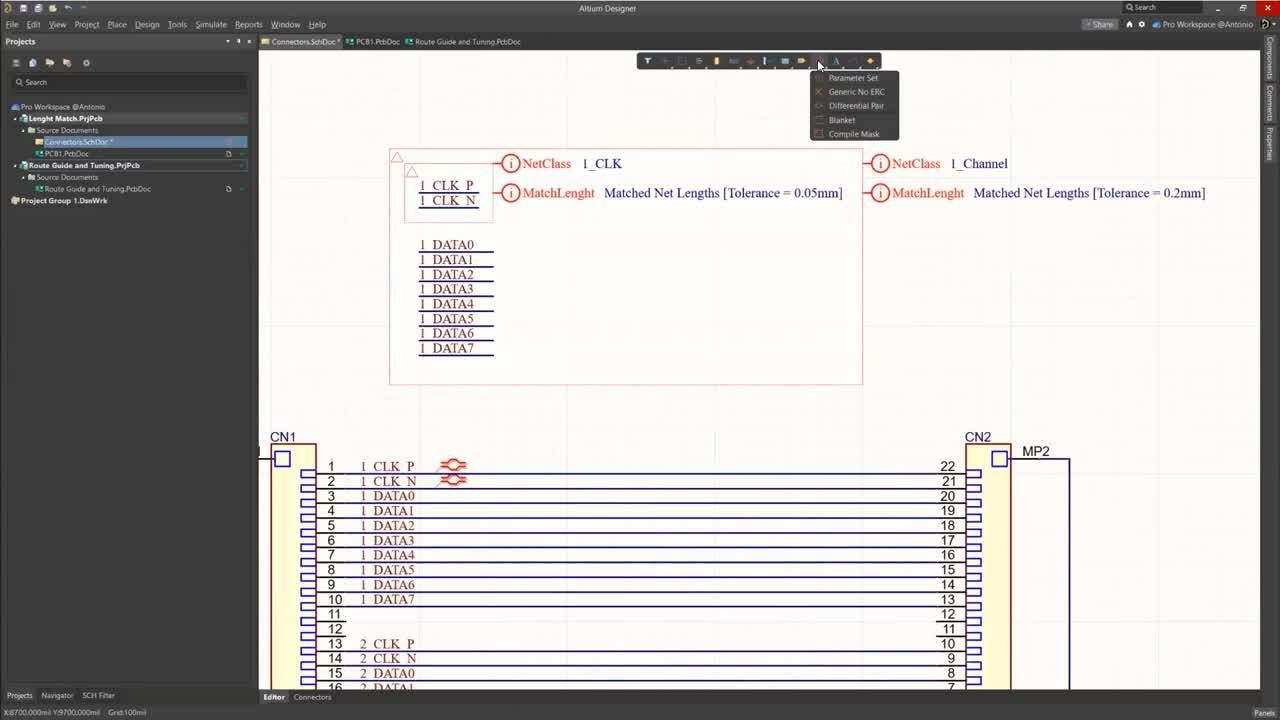

Cómo configurar las reglas de alta velocidad para PCB desde el esquemático o el PCB.

-

Cómo tunear pistas de terminación única o diferenciales.