FPGA : Création de pipelines d'intégration continue pour les systèmes embarqués ou les PCBs

Dans cet article, Ari Mahpour vous guide dans la création de pipelines d'Intégration Continue destinés aux FPGA

Les Field Programmable Gate Arrays, ou FPGAs, sont devenus omniprésents dans les systèmes numériques haute vitesse et en temps réel. Ils peuvent être utilisés pour des applications critiques en termes de temps, le traitement numérique du signal, ou même pour le minage de crypto-monnaie. Leur efficacité en termes de vitesse et de consommation d’énergie les rend parfaits pour des applications réutilisables à haute vitesse. La vitesse à laquelle les FPGAs fonctionnent continue d’augmenter à un rythme effréné, mais leur adoption dans les pipelines d'intégration continue (CI) semble ne pas suivre d’aussi près. Dans cet article, nous examinerons le concept des pipelines CI, leur application aux FPGAs, et nous verrons des exemples sur la façon de les mettre en place.

Intégration Continue et FPGAs

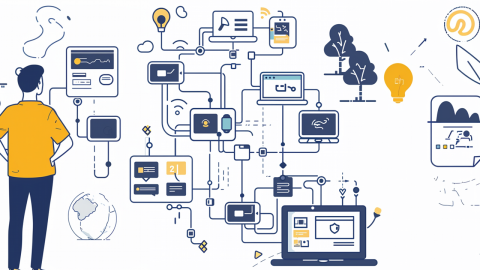

Si vous ne l'avez pas encore remarqué, je vis pratiquement dans l'intégration continue. Que ce soit pour l’IC pour la conception de PCB ou pour l’IC pour les systèmes embarqués, je cherche toujours des moyens d'améliorer et d'automatiser en continu les builds pour tout type de système. Certains retours récents m'ont dit qu'il n'y a pas eu beaucoup de progrès avec les FPGAs et les systèmes CI. Le principe de base de l'IC et des FPGAs suit la même logique que tous les autres systèmes CI : créer un environnement de build répétable qui peut faire tout le travail pour nous. Dans un système CI basé sur FPGA, on verrait généralement les trois étapes suivantes :

Figure 1 : Étapes d'un pipeline CI pour FPGA

Chaque étape est importante en elle-même et nécessite sa propre configuration. Voyons chaque étape pour comprendre ce qu'elles représentent et comment les mettre en œuvre.

Simulation

La simulation est une partie intégrante de la conception FPGA. La construction d'une image FPGA à charger sur une cible peut prendre beaucoup de temps. Plutôt que d'écrire du code, de le compiler et de le tester sur du matériel, la simulation nous permet de tester rapidement notre code, ou notre niveau de transfert de registres (RTL), dans un environnement qui simule le comportement d'un FPGA. Cela se fait généralement au niveau de l'utilisateur, mais il devient de plus en plus courant d'intégrer la simulation FPGA dans des pipelines CI. Cela signifie qu'une personne pousserait son code vers son dépôt et qu'un pipeline se lancerait pour exécuter la simulation (auto-vérification) quelque part dans le cloud. Pour vraiment faire cela « quelque part dans le cloud », il est nécessaire de créer un environnement qui peut être encapsulé, ou containerisé, dans un environnement auto-suffisant. Nous faisons cela en utilisant quelque chose appelé conteneurs Docker. Ils agissent presque comme des machines virtuelles qui peuvent être exécutées n'importe où. Ce conteneur Docker particulier, par exemple, crée un environnement containerisé qui permet à un utilisateur d'exécuter Icarus Verilog dans n'importe quel système Linux. Nous prenons ensuite ce conteneur et l'utilisons pour créer notre pipeline de simulation FPGA. Dans cet exemple, vous pouvez voir un simple pipeline « Hello World » s'exécuter dans le cloud en utilisant Icarus Verilog. Notez que cela peut être fait avec n'importe quel outil de simulation FPGA.

Figure 2 : Exécution d'un pipeline de simulation FPGA utilisant GItlab CI

Construction

Une deuxième étape, également très importante, dans le pipeline FPGA est l’étape de construction. Nous voulons pouvoir synthétiser, placer et router, puis générer un bitstream pour notre conception FPGA. Cela est généralement fait par les utilisateurs dans l’outil fourni par le fournisseur (par exemple, Xilinx, Intel, Microchip, etc.). Au lieu d’effectuer cette construction localement, nous aimerions qu’elle se fasse ailleurs. Cela peut cependant être un peu compliqué car les outils FPGA sont souvent très volumineux. Une approche que de nombreux utilisateurs adoptent est d’avoir une « machine de construction » dédiée qui exécute tous les pipelines de construction. Cette approche n’est pas mauvaise, mais elle ne peut pas évoluer et peut devenir un point unique de défaillance. D'autres ont tenté de containeriser des outils FPGA, mais ces images peuvent dépasser 100 Go, ce qui les rend essentiellement inutilisables pour les applications cloud. Un compromis que j'ai trouvé efficace est la méthode d'installation en réseau. À titre d'exemple, j'ai créé un conteneur qui exécute Vivado 2019.1, mais l'outil lui-même n'est pas installé sur l'image (ce qui réduit la taille de l'image à moins de 300 Mo). Ce que j’ai fait, c’est installer Vivado sur un lecteur réseau (dans ce cas EFS dans AWS) puis l’avoir monté dans mon conteneur Docker. Étant donné que mon pipeline s'exécute dans AWS, la latence entre l'EFS et l'instance EC2 (nœud Kubernetes) est négligeable.

Dans cet exemple, j'utilise un dispositif Arty A7 de Digilent pour créer un filtre numérique. J’utilise un script de construction automatisé pour générer le fichier bitstream pour mon appareil à chaque push vers mon référentiel. Comme vous pouvez le voir dans la sortie, j'appelle Vivado avec succès, même s'il n'existe pas dans le conteneur Docker (c'est-à-dire qu'il est monté en tant que lecteur externe).

Figure 3 : Exécution du pipeline de construction FPGA en utilisant Gitlab CI

Test

La phase de test dépendra vraiment de chaque individu et projet. L’objectif des tests dans un pipeline d’intégration continue est d’automatiser autant que possible. Tout comme j’ai automatisé mon exemple DSP pour Arduino avec mon Analog Discovery 2, je pourrais également faire de même ici. Couvrir une solution de test automatisée pour les FPGA serait un peu hors sujet pour cet article. Le principe clé ici est de s’assurer qu’il est répétable et qu’il s’exécute dans un environnement encapsulé ou containerisé. Il est important de se rappeler que les tests constituent une partie essentielle du pipeline CI et doivent être implémentés à un niveau que l’utilisateur peut gérer.

Conclusion

Dans cet article, nous avons abordé le concept des pipelines CI pour les FPGA. Nous avons passé en revue les trois étapes critiques qui composent les pipelines FPGA : la simulation, la construction et le test. Nous avons examiné des exemples de pipelines de simulation et de construction et discuté de l’importance des tests. Après avoir consulté cet article et les exemples, l’utilisateur devrait être en mesure de comprendre la composition de base nécessaire pour créer un pipeline CI basé sur un FPGA.

Lorsque vous êtes prêt à construire votre carte FPGA personnalisée pour prendre en charge votre système embarqué, utilisez l’ensemble complet des fonctionnalités de conception et de disposition de PCB dans Altium Designer®. Une fois votre PCB terminé et prêt à être partagé avec des collaborateurs ou votre fabricant, vous pouvez partager vos conceptions complètes via la plateforme Altium 365™. Tout ce dont vous avez besoin pour concevoir et produire des électroniques avancées se trouve dans un seul logiciel.

Nous n’avons fait qu'effleurer ce qui est possible avec Altium Designer sur Altium 365. Commencez votre essai gratuit d’Altium Designer + Altium 365 dès aujourd’hui.