Progetto Pi.MX8 - Layout della scheda Parte 3

Capitoli

Board Layout Part 3

| Created: June 24, 2024PCB Assembly

| Coming soonBenvenuti a una nuova puntata del progetto del modulo computer open-source Pi.MX8! In questa serie, ci immergiamo nella progettazione e nei test di un modulo su sistema basato su un processore i.MX8M plus di NXP.

Nell'aggiornamento precedente, abbiamo completato le preparazioni del layout. Questo ha incluso la creazione dei profili di impedenza, l'aggiunta delle regole di progettazione secondo le specifiche del produttore della scheda e la definizione delle aree dove dovrebbero applicarsi regole di progettazione speciali. Abbiamo anche terminato il routing dell'interfaccia LPDDR4 ma senza ancora procedere alla regolazione della lunghezza (per ora).

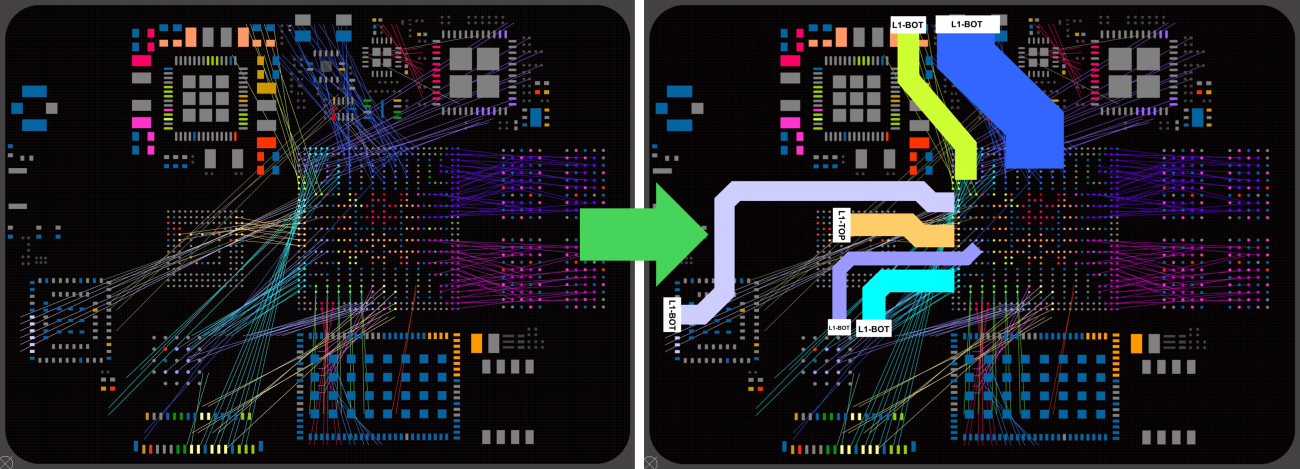

Prima di iniziare con la regolazione della lunghezza dell'interfaccia DRAM, daremo un'occhiata al routing delle rimanenti interfacce sul modulo Pi.MX8. Ci sono parecchi bus ad alta e bassa velocità sulla scheda, alcuni dei quali sono bus paralleli ampi che occupano molto spazio di routing. Per allocare abbastanza spazio a ciascuna interfaccia, creeremo prima una bozza di piano per ogni strato di routing sul modulo.

Progettazione del routing

Il piano di instradamento ci aiuterà a determinare come distribuire tutte le interfacce ad alta e bassa velocità attraverso i vari strati di segnale disponibili. Impostando una guida approssimativa in anticipo, possiamo assicurarci di avere abbastanza spazio di instradamento disponibile sullo strato su cui stiamo lavorando. Questo ci aiuta anche a minimizzare le transizioni tra gli strati e a ridurre la quantità di lavoro di rifinitura da fare durante il processo di instradamento.

Ci sono diversi modi per impostare la pianificazione del layout, principalmente dipendenti dagli strumenti disponibili. Abbiamo bisogno solo di uno strumento di disegno di base che ci permetta di schizzare su un'immagine esistente. In questo esempio, utilizzeremo Inkscape.

In Inkscape, possiamo aggiungere un'immagine di sfondo che mostra il posizionamento dei componenti e le interfacce non instradate sotto forma di airwires colorati. Nota che le reti di alimentazione sono nascoste in questa schermata poiché ci concentreremo solo sulle reti che saranno instradate sugli strati di segnale. Nello schema, abbiamo posizionato una direttiva di classe di rete su ogni rete di alimentazione, rendendo facile identificare quali reti sono instradate sugli strati di piano semplicemente abilitando o nascondendo la classe di rete associata nell'editor di layout.

Per l'effettivo routing, aggiungiamo semplicemente delle linee in Inkscape per rappresentare le interfacce che vogliamo instradare sullo strato corrispondente. Possiamo regolare la larghezza di queste linee per rappresentare quanti segnali verranno instradati nell'interfaccia. Il colore della linea può essere scelto dall'immagine di sfondo per facilitare l'identificazione dell'interfaccia rappresentata.

Dato che anche le transizioni tra gli strati richiedono spazio allocato su tutti gli strati, possiamo aggiungere un blocco alla fine di ogni linea per dettagliare la transizione di strato.

La pianificazione del layout in Inkscape con uno screenshot di Altium Designer come immagine di sfondo

Una volta ripetuto il processo sopra per ogni strato di routing, possiamo procedere e iniziare con il vero e proprio processo di routing.

Routing dello strato superiore

Con una strategia di routing definita, iniziamo col routing delle interfacce sullo strato superiore. Dato che abbiamo già completato il routing di fanout per i componenti sullo strato superiore, possiamo utilizzare tutto lo spazio rimanente per il routing dei segnali. Lo spazio lasciato non è molto, ma quello che abbiamo può ancora essere utilizzato per semplificare il routing sui livelli interni dei segnali posizionando strategicamente le VIA in regioni che non interferiranno con il routing sui livelli interni in seguito. Questo è un altro vantaggio della pianificazione anticipata di un layout, altrimenti queste regioni non sarebbero definite in questa fase.

Routing dello strato superiore del modulo PiMX8

Quando posizioniamo le tracce sullo strato superiore dovremmo anche considerare che abbiamo bisogno di spazio per aggiungere elementi come i fiduciali o le etichette sullo strato superiore. I codici a matrice di dati incisi al laser possono richiedere anche un'area di rame solido o un'area senza tracce per fornire un contrasto omogeneo, il che significa che queste aree non possono essere utilizzate per il routing.

Routing del Livello Interno dei Segnali

La maggior parte delle connessioni sarà posizionata sui due strati interni di segnale che abbiamo definito nel gestore dello stack di strati. Iniziamo col tracciare tutte le interfacce sincrone ad alta velocità. Nel nostro caso, queste potrebbero essere le interfacce MIPI-CSI, MIPI-DSI e LVDS. Queste interfacce utilizzano tutte la segnalazione differenziale a bassa tensione e trasportano una linea di clock dedicata e almeno due linee dati. Richiedono molto spazio di routing perché la lunghezza di ogni linea dati deve essere abbinata a quella della linea di clock entro un certo margine temporale. Abbinare la lunghezza di più coppie differenziali può richiedere molto spazio, poiché è molto probabile che una o più coppie all'interno dell'interfaccia introducano un ritardo significativo che deve essere considerato. Tracciando per prime queste interfacce, possiamo assicurarci che ci sarà abbastanza spazio disponibile per la regolazione della lunghezza in seguito.

Posizionare le VIA di ritorno vicino alle transizioni di strato di queste coppie differenziali ad alta velocità è anche importante per garantire l'integrità del segnale. Le VIA di ritorno possono occupare spazio su più strati, quindi queste VIA dovrebbero essere posizionate non appena viene effettuata una transizione di segnale.

Successivamente, possiamo instradare le altre interfacce ad alta velocità come PCIe, USB, HDMI ed Ethernet. Queste interfacce hanno requisiti meno stringenti per il matching di lunghezza tra coppie, quindi non dobbiamo dedicare tanto spazio al matching di lunghezza. Tuttavia, una solida gestione del percorso di ritorno e approcci di base alla progettazione ad alta velocità su questi segnali sono ancora molto importanti, anche se li posizioniamo al secondo posto nella lista delle priorità di routing.

Ultimo ma non meno importante, possiamo instradare le rimanenti interfacce a bassa velocità come SDIO, GPIO, RGMII e altri bus vari come UART o I2C e SPI. Queste interfacce operano ancora a tassi di transizione elevati, il che significa che dobbiamo comunque trattarli come segnali ad alta velocità.

Instradamento strato di segnale interno 1

Instradamento strato di segnale interno 2

Instradamento strato inferiore

Nel caso della scheda PiMX8, possiamo trattare lo strato inferiore come uno strato di routing interno in termini di spazio disponibile. La maggior parte dei componenti attivi sono collocati sullo strato superiore del modulo, lasciando solo alcuni regolatori di tensione e componenti passivi come condensatori di disaccoppiamento e resistori di configurazione sullo strato inferiore.

La priorità di routing sullo strato inferiore è la stessa degli strati interni, quindi inizieremo con le interfacce MIPI-CSI, MIPI-DSI e LVDS. Sul modulo PiMX8, un multiplexer ad alta velocità può selezionare tra le porte DSI e LVDS. Questo componente è posizionato sullo strato inferiore vicino al connettore da scheda a scheda. A causa del pinout del multiplexer, c'è un ritardo significativo su una delle linee di segnale collegate al mux. Dovremo esaminare questo più attentamente durante il processo di abbinamento delle lunghezze, ma dobbiamo riservare dello spazio sullo strato inferiore per permettere un ritardo maggiore.

Pinout del multiplexer con una linea lunga nell'interfaccia

Routing dello strato inferiore modulo PiMX8

Ci sono alcuni scenari sul modulo PiMX8 che richiedono un'attenzione particolare durante la regolazione dei ritardi. Faremo ampio uso di X-signals per superare alcune di queste sfide. Cosa sono esattamente queste sfide, e come possiamo implementare X-signals per fornire una regolazione precisa dei ritardi su un componente condiviso da più interfacce, sarà parte del prossimo aggiornamento. Restate sintonizzati!