Pi.MX8 Project - Board Layout Part 2

Chapters

Board Layout Part 2

| Created: March 21, 2024PCB Assembly

| Coming soonIn the previous update, we looked at defining a suitable layerstack for the module as well as adding the fanout routing to all the components placed on the board. Based on all these preparations, we are now almost ready to route the first traces. Before we start connecting any components on the board though we have to define the impedance profiles and set up the matching design rules for the correct trace width.

Setting up impedance profiles

Setting up the impedance profiles is straightforward in the layerstack manager. We have to define both single ended and differential impedance profiles. The information on which impedance values are needed can be taken from the interface standards and the hardware design guides for the NXP i.MX8 processor. The following impedance values both single ended and differential are used in the design:

On the previously defined layerstack we have four signal layers available that we can use for impedance-controlled routing which are the top layer, L2, L7 and the bottom layer. The top and bottom layer each have only one reference ground plane while L2 and L7 are embedded between two reference planes. After we input the impedance values and the reference layers the trace geometry gets calculated automatically:

Layerstack manager impedance profile differential 100 Ohm

While defining the trace geometry, especially the trace width and gap for differential pairs it is important to keep the needed routing space in mind. If possible we'd like to keep the overall width of the differential pair small in order to limit the needed routing space. Depending on the density of the board, this should also be taken into account when defining the layerstack.

Setting up the design-rules

There is only one step left before we can route the first traces, and that is to tell Altium Designer what trace widths (and gaps for the differential pairs) are required depending on the interface and routing layer. The impedance values are assigned to the appropriate interfaces in the schematic. Here we can work with directives to assign nets to net classes or differential pair classes.

Multiple net classes assigned to a design blanket

In the design rule editor we can now target these nets or differential pair classes and assign the corresponding trace geometries. Instead of manually entering the trace geometry we can choose the matching impedance profile that we´ve defined in the layerstack manager:

Impedance profile used in the design rule dialog – high priority rule overrides impedance profile

Note that we have another design rule that takes the highest rule priority in our setup. This design rule only applies to certain design rooms that we've created in the previous update. These design rooms are only placed directly underneath the fine pitch components and allow us to locally use a trace width and spacing of down to 85 um in the breakout region. The design rules for these rooms have the highest priority as we need to override the defined impedance profiles. As we may not be able to follow the required trace geometry within these rooms, we need to keep them as small as possible and use trace geometries that deviate from the impedance profiles only where absolutely necessary. If we keep these sections very small, the overall impact on the channel's signal integrity will be acceptable. However, we'll need to verify this in our post-layout simulations.

Design rooms in red shown underneath fine-pitch BGAs

LPDDR4 routing

Now that all the design rules have been defined, we can start routing the first interface. On this board we will start with the DRAM interface.

You´ll notice that we have not yet defined the overall routing strategy for this board. We could have done this prior to placing any routes and depending on personal preference, there is nothing wrong with that. On this board I decided to route the DRAM interface first to see how much space and how many routing layers we need to allocate to the DRAM interface. If we can route the LPDDR4 IC on two or three signal layers, then we can allocate one or two routing layers to other interfaces in the vicinity. Since the DRAM interface takes up quite a bit of space, especially on a small board like this, having another empty signal layer available would be very desirable.

LPDDR4 decoupling capacitors

Let's take a quick look at routing the decoupling capacitors on the LPDDR4 IC. Connecting the decoupling capacitors was part of the breakout routing in the previous article. Let's review that first to see if we need to add any additional VIAs or traces on the top or bottom layer. The fact that we are using filled and capped VIAs really plays into our hands when it comes to routing the decoupling capacitors.

Each power pin on the DRAM IC has its own through VIA that can connect to all 10 layers of the board. We need to use VIAs on these pins as we are dealing with return currents on all ground planes in the stackup. Since the decoupling capacitors are placed on the bottom side of the board we also need to have the VDD and VDDQ power pads available on the bottom side of the board. The DRAM IC has a pin pitch of 0.65mm in the Y-Axis. This pin pitch allows us to place the decoupling capacitors directly between the GND and VDD/VDDQ pads. This arrangement allows for the lowest loop inductance possible. We can now evenly distribute the decoupling capacitors among the power pins.

The optional clock termination resistors are also placed directly underneath the clock pins each directly connected to the pins through VIAs.

Decoupling capacitors placed on bottom side of the LPDDR4 IC

LPDDR4 signal routing

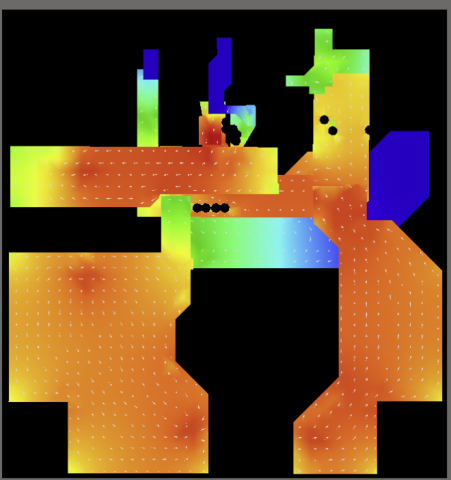

Since no additional trace segments are needed for the decoupling capacitors we can utilize the space on the bottom layer for signal routing. We will stick close to the reference design of the i.MX 8M plus and place all the DQS differential pairs on the bottom side of the board. Additionally we can also place the DRAM reset and clock enable signals on the bottom side:

DRAM routing bottom side

Coloring the command/address/control signal differently from the DQ groups helps us to identify a good routing strategy. The cyan command/address/control signals are all located behind the first two rows of signal pins on the SoC, with the exception of the two clock signals. If we want to route these signals on the inner layers we need to make sure that no VIAs from the two outer rows of signal pins are in the way. We can connect Byte 0 from channels A and B as well as the clock signals that are all available on the two outer rows directly on the top layer without needing any layer change:

DRAM top side routing

The Byte 1 from channels A and B are both located towards the corner of the BGA. This is perfect as it allows us to move those signals onto L2 and connect them to the DRAM IC while still leaving enough space in between those two routing groups to connect the command/address/control signals:

DRAM L2 routing

Strictly speaking, we are not changing the reference layer, but we are introducing a second one by switching to L2. As soon as we place a trace with a time-varying voltage over a ground plane, a current will flow regardless of whether there is a second reference plane present. To provide a return path for those currents as well we are using return path VIAs close to the layer transitions on the top layer. The signals that are switching layers behind the two outer pin rows underneath the BGA already have return path VIAs nearby that are formed by the two rows of ground pins and ground VIAs of the SoC:

Return path VIAs for the DRAM interface

Here is one more detail to keep in mind in relation to the return paths. We are using a staggered micro VIA layerstack. Therefore the two sequential micro VIAs need to be placed with a certain minimum distance to each other. A short trace segment is needed to establish a connection between the two sequential VIAs. This trace segment is placed on the ground plane underneath the top and bottom layer. We have to be careful not to create any cuts or voids on the ground plane that would disrupt the return path of the signal lines:

Return path management - voids and splits on the left side, improved routing on the right side

By arranging the micro VIAs and trace segments in line with the BGA grid of the DRAM device we can make sure that there is always a solid ground connection underneath the signal lines:

The traces on the top layer and on L2 are spaced at an even distance of at least 0.275mm to each other. This distance is necessary to ensure that we do not create excessive crosstalk between these signals. We´ll have to verify that in a post-layout simulation as well.

The only thing left to do now to finish the DRAM interface routing is delay tuning. We won't be doing this now though. Instead the delay tuning will be done for all interfaces once the routing is finished. For very high-density designs or interfaces that require a lot of delay compensation, it is best to do the length tuning earlier rather than later. The timing requirements on LPDDR4 are not too strict though so I'm confident we won't be running into any problems if we take care of that later.

For now the DRAM routing is completed and we can move to the layout planning phase and route all the other interfaces. This and more will be part of the next update on the open-source compute module project!