Cosa sono i Chiplet e come vengono utilizzati nel packaging?

I chiplet sono piccoli die di circuiti integrati (IC) con funzionalità specializzate. Sono progettati per essere combinati al fine di creare un circuito integrato più grande, seguendo la tendenza dell'industria dei semiconduttori verso l'integrazione eterogenea. La possibilità di selezionare da una gamma di chip piccoli e altamente specializzati, e poi mescolarli e abbinarli per produrre una funzionalità complessiva desiderata, rappresenta un grande passo avanti rispetto al tradizionale approccio system-on-chip (SoC) al packaging dei semiconduttori. I principali fornitori hanno prodotto processori che combinano un numero selezionato di chiplet, piuttosto che seguire la tradizionale strada della fabbricazione di semiconduttori monolitici, dove il dispositivo è fabbricato su un unico pezzo di silicio.

Sebbene l'idea dei chiplet esista da decenni, il packaging basato su chiplet sta guidando nuovi tipi di componenti, prodotti e sistemi per applicazioni specializzate. Questi componenti sono personalizzati per applicazioni specifiche, e sempre più aziende stanno entrando nel gioco della progettazione di chip con un focus sui chiplet come loro processore principale. Basandosi sul numero di articoli di ricerca, domande di brevetto e articoli tecnici che si trovano online, è chiaro che i componenti basati su chiplet sono qui per restare.

Se sei un progettista di sistemi e stai valutando le opzioni dei processori, potresti non renderti conto che i chiplet costituiscono la base per il tuo sistema. Tuttavia, i chiplet sono la colonna vertebrale che consente la diversa funzionalità trovata nei chip moderni, e il concetto di packaging continua a guidare l'integrazione di nuove caratteristiche nei progetti dei chip. Esempi includono l'integrazione di blocchi FPGA e blocchi acceleratori AI nello stesso pacchetto di memorie, una CPU e persino componenti RF.

Perché i Chiplet?

Costo e prestazioni sono le due questioni più pressanti nella progettazione e nella fabbricazione dei chip. Gli ultimi anni hanno visto rallentare lo scaling di Dennard e la Legge di Moore, risultando in intervalli di tempo più lunghi tra i nodi della tecnologia di processo. Inoltre, l'integrazione dei transistor su un chip monolitico sta diventando sempre più sfidante poiché ci sono poche opzioni disponibili per il ridimensionamento dei dispositivi. Queste sfide hanno diminuito il ROI per i semiconduttori monolitici a causa dei processi di fabbricazione più costosi.

L'unico modo per aumentare il numero di unità funzionali integrate con la stessa dimensione del transistor è espandere l'area del chip, sia nel piano del dispositivo che verticalmente. Il problema dell'aumento dell'area del chip è che i chip più grandi sono più suscettibili a difetti di fabbricazione, il che limita la resa dei wafer e aumenta il prezzo dei prodotti consegnati ai clienti. Di conseguenza, i chip monolitici stanno diventando sempre più incapaci di fornire le prestazioni desiderate alla luce delle crescenti richieste di calcolo.

Quindi, per supportare applicazioni ad alta computazione come AI/ML su dispositivo, reti ultra-veloci, fusione di sensori e dispositivi mobili di nuova generazione, abbiamo assistito all'emergere di sistemi basati su chiplet per lo sviluppo economicamente efficiente di elettronica ad alte prestazioni. Questo ha spaziato da SoC avanzati a processori per desktop/server e GPU.

Superare il "Muro dell'Area"

Il problema del "muro dell'area" è il risultato di una discrepanza tra la necessità dei sistemi di computing ad alte prestazioni di chip di grande area e la bassa resa della produzione di semiconduttori. Il muro dell'area si riferisce a questa sfida nella produzione di semiconduttori monolitici, dove chip più grandi sono utilizzati per aumentare la densità delle funzionalità, ma anche il conteggio dei difetti aumenta. Man mano che le capacità di elaborazione della produzione passano a nodi più avanzati, la resa del processo diminuisce e quindi il costo per il cliente finale aumenta. Pertanto, c'è sempre la motivazione a ridurre i rischi di produzione per questi prodotti eliminando le possibilità di difetti.

Una soluzione al muro dell'area ridurrebbe il costo complessivo di un prodotto finale riducendo gli sprechi durante la produzione. I chiplet diversificano essenzialmente il profilo di rischio per un prodotto distribuendolo su più die semiconduttori. Il risultato finale è la riduzione dei costi e la capacità di diversificare notevolmente la funzionalità in misura molto maggiore rispetto a un componente monolitico.

Riduzione dei Costi

Molti chiplet sono combinati con tecniche di confezionamento speciali per formare un IC più grande come alternativa a una struttura monolitica. Poiché i chiplet sono prodotti su un'area più piccola, solitamente su wafer circolari, l'impatto dei difetti di produzione è ridotto e l'utilizzo dell'area aumenta. Di conseguenza, il costo si riduce perché la resa del wafer è significativamente più alta quando i chiplet sono utilizzati per creare un componente.

L'integrazione eterogenea è un altro vantaggio significativo dei chiplet, in particolare in termini di riduzione dei costi di progettazione e produzione degli IC. Ogni chiplet può essere prodotto utilizzando diversi nodi di processo, cosa che AMD ha rivelato di aver fatto con il loro prodotto Ryzen 7. Un altro esempio da AMD è un recente brevetto per una GPU basata su chiplet; l'architettura di questo sistema è mostrata nell'illustrazione originale qui sotto:

Materiali multipli (ad es., chiplet GaN e Si) possono anche essere combinati nello stesso pacchetto con questo approccio. L'uso di diversi nodi tecnologici di processo riduce il rischio complessivo incorporato nel prodotto; il rischio più alto è confinato solo al chiplet che viene prodotto nel nodo di processo più avanzato, piuttosto che su tutto il chip.

Riuso del Design

Una volta sviluppato, un chiplet può essere riutilizzato, riducendo i costi di test e verifica. L'efficienza dei costi del processo di progettazione dei chip è significativamente più alta attraverso l'uso di moduli chiplet perché possono essere riutilizzati. Uno scenario di riutilizzo dei chiplet è progettare e produrre solo il chiplet principale per un IC, mentre i restanti chiplet nel pacchetto sono acquisiti da un altro fornitore. Utilizzando questo approccio con chiplet pronti all'uso da più fornitori, o riutilizzando IP in un nuovo design, si riducono notevolmente i costi totali di progettazione e verifica del prodotto.

In caso sia necessario un aggiornamento del sistema, un chiplet può essere sostituito con un altro chiplet all'interno del pacchetto. Da notare che il pacchetto stesso potrebbe necessitare di un aggiornamento, ma questo è molto meno difficile come compito di progettazione rispetto alla riprogettazione di un intero componente monolitico. Anche una piccola parte del sistema potrebbe essere ridisegnata senza incorrere in nuovi costi di verifica che sorgerebbero in pacchetti semiconduttori monolitici. Questo metodo di riutilizzo dei chiplet è denominato "riutilizzo eterogeneo".

Un altro scenario di riutilizzo dei chiplet è integrare più chiplet identici nello stesso sistema. Questo metodo è ideale per sistemi scalabili e migliora notevolmente la loro efficienza riducendo i costi. Questo è denominato metodo di riutilizzo omogeneo e il principale vantaggio è che aumentare il numero di chiplet nell'architettura è tutto ciò che serve per soddisfare le varie esigenze di prestazione e potenza.

Tecnologie di Imballaggio dei Chiplet

Per realizzare prodotti basati su chiplet, sono necessarie competenze di progettazione, die, connessioni tra i die e una strategia di produzione. Le prestazioni, il prezzo e la maturità delle tecnologie di imballaggio dei chiplet hanno un impatto sostanziale sull'applicazione dei chiplet. In base alle differenze nel mezzo di connessione e nei metodi, le tecnologie di imballaggio utilizzate per l'interconnessione dei chiplet possono essere classificate in tre gruppi:

-

Imballaggio su substrato

-

Imballaggio con interposer di silicio

-

Imballaggio con layer di ridistribuzione (RDL)

-

Ponte di interconnessione multi-die incorporato (EMIB)

Imballaggio Basato su Substrato

Nell'imballaggio basato su substrato, la scelta popolare del substrato è un materiale organico poiché questi sono facilmente disponibili. Similmente ai PCB convenzionali, le connessioni elettriche sono realizzate attraverso un processo di incisione che è indipendente da altri processi utilizzati nella fabbricazione dei semiconduttori. Questo è noto come la prima incarnazione della integrazione eterogenea 2D.

Attraverso il design flip-chip o l'impilamento, diversi die possono essere facilmente uniti a un substrato ad alta densità. Inoltre, i costi dei materiali e di produzione associati sono minimi perché questa tecnologia non dipende dal processo di fabbricazione dei chip. Il principale svantaggio dell'uso di questa tecnologia è la bassa densità dei pin di I/O e la conseguente limitazione nella larghezza di banda delle interconnessioni in questi pacchetti.

Imballaggio con Interposer di Silicio

Questa tecnologia abbraccia le tecnologie di packaging 2.5D e 3D, dove i chip sono costruiti lateralmente su un interposer (2.5D) o impilati verticalmente (3D). Per implementare gli interconnessioni e la comunicazione tra i die, lo strato di interposer in silicio è posizionato tra il substrato e i die. L'interposer funziona come un mini circuito stampato, fornendo essenzialmente un substrato per le connessioni elettriche tra i chiplet. Il tessuto di interconnessione è costruito da contatti metallici (chiamati micro bump) e attraverso-silicio vie (TSV) che corrono internamente nel pacchetto. Questi sono utilizzati per collegare il die all'interposer, e i connettori dell'interposer a un substrato del pacchetto con un pattern di atterraggio BGA.

Questi prodotti hanno una densità di I/O superiore con un consumo di energia ridotto e un ritardo di trasmissione inferiore. Questo è reso possibile dalla lunghezza e dal passo ridotti tra i micro bump e i TSV. L'unico svantaggio significativo di questa tecnologia è l'aumento dei costi di fabbricazione.

Packaging RDL

La tecnologia di packaging del layer di ridistribuzione (RDL) non utilizza un substrato, ma prevede la deposizione diretta del dielettrico e del metallo direttamente sulla superficie superiore del wafer. Questa tecnologia è anche conosciuta come tecnologia ‘fanout’. Per trasportare il design del filo, viene costruito un layer di ridistribuzione in modo tale che le porte I/O su ogni chiplet siano modellate intorno al dispositivo. Accorciando la lunghezza del circuito, RDL fornisce una maggiore integrità del segnale (minore perdita e distorsione).

Ponte di Interconnessione Multi-die Incorporato

EMIB è una tecnologia che utilizza sezioni di wafer in silicio sottile incorporate in materiali organici come substrati per interconnessioni die-to-die. Il problema dei costi più elevati nei prodotti avanzati può essere affrontato utilizzando il packaging a ponte con chiplet diversi. Questa tecnologia di packaging ibrido è una combinazione di packaging basato su substrato e basato su interposer. Strati sottili di silicio, generalmente inferiori a 75 micron, sono rivestiti sul substrato e utilizzati per formare connessioni inter-die, e questi strati sono incorporati in uno strato di substrato organico.

Il concetto segue le stesse idee in ELIC utilizzate negli HDI PCB, dove un tessuto di interconnessione per ogni strato collega più die a strati interni in un substrato isolante (organico). La parte EMIB del pacchetto è un ponte di silicio che fornisce connessioni ad alta larghezza di banda tra i chiplet.

Conclusione

Si prevede che i chiplet continueranno a rivoluzionare le applicazioni che richiedono componenti ad alta computazione così come funzionalità diverse in un unico pacchetto. Questi prodotti sono attualmente indirizzati verso tecnologie avanzate come 5G, IoT, automotive, edge computing, imaging medico, edge computing, AI, dispositivi mobili e molto altro ancora.

Oggi, importanti produttori di semiconduttori come Intel, Marvell e AMD si sono avventurati nella tecnologia dei chiplet, e possiamo aspettarci che più aziende esplorino questa opzione. Man mano che si sviluppa un mercato per l'IP dei chiplet, similmente a come si è sviluppato un mercato per molti altri componenti, più aziende di semiconduttori fabless potrebbero adottare un approccio di semiconduttori personalizzati piuttosto che costruire sistemi con componenti discreti.

Ora che Intel, AMD e TSMC hanno concordato uno standard comune per gli interconnettori dei chiplet, vedremo una maggiore proliferazione di questi progetti da parte di altre aziende? Si può sperare che si sviluppi un mercato per questi componenti poiché ciò incoraggerà più innovazione a livello di packaging oltre i grandi produttori di semiconduttori.

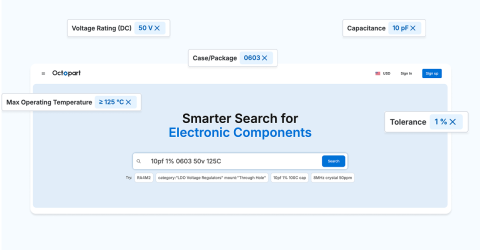

Con l'arrivo sul mercato di componenti basati su chiplet con packaging avanzato, i progettisti di sistemi possono utilizzare le funzionalità avanzate di ricerca e filtraggio in Octopart per trovare tutti i componenti avanzati di cui hanno bisogno per progetti avanzati. Utilizzando il motore di ricerca elettronica di Octopart, avrai accesso ai dati aggiornati sui prezzi dei distributori, all'inventario dei componenti e alle specifiche dei componenti, ed è tutto liberamente accessibile in un'interfaccia user-friendly. Dai un'occhiata alla nostra pagina sui circuiti integrati per trovare i componenti di cui hai bisogno.

Rimani aggiornato con i nostri ultimi articoli iscrivendoti alla nostra newsletter.