O Que São Chiplets e Como São Usados em Embalagens?

Chiplets são pequenos dies de CI com funcionalidade especializada. Eles são projetados para ser combinados a fim de compor um circuito integrado maior, seguindo a tendência da indústria de semicondutores de integração heterogênea. A capacidade de selecionar uma variedade de chips pequenos e altamente especializados, e depois combiná-los para produzir uma funcionalidade geral desejada, é um grande avanço em relação à abordagem tradicional de sistema em um chip (SoC) para embalagem de semicondutores. Grandes fornecedores produziram processadores de computador que combinam um número selecionado de chiplets, em vez de seguir o caminho tradicional da fabricação de semicondutores monolíticos, onde o dispositivo é fabricado em um único pedaço de silício.

Embora a ideia de chiplets exista há décadas, a embalagem baseada em chiplets está impulsionando novos tipos de componentes, produtos e sistemas para aplicações especializadas. Esses componentes são personalizados para aplicações específicas, e mais empresas estão entrando no jogo de design de chips com foco em chiplets como seu processador central. Baseado no número de artigos de pesquisa, aplicações de patentes e artigos técnicos que você encontrará online, está claro que os componentes baseados em chiplets vieram para ficar.

Se você é um designer de sistemas e está avaliando opções de processadores, talvez não perceba que chiplets formam a base para o seu sistema. No entanto, chiplets são a espinha dorsal que possibilita a diversidade de funcionalidades encontradas em chips modernos, e o conceito de embalagem continua a impulsionar a integração de novas características nos designs de chips. Exemplos incluem a integração de blocos FPGA e blocos aceleradores de IA no mesmo pacote que memórias, uma CPU e até componentes RF.

Por que Chiplets?

Custo e desempenho são as duas questões mais prementes no design e fabricação de chips. Os últimos anos viram o escalonamento de Dennard e a Lei de Moore desacelerarem, resultando em intervalos de tempo mais longos entre os nós de tecnologia de processo. Além disso, a integração de transistores em um chip monolítico está se tornando cada vez mais desafiadora, pois há poucas opções disponíveis para escalonamento de dispositivos. Esses desafios diminuíram o ROI para semicondutores monolíticos devido a processos de fabricação mais custosos.

A única maneira de aumentar o número de unidades funcionais integradas com o mesmo tamanho de transistor é expandir a área do chip, seja no plano do dispositivo ou verticalmente. O problema de aumentar a área do chip é que os chips maiores são mais suscetíveis a defeitos de fabricação, o que limita o rendimento do wafer e aumenta o preço dos produtos entregues aos clientes. Consequentemente, chips monolíticos estão se tornando cada vez mais incapazes de fornecer o desempenho desejado diante das crescentes demandas de computação.

Portanto, para suportar aplicações de alta computação como IA/ML embarcada, redes ultra-rápidas, fusão de sensores e dispositivos móveis de próxima geração, temos visto o surgimento de sistemas baseados em chiplets para o desenvolvimento custo-efetivo de eletrônicos de alto desempenho. Isso abrangeu desde SoCs avançados até processadores de desktop/servidor e GPUs.

Superando a "Barreira da Área"

O problema da "barreira da área" é o resultado de uma incompatibilidade entre a necessidade de chips de grande área por sistemas de computação de alto desempenho e o baixo rendimento da fabricação de semicondutores. A barreira da área refere-se a esse desafio na fabricação de semicondutores monolíticos, onde chips maiores são usados para aumentar a densidade de recursos, mas o número de defeitos também aumenta. À medida que as capacidades de processamento de fabricação avançam para nós mais sofisticados, o rendimento do processo diminui e, assim, o custo para o cliente final aumenta. Portanto, há sempre uma motivação para des-riscar a fabricação desses produtos eliminando chances de defeitos.

Uma solução para a barreira da área reduziria o custo geral de um produto final ao reduzir o desperdício durante a fabricação. Os chiplets essencialmente diversificam o perfil de risco de um produto ao distribuí-lo por vários dies semicondutores. O resultado final é a redução do custo e a capacidade de diversificar muito mais a funcionalidade do que em um componente monolítico.

Redução de Custos

Vários chiplets são combinados com técnicas especiais de embalagem para formar um CI maior como alternativa a uma estrutura monolítica. Como os chiplets são fabricados em uma área menor, geralmente em wafers circulares, o impacto dos defeitos de fabricação é reduzido e a utilização da área aumenta. Consequentemente, o custo é reduzido porque o rendimento do wafer é significativamente maior quando chiplets são usados para criar um componente.

Integração Heterogênea é outra vantagem significativa dos chiplets, particularmente em termos de redução dos custos de design e produção de ICs. Cada chiplet pode ser fabricado usando diferentes nós de processo, algo que a AMD revelou ter feito com seu produto Ryzen 7. Outro exemplo da AMD é uma patente recente para uma GPU baseada em chiplets; a arquitetura para este sistema é mostrada na arte original abaixo:

Materiais múltiplos (por exemplo, chiplets de GaN e Si) também podem ser combinados no mesmo pacote com esta abordagem. O uso de diferentes nós de tecnologia de processo reduz o risco geral incorporado ao produto; o maior risco está confinado apenas ao chiplet que está sendo produzido no nó de processo mais avançado, em vez de em todo o chip.

Reutilização de Design

Uma vez desenvolvido, um chiplet pode ser reutilizado, reduzindo o custo de testes e verificação. A eficiência de custo do processo de design de chips é significativamente maior através do uso de módulos chiplet porque eles podem ser reutilizados. Um cenário de reutilização de chiplet é projetar e fabricar apenas o chiplet central para um CI, enquanto os demais chiplets no pacote são adquiridos de outro fornecedor. Usar essa abordagem com chiplets prontos de vários fornecedores, ou reutilizando IP em um novo design, reduz grandemente os custos totais de design e verificação do produto.

Caso seja necessária alguma atualização no sistema, um chiplet pode ser substituído por outro dentro da embalagem. Note que a própria embalagem pode precisar ser atualizada, mas isso é muito menos difícil do que redesenhar um componente monolítico inteiro. Uma pequena parte do sistema também pode ser redesenhada sem incorrer em novos custos de verificação que surgiriam em pacotes semicondutores monolíticos. Esse método de reutilização de chiplet é denominado “reutilização heterogênea”.

Outro cenário de reutilização de chiplet é integrar vários chiplets idênticos no mesmo sistema. Esse método é ideal para sistemas escaláveis e melhora significativamente sua eficiência enquanto reduz custos. Isso é referido como o método de reutilização homogênea e a principal vantagem é que aumentar o número de chiplets na arquitetura é tudo o que é necessário para atender às diversas exigências de desempenho e energia.

Tecnologias de Embalagem de Chiplet

Para fazer produtos baseados em chiplet, você precisa de habilidades de design, dies, conexões entre os dies e uma estratégia de produção. O desempenho, preço e maturidade das tecnologias de embalagem de chiplet têm um impacto substancial na aplicação de chiplets. De acordo com as diferenças no meio de conexão e métodos, as tecnologias de embalagem usadas para interconexão de chiplets podem ser classificadas em três grupos:

-

Embalagem de substrato

-

Embalagem de interposer de silício

-

Embalagem de camada de redistribuição (RDL)

-

Ponte de interconexão multi-die embutida (EMIB)

Embalagem Baseada em Substrato

Na embalagem baseada em substrato, a escolha popular de substrato é um material orgânico, pois estes estão prontamente disponíveis. Semelhante às PCBs convencionais, conexões de fiação são feitas através de um processo de gravação que é independente de outros processos usados na fabricação de semicondutores. Isso é melhor conhecido como a primeira encarnação da integração heterogênea 2D.

Através do design flip-chip ou empilhamento, vários dies podem facilmente ser unidos a um substrato com alta densidade. Além disso, os custos de materiais e fabricação associados a isso são mínimos porque esta tecnologia não depende do processo de fabricação do chip. O principal inconveniente de usar esta tecnologia é a baixa densidade de pinos de E/S e a limitação resultante na largura de banda das interconexões nestes pacotes.

Embalagem de Interposer de Silício

Esta tecnologia abrange tecnologias de embalagem 2.5D e 3D, onde os chips são construídos lateralmente em um interposer (2.5D) ou empilhados verticalmente (3D). Para implementar interconexões e comunicação entre os dies, a camada de interposer de silício é colocada entre o substrato e os dies. O interposer é como uma miniatura de placa de circuito impresso, fornecendo essencialmente um substrato para conexões elétricas entre chiplets. O tecido de interconexão é construído a partir de contatos metálicos (chamados micro bumps) e vias através de silício (TSV) que correm internamente no pacote. Estes são usados para conectar o die ao interposer, e os conectores do interposer a um substrato de pacote com um padrão de terra BGA.

Estes produtos têm uma maior densidade de I/O com redução do consumo de energia e menor atraso de transmissão. Isso é possibilitado pelo menor comprimento de traço e distância entre micro bumps e TSVs. O único grande inconveniente desta tecnologia é o aumento dos custos de fabricação.

Embalagem RDL

A tecnologia de embalagem com camada de redistribuição (RDL) não utiliza um substrato, envolvendo em vez disso a deposição direta do dielétrico e do metal diretamente na superfície superior do wafer. Esta tecnologia também é referida como tecnologia ‘fanout’. Para transportar o design do fio, uma camada de redistribuição é construída de tal forma que as portas de I/O em cada chiplet são moldadas ao redor do dispositivo. Ao encurtar o comprimento do circuito, o RDL proporciona uma maior integridade de sinal (menor perda e distorção).

Ponte de Interconexão Multi-die Embutida

EMIB é uma tecnologia que usa seções finas de wafer de silício embutidas em materiais orgânicos como substratos para interconexões de die para die. O problema de custos mais altos em produtos avançados pode ser abordado usando embalagem com ponte com chiplets diversos. Esta tecnologia de embalagem híbrida é uma combinação de embalagem baseada em substrato e baseada em interposer. Camadas finas de silício, geralmente com menos de 75 microns, são revestidas no substrato e usadas para formar conexões entre dies, e estas camadas são embutidas em uma camada de substrato orgânico.

O conceito segue as mesmas ideias em ELIC usadas em PCBs HDI, onde um tecido de interconexão em cada camada conecta múltiplos dies a camadas internas em um substrato isolante (orgânico). A parte EMIB do pacote é uma ponte de silício que fornece conexões de alta largura de banda entre chiplets.

Conclusão

Espera-se que os chiplets continuem revolucionando aplicações que requerem componentes de alta computação, bem como funcionalidade diversa em um único pacote. Estes produtos estão atualmente visando tecnologias avançadas como 5G, IoT, automotivo, computação de borda, imagem médica, computação de borda, IA, dispositivos móveis e muito mais.

Hoje, grandes fabricantes de semicondutores como Intel, Marvell e AMD aventuraram-se na tecnologia de chiplets, e podemos esperar que mais empresas explorem essa opção. À medida que um mercado se desenvolve para IP de chiplets, de forma semelhante ao que aconteceu com muitos outros componentes, mais empresas de semicondutores fabless podem adotar uma abordagem de semicondutores personalizados em vez de construir sistemas com componentes discretos.

Agora que a Intel, AMD e TSMC concordaram com um padrão comum para interconexões de chiplets, veremos uma maior proliferação desses designs por outras empresas? Pode-se esperar que um mercado se desenvolva para esses componentes, pois isso incentivará mais inovação no nível de embalagem além dos grandes fabricantes de semicondutores.

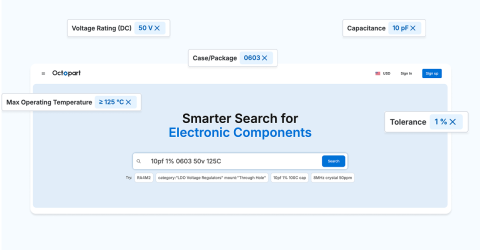

À medida que componentes baseados em chiplets com embalagens avançadas chegam ao mercado, os projetistas de sistemas podem usar os recursos avançados de busca e filtragem no Octopart para encontrar todos os componentes avançados de que precisam para designs avançados. Ao usar o motor de busca de eletrônicos do Octopart, você terá acesso a dados atualizados de preços de distribuidores, inventário de peças e especificações de peças, e tudo isso é livremente acessível em uma interface amigável ao usuário. Confira nossa página de circuitos integrados para encontrar os componentes de que precisa.

Mantenha-se atualizado com nossos últimos artigos ao inscrever-se em nossa newsletter.