Проект Pi.MX8 - Разметка платы Часть 3

Главы

Board Layout Part 3

| Created: June 24, 2024PCB Assembly

| Coming soonДобро пожаловать в новый выпуск проекта открытого компьютерного модуля Pi.MX8! В этой серии мы погружаемся в дизайн и тестирование системы на модуле на основе процессора i.MX8M plus от NXP.

В предыдущем обновлении мы завершили подготовку компоновки. Это включало создание профилей импеданса, добавление правил дизайна в соответствии со спецификациями производителя плат и определение областей, где должны применяться специальные правила дизайна. Мы также завершили трассировку интерфейса LPDDR4, но пока без настройки длины.

Прежде чем мы начнем настройку длины интерфейса DRAM, мы рассмотрим трассировку оставшихся интерфейсов на модуле Pi.MX8. На плате есть довольно много шин высокой и низкой скорости, некоторые из которых являются широкими параллельными шинами, занимающими много места для трассировки. Чтобы выделить достаточно места для каждого интерфейса, мы сначала создадим приблизительный план компоновки для каждого слоя трассировки на модуле.

Планирование трассировки

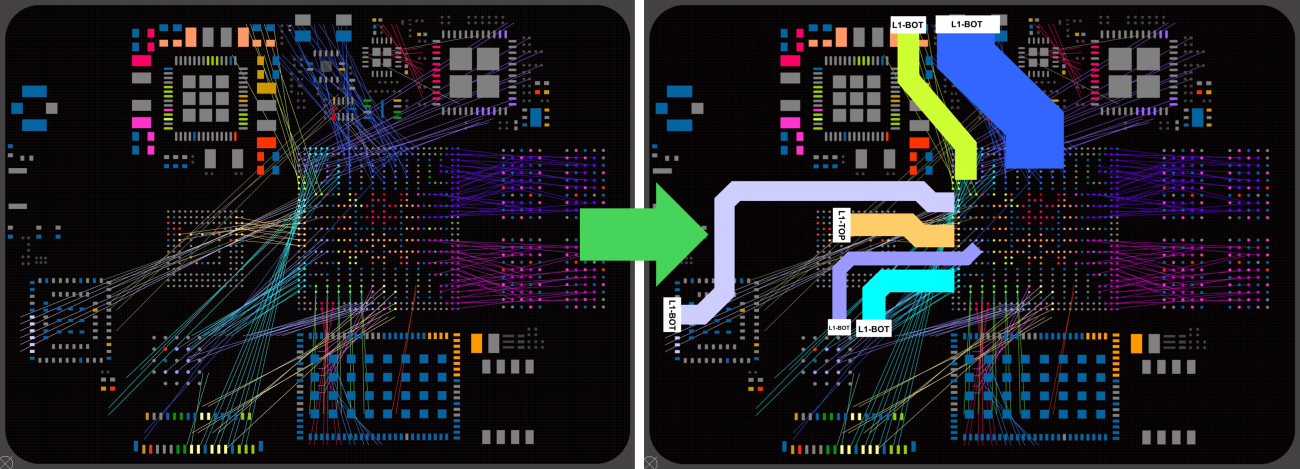

План трассировки поможет нам определить, как распределить все интерфейсы высокой и низкой скорости по доступным слоям сигналов. Создав заранее примерное руководство, мы можем убедиться, что у нас достаточно места для трассировки на слое, над которым мы в данный момент работаем. Это также помогает нам минимизировать переходы между слоями и уменьшить объем переделок, которые придется выполнять в процессе трассировки.

Существует несколько способов настройки планирования компоновки, в основном зависящих от доступных инструментов. Нам просто нужен базовый инструмент для рисования, который позволяет набросать эскиз поверх существующего изображения. В этом примере мы будем использовать Inkscape.

В Inkscape мы можем добавить фоновое изображение, которое показывает размещение компонентов и непроложенные интерфейсы в виде цветных воздушных линий. Обратите внимание, что силовые сети скрыты на этом снимке экрана, поскольку мы сосредоточимся только на сетях, которые будут проложены на слоях сигналов. На схеме мы разместили директиву класса сети на каждую силовую сеть, что позволяет легко идентифицировать, какие сети проложены на слоях плоскостей, просто включив или скрыв связанный класс сети в редакторе компоновки.

Для непосредственной трассировки мы просто добавляем линии в Inkscape, чтобы представить интерфейсы, которые мы хотим проложить на соответствующем слое. Мы можем настроить ширину этих линий, чтобы показать, сколько сигналов будет проложено в интерфейсе. Цвет линии можно выбрать из фонового изображения, чтобы было проще идентифицировать, какой интерфейс представлен.

Поскольку переходы между слоями также требуют выделения места на всех слоях, мы можем добавить блок в конец каждой линии, детализирующий переход между слоями.

Планирование компоновки в Inkscape с использованием скриншота Altium Designer в качестве фонового изображения

После того как мы повторили вышеописанный процесс для каждого слоя трассировки, мы можем приступить к непосредственному процессу трассировки.

Трассировка верхнего слоя

С учетом стратегии трассировки, давайте начнем с трассировки интерфейсов на верхнем слое. Поскольку мы уже выполнили трассировку разводки для компонентов на верхнем слое, мы можем использовать все оставшееся пространство для трассировки сигналов. Свободного места осталось немного, но то, что у нас есть, все еще может быть использовано для упрощения трассировки на внутренних слоях сигналов за счет стратегического размещения переходных отверстий (VIA) в областях, которые не будут мешать трассировке на внутренних слоях позже. Это еще одно преимущество предварительного планирования компоновки, иначе эти области не были бы определены на данном этапе.

Трассировка верхнего слоя модуля PiMX8

При размещении дорожек на верхнем слое мы также должны учитывать, что нам нужно немного места для добавления таких элементов, как маркеры или метки на верхнем слое. Для лазерно-гравированных кодовых матриц также может потребоваться либо сплошная медная область, либо область без дорожек, чтобы обеспечить однородный контраст, что означает, что эти области не могут быть использованы для трассировки.

Трассировка внутренних слоев сигналов

Большинство соединений будет размещено на двух внутренних слоях сигналов, которые мы определили в менеджере стека слоев. Давайте начнем с прокладки всех высокоскоростных синхронных интерфейсов. В нашем случае это могут быть интерфейсы MIPI-CSI, MIPI-DSI и LVDS. Все эти интерфейсы используют низковольтную дифференциальную сигнализацию и имеют выделенную линию тактового сигнала и как минимум две линии данных. Для их прокладки требуется много места, поскольку длина каждой линии данных должна соответствовать линии тактового сигнала в пределах определенного временного зазора. Согласование длины нескольких дифференциальных пар может потребовать много места, так как весьма вероятно, что одна или несколько пар внутри интерфейса внесут значительную задержку, которую необходимо учесть. Прокладывая эти интерфейсы в первую очередь, мы можем убедиться, что позже будет достаточно места для настройки длины.

Размещение возвратных путей VIA рядом с переходами слоев этих высокоскоростных дифференциальных пар также важно для обеспечения целостности сигнала. Возвратные пути VIA могут занимать место на нескольких слоях, поэтому эти VIA следует размещать как только будет выполнен переход сигнала.

Далее мы можем проложить другие интерфейсы высокой скорости, такие как PCIe, USB, HDMI и Ethernet. Для этих интерфейсов требования к согласованию длин между парами менее строгие, поэтому нам не нужно выделять столько места для согласования длин. Тем не менее, управление твердым возвратным путем и базовые подходы к проектированию высокоскоростных сигналов по-прежнему очень важны, хотя их размещение на втором месте в списке приоритетов трассировки.

Наконец, мы можем проложить оставшиеся интерфейсы низкой скорости, такие как SDIO, GPIO, RGMII и другие разнообразные шины, такие как UART или I2C и SPI. Эти интерфейсы все еще работают на высоких скоростях фронтов сигнала, что означает, что мы все еще должны обрабатывать их как высокоскоростные сигналы.

Трассировка внутреннего слоя сигналов 1

Трассировка внутреннего слоя сигналов 2

Трассировка нижнего слоя

В случае платы PiMX8 мы можем рассматривать нижний слой как внутренний слой трассировки с точки зрения доступного пространства. Большинство активных компонентов размещены на верхнем слое модуля, оставляя на нижнем слое лишь несколько регуляторов напряжения и пассивных компонентов, таких как развязывающие конденсаторы и резисторы конфигурации.

Приоритет трассировки на нижнем слое такой же, как и для внутренних слоев, поэтому мы начнем с интерфейсов MIPI-CSI, MIPI-DSI и LVDS. На модуле PiMX8 высокоскоростной мультиплексор может выбирать между портами DSI и LVDS. Этот компонент размещается на нижнем слое рядом с разъемом соединения плат. Из-за распиновки мультиплексора на одной из сигнальных линий, подключенных к мультиплексору, возникает значительная задержка. Нам придется более внимательно рассмотреть это в процессе согласования длин, но нам нужно зарезервировать некоторое пространство на нижнем слое, чтобы позволить большую задержку.

Распиновка мультиплексора с одной длинной линией в интерфейсе

Трассировка нижнего слоя модуля PiMX8

На модуле PiMX8 есть несколько сценариев, требующих особого внимания при настройке задержек. Мы будем широко использовать X-сигналы, чтобы преодолеть некоторые из этих проблем. Что именно эти проблемы представляют собой и как мы можем реализовать X-сигналы для точной настройки задержек на компоненте, используемом несколькими интерфейсами, будет частью следующего обновления. Следите за новостями!