Что такое чиплеты и как они используются в упаковке?

Чиплеты — это маленькие кристаллы интегральных схем с специализированной функциональностью. Они разработаны для объединения в более крупную интегральную схему, следуя тенденции полупроводниковой промышленности к гетерогенной интеграции. Возможность выбора из набора маленьких, высокоспециализированных чипов и их сочетание для получения желаемой общей функциональности является значительным шагом вперед по сравнению с традиционным подходом системы-на-чипе (SoC) к упаковке полупроводников. Крупные производители выпустили компьютерные процессоры, которые объединяют определенное количество чиплетов, вместо того чтобы идти по традиционному пути монолитного производства полупроводников, где устройство изготавливается на едином куске кремния.

Хотя идея чиплетов существует уже десятилетия, упаковка на основе чиплетов стимулирует появление новых типов компонентов, продуктов и систем для специализированных приложений. Эти компоненты адаптированы для конкретных приложений, и все больше компаний включаются в разработку чипов с акцентом на чиплетах в качестве их основного процессора. Основываясь на количестве научных статей, заявок на патенты и технических статей, которые вы найдете в Интернете, очевидно, что компоненты на основе чиплетов пришли, чтобы остаться.

Если вы системный дизайнер и вы взвешиваете варианты процессоров, вы можете не осознавать, что чиплеты составляют основу вашей системы. Однако чиплеты являются костяком, обеспечивающим разнообразную функциональность, найденную в современных чипах, и концепция упаковки продолжает стимулировать интеграцию новых функций в дизайн чипов. Примеры включают интеграцию блоков FPGA и блоков ускорителей ИИ в один и тот же пакет, что и память, ЦПУ и даже РЧ компоненты.

Почему чиплеты?

Стоимость и производительность являются двумя наиболее насущными проблемами в дизайне и производстве чипов. В последние годы замедление масштабирования по Деннарду и Закона Мура привело к увеличению временных промежутков между технологическими узлами. Кроме того, интеграция транзисторов на монолитном чипе становится все более сложной задачей, поскольку существует мало вариантов для масштабирования устройств. Эти вызовы снизили ROI для монолитных полупроводников из-за более дорогих производственных процессов.

Единственный способ увеличить количество интегрированных функциональных блоков с тем же размером транзистора - это расширить площадь чипа, либо в плоскости устройства, либо вертикально. Проблема увеличения площади чипа заключается в том, что большие чипы более подвержены производственным дефектам, что ограничивает выход пластин и увеличивает цену продуктов, поставляемых клиентам. Следовательно, монолитные чипы становятся все менее способными обеспечивать желаемую производительность на фоне растущих вычислительных требований.

Поэтому, чтобы поддержать приложения с высокой вычислительной мощностью, такие как искусственный интеллект и машинное обучение на устройстве, сверхбыстрые сети, слияние датчиков и мобильные устройства следующего поколения, мы наблюдаем появление систем на основе чиплетов для экономичной разработки высокопроизводительной электроники. Это охватывает от продвинутых SoC до процессоров для настольных компьютеров/серверов и GPU.

Преодоление «стены площади»

Проблема «стены площади» возникает из-за несоответствия между потребностью систем высокопроизводительных вычислений в крупноплощадных чипах и низким выходом полупроводникового производства. «Стена площади» относится к этой проблеме в монолитном полупроводниковом производстве, где для увеличения плотности функций используются большие чипы, но также увеличивается и количество дефектов. По мере перехода производственных возможностей к более продвинутым узлам, выход процесса уменьшается, а следовательно, стоимость для конечного потребителя увеличивается. Поэтому всегда есть мотивация снизить риски производства этих продуктов, исключая возможности для дефектов.

Решение проблемы «стены площади» могло бы снизить общую стоимость конечного продукта за счет уменьшения отходов в производстве. Чиплеты по сути диверсифицируют профиль риска для продукта, распределяя его между несколькими полупроводниковыми кристаллами. В результате стоимость снижается, и возможности значительно расширения функциональности становятся гораздо шире, чем в монолитном компоненте.

Снижение стоимости

Несколько чиплетов объединяются с помощью специальных технологий упаковки для создания большой ИС в качестве альтернативы монолитной структуре. Поскольку чиплеты производятся на меньшей площади, обычно на круглых пластинах, влияние дефектов производства уменьшается, а использование площади увеличивается. Следовательно, стоимость снижается, поскольку выход пластин значительно выше, когда для создания компонента используются чиплеты.

Гетерогенная интеграция является еще одним значительным преимуществом чиплетов, особенно с точки зрения снижения стоимости проектирования и производства ИС. Каждый чиплет может быть изготовлен с использованием различных технологических узлов, что, как раскрыла AMD на примере своего продукта Ryzen 7. Еще один пример от AMD - недавний патент на GPU на основе чиплетов; архитектура этой системы показана на оригинальном изображении ниже:

Также можно комбинировать несколько материалов (например, чиплеты из GaN и Si) в одной упаковке. Использование различных технологических узлов снижает общий риск, заложенный в продукт; наибольший риск ограничивается только чиплетом, который производится на самом передовом технологическом узле, а не по всему чипу.

Повторное использование дизайна

Как только чиплет разработан, его можно использовать повторно, что снижает стоимость тестирования и верификации. Эффективность стоимости процесса проектирования чипов значительно выше за счет использования модулей чиплетов, поскольку их можно использовать повторно. Один из сценариев повторного использования чиплета заключается в том, чтобы разработать и изготовить только основной чиплет для ИС, в то время как остальные чиплеты в пакете приобретаются у другого поставщика. Использование этого подхода с готовыми чиплетами от нескольких поставщиков или повторное использование IP в новом дизайне значительно снижает общие затраты на проектирование и верификацию продукта.

В случае необходимости обновления системы один чиплет можно заменить на другой внутри упаковки. Обратите внимание, что сама упаковка может потребовать обновления, но это гораздо менее сложная задача по проектированию, чем перепроектирование целого монолитного компонента. Небольшая часть системы также может быть перепроектирована без необходимости нести новые затраты на верификацию, которые возникли бы в монолитных полупроводниковых пакетах. Этот метод повторного использования чиплетов называется «гетерогенное повторное использование».

Еще один сценарий повторного использования чиплетов заключается в интеграции нескольких идентичных чиплетов в одну и ту же систему. Этот метод идеален для масштабируемых систем и значительно повышает их эффективность, снижая при этом стоимость. Это называется методом однородного повторного использования, и его главное преимущество заключается в том, что для удовлетворения различных требований к производительности и энергопотреблению достаточно увеличить количество чиплетов в архитектуре.

Технологии упаковки чиплетов

Для создания продуктов на основе чиплетов вам потребуются навыки проектирования, кристаллы, соединения между кристаллами и стратегия производства. Производительность, цена и зрелость технологий упаковки чиплетов оказывают существенное влияние на применение чиплетов. В зависимости от различий в среде и методах соединения, технологии упаковки, используемые для взаимосвязи чиплетов, могут быть классифицированы на три группы:

-

Упаковка на подложке

-

Упаковка с использованием кремниевого интерпозера

-

Упаковка с перераспределительным слоем (RDL)

-

Встроенный мост многокристального взаимосвязи (EMIB)

Упаковка на основе подложки

В упаковке на основе подложки популярным выбором материала для подложки является органический материал, поскольку он широко доступен. Аналогично традиционным печатным платам, соединения проводов создаются с помощью процесса травления, который не зависит от других процессов, используемых в производстве полупроводников. Это лучше всего известно как ранняя инкарнация 2D гетерогенной интеграции.

С помощью дизайна flip-chip или стекирования несколько кристаллов могут быть легко соединены с подложкой с высокой плотностью. Более того, материалы и затраты на производство, связанные с этим, минимальны, поскольку эта технология не зависит от процесса производства чипов. Основным недостатком использования этой технологии является низкая плотность выводов ввода/вывода и, как следствие, ограничение пропускной способности межсоединений в этих пакетах.

Упаковка с использованием кремниевого интерпозера

Эта технология охватывает технологии упаковки 2.5D и 3D, где чипы строятся горизонтально на интерпозере (2.5D) или вертикально стыкуются (3D). Для реализации соединений и коммуникации между кристаллами, слой силиконового интерпозера размещается между подложкой и кристаллами. Интерпозер подобен миниатюрной печатной плате, по сути, обеспечивая подложку для электрических соединений между чиплетами. Ткань соединений создается из металлических контактов (называемых микро-выступами) и сквозных кремниевых переходов (TSV), проходящих внутри пакета. Они используются для соединения кристалла с интерпозером, а соединители интерпозера с подложкой пакета с узором BGA.

Эти продукты имеют более высокую плотность ввода/вывода при сниженном потреблении энергии и меньшей задержке передачи. Это достигается за счет меньшей длины и шага между микро-выступами и TSV. Единственным значительным недостатком этой технологии являются увеличенные затраты на производство.

Упаковка RDL

Технология упаковки с перераспределительным слоем (RDL) не использует подложку, вместо этого происходит прямое нанесение диэлектрика и металла непосредственно на верхнюю поверхность пластины. Эта технология также известна как технология «fanout». Для передачи дизайна проводов создается перераспределительный слой таким образом, чтобы порты ввода/вывода на каждом чиплете были расположены вокруг устройства. Сокращая длину цепи, RDL обеспечивает большую целостность сигнала (меньшие потери и искажения).

Встроенный многочиповый межсоединительный мост

EMIB - это технология, использующая тонкие секции кремниевой пластины, встроенные в органические материалы в качестве подложек для межкристальных соединений. Проблему высоких затрат на продвинутые продукты можно решить с помощью упаковки мостов с различными чиплетами. Эта гибридная технология упаковки является комбинацией упаковки на основе подложки и упаковки на основе интерпозера. Тонкие слои кремния, обычно менее 75 микрон, наносятся на подложку и используются для формирования межкристальных соединений, и эти слои встраиваются в органический слой подложки.

Концепция следует тем же идеям, что и ELIC, используемые в HDI PCB, где ткань соединений каждого слоя соединяет несколько кристаллов с внутренними слоями в изолирующей (органической) подложке. Часть упаковки EMIB представляет собой кремниевый мост, обеспечивающий высокопропускные соединения между чиплетами.

Заключение

Ожидается, что чиплеты будут продолжать революционизировать приложения, требующие высокопроизводительных компонентов, а также разнообразной функциональности в одном пакете. В настоящее время эти продукты нацелены на передовые технологии, такие как 5G, IoT, автомобильная промышленность, вычисления на периферии, медицинская визуализация, вычисления на периферии, ИИ, мобильные устройства и многое другое.

Сегодня крупные производители полупроводников, такие как Intel, Marvell и AMD, начали использовать технологию чиплетов, и мы можем ожидать, что больше компаний изучат этот вариант. По мере развития рынка IP для чиплетов, аналогично тому, как рынок развивался для многих других компонентов, больше бесфабричных полупроводниковых компаний могут выбрать подход к созданию индивидуальных полупроводников вместо создания систем с дискретными компонентами.

Теперь, когда Intel, AMD и TSMC договорились о едином стандарте для межсоединений чиплетов, увидим ли мы большее распространение этих дизайнов другими компаниями? Можно надеяться, что рынок для этих компонентов разовьется, так как это будет способствовать большему инновационному развитию на уровне упаковки за пределами крупных полупроводниковых производителей.

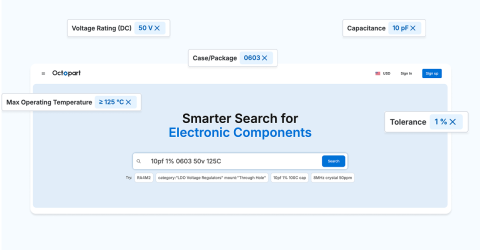

По мере появления на рынке компонентов на основе чиплетов с передовой упаковкой, системные дизайнеры могут использовать расширенные функции поиска и фильтрации в Octopart, чтобы найти все необходимые им передовые компоненты для сложных проектов. Используя поисковую систему электроники Octopart, вы получите доступ к актуальным данным о ценах дистрибьюторов, инвентаризации компонентов и спецификациям деталей, и все это доступно в удобном для пользователя интерфейсе. Посмотрите нашу страницу с интегральными схемами, чтобы найти необходимые вам компоненты.

Оставайтесь в курсе наших последних статей, подписавшись на нашу рассылку.