Dự án Thiết kế PCB Mô-đun ADC Kép

Dự án này khảo sát các ADC trên một PCB, bao gồm việc đặt và định tuyến liên quan đến một ADC cô lập.

Nhấn vào đây để chuyển tới phần nhúng trình xem và duyệt qua dự án này

Nếu bo mạch của bạn bao gồm một ADC, thì bo mạch của bạn được xem là một hệ thống tín hiệu hỗn hợp và sẽ cần một số phương pháp bố trí cụ thể để ngăn chặn tiếng ồn dư thừa trên các đường tín hiệu analog. ADC thường là các thành phần không cô lập, nhưng chúng cũng có dạng cô lập, nơi mà thành phần cung cấp cách ly galvanic giữa phía analog và phía số.

Trong dự án này, tôi sẽ trình bày một thiết kế ví dụ sử dụng cả hai loại ADC trong cùng một bố trí PCB. Những thành phần này yêu cầu các phương pháp bố trí khác nhau, nhưng chúng tôi sẽ thực hiện chúng trên cùng một bo mạch để cung cấp một sự so sánh tốt.

Như trong tất cả các dự án của chúng tôi, có một liên kết để tải về các tệp nguồn cho dự án này ở cuối bài viết. Để tìm hiểu thêm về việc sử dụng các loại thành phần này và để theo dõi toàn bộ quá trình bố trí, bạn có thể xem danh sách phát bên dưới.

Bắt đầu với Mô-đun ADC

Mô-đun ADC mà tôi sẽ trình bày trong dự án này được dự định để thu thập hai tín hiệu và truyền dữ liệu đến một tiêu đề chân, có thể sau đó kết nối với một bo mạch bên ngoài như một mô-đun vi điều khiển. Mô-đun sẽ bao gồm bộ phận chính sau:

- ISL75051ASEHVFE - Mô-đun điều chỉnh nguồn từ 5V xuống 3V3 chịu bức xạ

- ADC128S102CIMTX - ADC 12-bit, 8 kênh, từ 0.5 đến 1 MSps

- AMC1203BPSA - ADC cảm biến dòng cách ly sigma-delta 8-bit, một kênh, 40 kSps

Các tín hiệu được thu thập được dự định ở tần số thấp, như được chứng minh bởi tốc độ lấy mẫu thấp của chúng. Cả hai ADC đều giả định nguồn có trở kháng thấp, vì vậy chúng ta không cần bộ lọc hoạt động với bộ đệm trở kháng, và chúng ta có thể kết nối trực tiếp vào đầu vào ADC nếu muốn. Cuối cùng, bất kỳ ai quen thuộc với các linh kiện của Intersil sẽ lưu ý rằng ISL75051ASEHVFE là một bộ điều chỉnh chịu bức xạ; mô-đun này có thể được sử dụng trong hệ thống vũ trụ miễn là hai thành phần khác có thể được chứng nhận cho hàng không vũ trụ.

Sơ đồ của ADC cách ly và không cách ly

Hình ảnh dưới đây hiển thị hai phần chính của sơ đồ cho mô-đun này: ADC cách ly và không cách ly. Các thành phần và mạch còn lại có thể được xem trong các tệp dự án.

Sơ đồ mạch rất đơn giản; chúng ta chỉ cần một trang cho tất cả các mạch. Chúng ta có hai nguồn điện riêng biệt, một cho phía cách ly qua một SMA, và một cho phía không cách ly qua cổng pin.

Đầu tiên, hãy xem sơ đồ của ADC cách ly (AMC1203BPSA) như được hiển thị dưới đây.

Tham chiếu tương tự cho thành phần này được thiết lập nội bộ, vì vậy chúng ta không cần một chip tham chiếu chính xác để thiết lập phạm vi đo lường. Lưu ý rằng ADC cách ly yêu cầu hai mạng điện khác nhau (+5V và +5V_AN), cả hai đều ở +5V dựa trên bảng dữ liệu; những nguồn này phải đến từ các nguồn cung cấp khác nhau để đảm bảo cách ly galvanic được duy trì qua khoảng cách cách ly trong thành phần này. J1 và J3 là các kết nối cho tín hiệu tương tự đến và nguồn điện cho phần tương tự của ADC.

Để bảo vệ tín hiệu đến một cách đúng đắn, các tín hiệu đến ADC cách ly và không cách ly được cung cấp sử dụng cáp đồng trục với kết nối SMA dọc (73251-1350 từ Molex). Những kết nối này và cáp đồng trục gắn kèm sẽ có trở kháng 50 Ohms, nhưng các tín hiệu đầu vào sẽ đủ thấp đến mức chỉ có sự tương tác đáng kể giữa nguồn và tải trong hệ thống.

Tiếp theo, hãy xem mạch của ADC tiêu chuẩn.

Trong mạch này, nguồn được cung cấp bởi bộ điều chỉnh (mạch 3V3), mà lại nhận nguồn từ kết nối +5V từ chân cắm. Đầu ra SPI sử dụng một điện trở để làm chậm tốc độ cạnh một chút trước khi định tuyến tín hiệu ra ngoài bo mạch. Các tụ điện cũng được đặt cụ thể cho việc giảm nhiễu/qua mạch cho các chân VA và VD.

Có một số giả định trong sơ đồ trên:

- Mạch +5V_AN sẽ không bao giờ cần dòng điện cao trên bo mạch này, do đó việc sử dụng cáp SMA + coax cho nguồn điện là phù hợp. Các điện áp/dòng điện cao hơn qua đó sẽ yêu cầu các linh kiện khác nhau.

- Băng thông tín hiệu đầu vào chỉ bị giới hạn bởi tốc độ lấy mẫu của mỗi ADC. Nếu cần băng thông thấp hơn, thêm một bộ lọc RC thông thấp và chạy ở tốc độ lấy mẫu tối đa để chống nhiễu.

- Kết nối +5V trên chân cắm được giả định là được điều chỉnh và tương đối không nhiễu. Nếu không được điều chỉnh, một bộ điều chỉnh +5V sẽ cần thiết ở đầu vào.

- Các chân VA và VD trên U2 không được cô lập vì U2 là thành phần duy nhất kéo cạnh số nhanh cho giao diện SPI của nó. Nếu có nhiều thành phần hơn trên bus 3V3, thì chúng ta chắc chắn sẽ muốn xem xét giới hạn băng thông nguồn cho chân VA gần 1 MHz.

Với những điểm này đã được giải quý, chúng ta có thể tiếp tục với việc xếp chồng. Bản xếp chồng của chúng ta cần phải hỗ trợ 2 giao diện số tốc độ cao hợp lý (một cho mỗi ADC) và hai đường cấp dẫn riêng biệt vào các ADC.

Lập kế hoạch sàn và Xếp chồng PCB

Vì bo mạch này chứa một thành phần cô lập, nên bo mạch cần có một kế hoạch sàn cụ thể cho phép một khu vực cô lập. Chúng ta có thể thực hiện mọi thứ trên bo mạch này trên một lớp duy nhất, nhưng chúng ta cần có mặt đất để ngăn chặn sự cảm ứng từ giữa các phần analog và số, điều này đòi hỏi một mặt đất nội bộ. Do đó, chúng ta có thể sử dụng một bản xếp chồng PCB 4 lớp đơn giản với GND nội bộ.

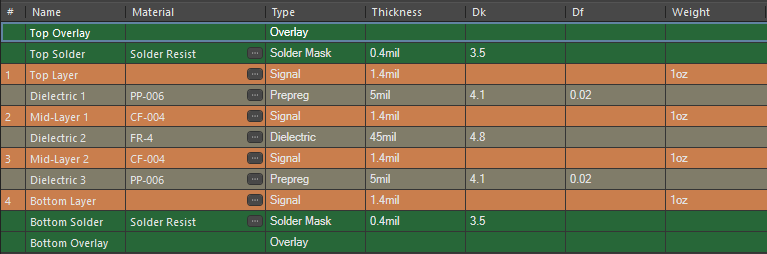

Bản xếp chồng hoàn chỉnh được hiển thị bên dưới. Trong bản xếp chồng này, chúng ta đã sử dụng một SIG+PWR/GND/GND/SIG xếp chồng; các thành phần sẽ ở phía trên và phía dưới có thể được sử dụng cho việc định tuyến bổ sung khi cần thiết.

Trong bản xếp chồng này, giá trị Dk không quan trọng lắm vì chúng ta không có yêu cầu về trở kháng kiểm soát. Điểm quan trọng ở đây là lớp ngoài mỏng, cũng như GND trên L2 và L3. Lớp ngoài mỏng kề với mặt đất là chìa khóa để giảm tiếng ồn, như tôi đã chỉ ra trong một bài viết khác về trích xuất nhiễu.

Tiếp theo, phần cô lập cần được đặt trong khu vực riêng của nó với các kết nối SMA cung cấp điện và tín hiệu. Tôi đã cô lập phần này vào phía bên trái của bảng mạch, trong khi các thành phần còn lại sẽ được đặt ở phía bên phải. Vị trí đặt ban đầu được hiển thị bên dưới.

Vị trí đặt ban đầu xếp tất cả các phần tương tự ở phía bên trái của bảng mạch, trong khi bộ điều chỉnh và các dòng I/O được định tuyến trực tiếp ra phía bên phải (chủ yếu trên lớp sau). Đây là một chiến lược điển hình để giảm thiểu sự cộng hưởng nhiễu giữa các dòng kỹ thuật số và các đường dẫn tương tự. Ranh giới cô lập chạy dọc theo dưới U3, vì vậy đó là nơi chúng tôi sẽ chia mạng đất thành GND và AGND để duy trì sự cô lập cần thiết.

Để thực hiện việc chia này, tôi đã triển khai một khu vực đổ đồng nhỏ mở rộng qua tất cả 4 lớp trong PCB. Khu vực này cung cấp các kết nối AGND trên J1 và J3, và các lớp sẽ được kết nối với nhau bằng các via khâu.

Các kết nối nhiệt trên các pad SMA sẽ được loại bỏ bằng cách thay đổi các quy tắc thiết kế. Tôi sử dụng một chiến lược tương tự trong phần không cô lập, nhưng sự khác biệt là lớp đổ trên L2 chạy dưới toàn bộ kết nối ADC. Tôi cũng sẽ thêm các via khâu vào phần đó để giảm nhiễu. Với điểm này hoàn thành, chúng ta giờ đây có thể bắt đầu định tuyến phần còn lại của các kết nối.

Một điểm tôi muốn lưu ý ở đây là vị trí đặt tụ điện. Giống như trường hợp với một thành phần số, việc đặt bất kỳ tụ điện nào cung cấp điện cho chân điện áp analog gần với những chân đó là quan trọng. Như vậy, hệ thống analog sẽ có thể rút điện năng đủ trong khoảng thời gian lấy mẫu của nó và sẽ có sự giảm thiểu tối thiểu cho bất kỳ tham chiếu nội bộ nào. Một ví dụ được hiển thị bên dưới. Cụ thể, chúng tôi đã đặt C18 và C19 cho nguồn cung cấp số, và C16 và C17 cho phía analog.

Hoàn thiện Định Tuyến và Bố Cục

Sau khi điều chỉnh vị trí một số linh kiện, tôi đã có thể di chuyển các tụ lớn (C9 và C13) sao cho chúng nằm gần trung tâm của bảng mạch hơn. Điều này cho phép tôi giảm kích thước bảng mạch một chút để không có khu vực rộng lớn nào không có linh kiện hoặc đường dẫn. Sau đó, ở L2 và L3, tôi đã chạy mặt đất ở khắp mọi nơi để giữ cho phân phối đồng trong stackup chủ yếu là đối xứng. Đường dẫn cuối cùng, bao gồm cả vias nối, được hiển thị bên dưới.

Trong góc nhìn này, bạn có thể thấy đầu vào +5V và đầu ra +3V3 được định tuyến dưới dạng đa giác lớn, trong khi các đa giác khác trên lớp trên cùng là GND hoặc AGND. Tất cả tín hiệu số được định tuyến trên lớp dưới cùng trừ những điểm chúng cần kết nối với các ADC trên L1.

Một góc nhìn 3D của bố cục PCB đã hoàn thiện được hiển thị trong hình dưới đây. Như thường lệ, chúng tôi có một số logo, cũng như một huyền thoại silkscreen cho bảng chân trên pin header. Các SMA đặt ở phía bên trái có vias nối để kết nối khu vực đất đó lại với nhau trên tất cả các lớp và để ngăn chặn sự can thiệp RF lạc đường lan truyền vào phần đó của chất nền. Những đường này cũng không được thiết kế theo một trở kháng cụ thể, và giả định ở đây là các tín hiệu đầu vào sẽ có tần số thấp đến mức các đường dẫn điện tử là ngắn.

Chúng ta có thể thêm gì vào mô-đun này?

Thiết kế như đã trình bày ở trên nhằm mục đích giao tiếp với một mô-đun vi điều khiển bên ngoài để thu thập và xử lý dữ liệu qua cổng pin. Để tiếp tục phát triển bảng mạch này, người ta có thể đặt một phần kỹ thuật số với vi điều khiển ở lớp sau, nơi vi điều khiển nhận dữ liệu được cung cấp bởi các đầu ra từ các ADC. Một vi điều khiển nhỏ như PIC (từ Microchip) hoặc một STM32 nhỏ hơn (ST Microelectronics) sẽ phù hợp cho mô-đun này.

Thiết kế hiện tại giả định một trở kháng nguồn thấp và không có bộ lọc để giới hạn băng thông của tín hiệu được thu thập bởi thiết bị. Điều này đã được giới hạn bởi tốc độ lấy mẫu dựa trên tốc độ lấy mẫu Nyquist, nhưng các tín hiệu tần số thấp có thể được lấy mẫu quá mức và đưa qua bộ lọc chống nhiễu RC để giảm tiếng ồn thêm.

Nếu bạn sử dụng một vi điều khiển trên lớp sau, nó sẽ có giao diện đầu ra để gửi dữ liệu đến thiết bị khác, chẳng hạn như máy tính. Điều này có thể được thực hiện qua giao diện UART, hoặc trực tiếp qua USB. Tùy chọn UART hữu ích vì nó có thể sau đó được kết nối với một đầu nối 2 chân, sau đó sẽ được kết nối với thiết bị đích. Vì rất nhiều vi điều khiển có tùy chọn UART, dự án tiếp theo mà tôi sẽ trình bày sẽ là một mô-đun chuyển đổi UART sang USB có thể nhận dữ liệu từ vi điều khiển như tôi đã mô tả ở đây.

Theo dõi liên kết này để tải xuống một lưu trữ ZIP với các tệp nguồn của dự án. Bạn cũng có thể sử dụng liên kết tải xuống trong phần nhúng ở trên để truy cập các tệp nguồn.

Các thành phần mật độ cao với các phần RF dễ dàng được đặt và định tuyến với bộ công cụ CAD đầy đủ trong Altium Designer®. Khi bạn đã hoàn thành thiết kế và muốn gửi các tệp cho nhà sản xuất, nền tảng Altium 365™ giúp bạn dễ dàng hợp tác và chia sẻ các dự án của mình.

Chúng tôi mới chỉ khám phá bề mặt của những gì có thể thực hiện với Altium Designer trên Altium 365. Bắt đầu dùng thử miễn phí Altium Designer + Altium 365 ngay hôm nay.