Wie Embedded-Design-Teams die I/O- und Routing-Vereinfachung umsetzen können

Jedes Mitglied eines Teams für das Design elektronischer Produkte kann konkrete Schritte unternehmen, um die Auswahl und Verlegung von I/O in Embedded-System-Designs zu vereinfachen.

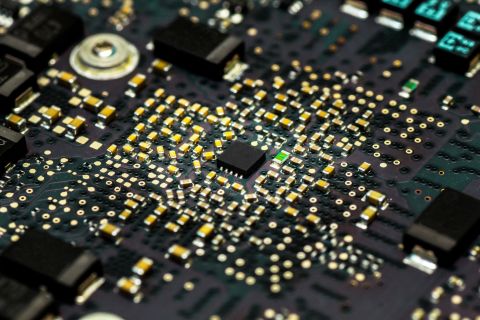

Reale elektronische Produkte werden langsam intelligenter, sowohl durch die Implementierung einer eingebetteten Anwendung als auch durch Verbindungen zurück zu einer Cloud-Plattform oder Anwendung. Eingebettete Entwicklungsteams müssen zusammenarbeiten, um diese neuen Generationen von Produkten zu erstellen. Ein Bereich, in dem der PCB-Layout-Ingenieur, der eingebettete Entwickler und sogar der MCAD-Ingenieur bei der Fertigstellung eines Projekts Verzögerungen erleben können, ist die Auswahl der I/O-Schnittstellen. Dies geschieht immer dann, wenn Sie Steckverbinder, Peripheriegeräte und einen Host-Prozessor haben.

Um also die Dinge für beide Seiten einfach zu halten, möchte ich einige meiner Erfahrungen teilen, die ich bei der Arbeit mit eingebetteten Entwicklern gemacht habe, um die Auswahl der I/O-Schnittstellen und den gesamten Prozess für die Fertigstellung des PCB-Layouts zu optimieren. Mit ein wenig Zusammenarbeit im Vorfeld können Sie das PCB-Routing und die eingebettete Entwicklung auf der Backend-Seite erleichtern.

Wer macht was in der eingebetteten Entwicklung?

Ich vertrete die Ansicht, dass jedes Mitglied des Entwicklungsteams verstehen sollte, was die anderen Teammitglieder benötigen, um erfolgreich zu sein. Dies betrifft auch den effizienten Einsatz von Ressourcen, das Vermeiden von technischen Sackgassen, die Tage zur Lösung benötigen, und das schnelle Erreichen des Marktes.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ich habe einen Stern (*) bei den Einträgen der Pinliste gesetzt, weil der genaue Prozess der Zuweisung von I/Os von der spezifischen Komponente abhängt, die verwendet wird, um die eingebettete Anwendung auszuführen. Handelt es sich um einen einfachen MCU, bei dem die verfügbaren I/Os an festen Stellen liegen, oder um einen FPGA, der in bestimmten Bänken eine angepasste Pinbelegung haben kann? Ein anderer Aspekt sind die Anschlüsse: Ist die Pinbelegung standardisiert, wird die Pinbelegung durch eine andere Platine in der Baugruppe festgelegt, oder kann sie angepasst werden?

Dies ist der Punkt, an dem wir die Herausforderung erkennen können, die darin besteht, dass ein PCB-Designer und ein Entwickler für eingebettete Systeme zusammenarbeiten, um die Auswahl der I/Os zu treffen. Wie können die beiden Seiten zusammenkommen und die Pinbelegungen, die Auswahl der I/Os und letztendlich das PCB-Layout festlegen?

Entwickler für eingebettete Systeme definiert PCB-Anforderungen

Meiner Meinung nach funktioniert dies am besten, wenn die Pinbelegung auf dem Hauptprozessor flexibel ist, d.h., die Anwendung wird in einem FPGA instanziiert. In diesem Fall können die I/Os vom Entwickler in der Gerätelogik festgelegt werden, und das Ergebnis ist, dass der PCB-Designer mit den ihm gegebenen Pinzuweisungen arbeiten muss.

Das Problem ist folgendes: Wenn Pin-Zuweisungen auf Basis einzelner Pins gegeben werden, erhält man möglicherweise keine optimale Verdrahtung, was zu einem Durcheinander von Verbindungen führt, die sich überkreuzen, um zu den Komponenten zu gelangen. Stattdessen, wenn der Embedded-Entwickler dem PCB-Designer lediglich Bank-Zuweisungen gibt, dann kann der PCB-Designer Pins innerhalb einer Bank wählen, um optimale Verbindungen herzustellen.

Durch die Zuweisung von Bänken auf einem FPGA anstelle einer spezifischen Pinbelegung kann der Designer ein Werkzeug wie Pin-Tausch verwenden, um I/O-Zuweisungen innerhalb einer Pin-Bank zu verschieben. Wenn ein Pin-Tausch wünschenswert ist, könnte ein benutzerdefiniertes Schaltsymbol erforderlich sein, um Pins ordnungsgemäß in ihre jeweiligen Bänke zu trennen. Die Verwendung eines benutzerdefinierten Symbols ermöglicht eine viel schnellere Gruppierung von Pins für Pin-Tausch-Operationen während der Verdrahtung des PCBs.

PCB-Designer definiert Embedded-Anforderungen

Meiner Meinung nach funktioniert dies am besten, wenn das Pinout auf dem Hauptprozessor festgelegt ist, d.h. bei einem MCU und seinen Peripheriegeräten. In einem MCU sind die I/O-Standorte im Grunde festgelegt. Man kann eine gewisse Flexibilität in Bezug darauf haben, wie jede I/O verwendet wird, zum Beispiel bei der Verwendung einer Bank von GPIOs. Allerdings können Pin- oder Funktionszuweisungen für Standard-Schnittstellen festgelegt sein (z.B. SPI, ADC-Pins, PWM-Pins, I2C usw.).

In diesem Fall denke ich, dass es am besten ist, wenn der PCB-Designer die Pins auswählt, die er verwenden wird, um sie mit verschiedenen Komponenten abzugleichen. Der PCB-Designer muss innerhalb eines festen Pinouts wählen, also muss er herausfinden, wie er die Komponenten so platzieren kann, dass das PCB-Layout lösbar ist. Einmal platziert und verdrahtet, ist es die Aufgabe des PCB-Designers, dem Embedded-Entwickler mitzuteilen, welche Pins für bestimmte Funktionen verwendet werden.

Was ist, wenn ein Steckverbinder-Pinout standardisiert ist?

Wenn das Pinout Ihres Steckverbinders standardisiert ist, dann ist das ein bisschen eine Wildcard. Ich sage das, weil „standardisiert“ zwei verschiedene Dinge bedeuten kann:

- Die Pinbelegung könnte Teil einer Standard-Schnittstelle sein (Ethernet, USB usw.)

- Die Pinbelegung könnte durch eine andere Platine in der Baugruppe oder im System festgelegt sein

Wenn keines von beiden zutrifft, dann ist Ihre Pinbelegung anpassbar. In Projekten, bei denen ich mit anderen Platinen in einer größeren Baugruppe gearbeitet habe, hatten wir oft die Freiheit, eine Pinbelegung festzulegen, meist weil wir beide Platinen gebaut haben. In jedem Fall müssen die beiden Seiten zusammenarbeiten, um eine objektiv „beste“ Pinbelegung für den Steckverbinder zu ermitteln und wie diese mit dem Prozessor übereinstimmt.

Teams, die an komplexen Produkten zusammenarbeiten müssen, können auf einen vollständigen Satz von Kollaborationsfunktionen für das Design zugreifen, wenn sie Altium Designer® verwenden. Alle an der Produktgestaltung beteiligten Stakeholder können auf einen vollständigen Satz von Werkzeugen für das PCB-Design zugreifen, die auch Aufgaben der eingebetteten Entwicklung unterstützen, sowie auf Funktionen für das Design von Kabeln und Leitungssätzen. Wenn Sie mit Ihrem Design fertig sind und Dateien an Ihren Hersteller freigeben möchten, macht die Plattform Altium 365™ die Zusammenarbeit und das Teilen Ihrer Projekte einfach.

Wir haben nur an der Oberfläche dessen gekratzt, was mit Altium Designer auf Altium 365 möglich ist. Starten Sie heute Ihre kostenlose Testversion von Altium Designer + Altium 365.