Comenzando con el MCU nRF52 en un PCB

Descubre cómo empezar con el nRF52 en un diseño de PCB. Te mostraremos cómo utilizar la versión del componente en paquete BGA de paso fino.

Haz clic aquí para saltar al visor incrustado y explorar este proyecto

La mayoría de los fabricantes de semiconductores han desarrollado y lanzado su propia línea de microcontroladores, y Nordic Semiconductor no es la excepción. Uno de sus productos más conocidos es el nRF52, un SoC con capacidad RF que incluye un transceptor integrado. Este componente es pequeño, ofrece un alto número de E/S y tiene un número de parte que viene en un paquete BGA de paso fino.

En este artículo, mostraré un ejemplo de diseño de PCB que utiliza la versión de paquete BGA de paso fino del nRF52. Al final del artículo, tendrás la oportunidad de descargar los archivos fuente de este proyecto. Sin más demora, comencemos con un ejemplo de diseño de PCB que incluye el nRF52.

Para los espectadores que quieran ver todo el proceso de diseño para este componente, hemos creado la siguiente lista de reproducción que guía a los usuarios a través del proceso de uso del nRF52 en un diseño de PCB. Específicamente, cubrimos cómo usar la versión de alta densidad (0.35 mm de distancia entre bolas) de este componente en un diseño que requiere algunas técnicas de diseño HDI. También mostraremos todo el viaje de ingeniería que nos llevó a la versión final de nuestro módulo nRF52.

Diseño Frontal

El nRF52 está disponible en varios paquetes con factores de forma pequeños. Este chip se ha popularizado como un microcontrolador capaz de manejar Bluetooth, con un conteo moderado de pines e interfaces digitales estándar, incluyendo la capacidad de usar USB en el dispositivo. El componente está dirigido a dispositivos embebidos pequeños con conectividad Bluetooth 5.

En este proyecto, el componente que utilizaremos es el nRF52840-CKAA-R7, un WLCSP de 93 pines con un footprint BGA. Este procesador es conocido por funcionar con bajo consumo de energía cuando no está transmitiendo, por lo que es posible usarlo con una batería pequeña. Añadiremos algo de regulación de batería y circuitos de protección de polaridad para este sistema, de modo que pueda funcionar exitosamente con energía de batería.

Footprint del nRF52840 WLCSP

El footprint para el nRF52840-CKAA-R7 se muestra a continuación. La barra de medida entre bolas muestra que el pitch es de 0.35 mm. Este es un pitch muy fino y requerirá algunas técnicas de diseño utilizadas en diseños HDI.

Otros Componentes Importantes

Entraremos en el pinout y fanout para este componente en una de las secciones siguientes. Por ahora, habrá varios otros componentes que aparecerán en el diseño:

- TPS70933DBVR - Regulador lineal de baja corriente

- FR015L3EZ - Protector de polaridad inversa de lado bajo

- BD33HC0MEFJ-ME2 - Regulador de 3V3/1A para circuitos lógicos

- PCF8523TK - Reloj en tiempo real (RTC) con interfaz I2C

- CAT24C512WI-GT3 - EEPROM de 512 KB

El dispositivo inicialmente necesitará conectarse a una batería LiPo a través de un conector estándar de 2 pines, y necesitaremos incluir al menos un encabezado para acceder a los I/Os y programar la placa. La cantidad de I/Os es mayor de lo que normalmente cabría en un solo encabezado, por lo que es una decisión si incluir un segundo encabezado solo para acceder a los I/Os. Por ahora, procederemos con el conector de la batería y un único encabezado de I/O, y siempre podemos agregar otro conector más tarde.

Comenzando: Esquemáticos

Los esquemáticos para este dispositivo no son demasiado complejos y todos los circuitos cabrán en una sola página. Mostraré diferentes regiones de los esquemáticos individualmente para que todo el diseño sea claro y fácil de leer.

Primero, veamos la sección de potencia. En este dispositivo, la potencia de 3V3 es proporcionada por un LDO de bajo ruido y baja corriente con una corriente nominal de salida de 150 mA. El LDO toma la potencia de la batería (VBAT) como entrada y convierte esto en la salida deseada de 3V3.

Basándonos en las conexiones de red para VBAT y VDD1, vemos que hay dos maneras de proporcionar energía a la placa:

- Aplicar 3V3 directamente a VDD1, como a través de un conector de pines

- Aplicar voltaje directamente a la red VBAT, también a través de uno de los conectores

En el primer caso, solo se encendería el MCU y el RTC; no habría energía para los periféricos. En el segundo caso, estarías proporcionando energía a todo el sistema, y ahora VDD1 sería una salida en lugar de una entrada.

Notarás que un segundo regulador está proporcionando energía de 3V3 para la red VDD2. Este regulador incluye un pin de habilitación, por lo que el dispositivo puede encenderse primero usando VDD1, y luego los periféricos (en este caso, la EEPROM) pueden ser alimentados usando VDD2. Esto le da al dispositivo la capacidad de apagar sus periféricos cuando no está en uso mediante el cambio del pin VDD2_ENABLE. Si tuviéramos otros periféricos que quisiéramos incluir en este diseño que no son centrales para el encendido del dispositivo, querríamos conectar estos a VDD2 en lugar de VDD1.

A continuación, veamos las conexiones del nRF52840. Estas fueron tomadas de la placa de desarrollo de Nordic y el conjunto original de conexiones en sus componentes se puede acceder en sus archivos de diseño de Altium.

Aquí he desglosado varias interfaces, y el circuito de soporte contiene principalmente cristales de referencia y algunos capacitores. Los capacitores varían desde un tamaño grande para desacoplamiento en masa, hasta un tamaño pequeño (0201) para el bypass en el rail VDD1. Todavía hay muchos pines disponibles en este componente, y estos podrían ser utilizados para otros periféricos. Eventualmente, desglosaré algunas de las I/Os adicionales y la interfaz SPI a un conector de pines como se muestra más adelante en la serie de videos.

Si echas un vistazo al pin E1, verás la conexión de la antena. Inicialmente, partiendo de los esquemáticos originales y el diseño de la disposición en el diseño de referencia, esta red de adaptación de impedancia utilizaba diferentes valores de capacitores de salida. La red de adaptación de impedancia mostrada a continuación se determinó mediante la ingeniería inversa de la impedancia de la antena con una calculadora en línea y modificando la red de adaptación para que sea simétrica. Cambiar el capacitor de salida de 0.8 pF en el diseño de referencia por el capacitor de salida de 1.2 pF mostrado a continuación produce esencialmente el mismo rendimiento.

Esto concluye esencialmente la parte de captura esquemática, y los circuitos restantes son simples de implementar. Ahora podemos pasar al diseño de la PCB.

Diseño de la PCB

Una vez en el diseño de la PCB, tenemos algunas tareas importantes que completar para usar el nRF52840 en WLCSP:

- Determinar un apilado y un despliegue de BGA

- Colocar la antena como un elemento impreso

- Colocar y enrutar los otros ICs para que no interfieran con la sección de RF

Apilado y Despliegue

El principal impulsor de la estrategia de apilamiento y distribución es el paso de bola en el paquete nRF52. Los lectores pueden notar arriba que el paso de bola es de 0.35 mm. El tamaño del pad en mi huella es de 0.212 mm, lo cual es un tamaño apropiado dado los estándares IPC sobre huellas BGA. La distancia diagonal a través de los pads es de 0.495 mm. Estas medidas se muestran a continuación.

Si intentáramos usar una distribución con fanout tipo hueso de perro con vías pasantes para enrutar hacia los pines internos, solo nos quedaría alrededor de 1-2 mils de espacio entre las vías y los pads vecinos. Esto es demasiado pequeño para que la mayoría de las casas de fabricación graben correctamente. También requeriría un tamaño de taladro muy pequeño de aproximadamente 4 mil con un pad de diámetro de 8 a 9 mil. Estos valores son simplemente demasiado pequeños para trabajar dentro de la fabricación estándar.

Por lo tanto, he utilizado un despliegue de vías en pad con vías ciegas y enterradas para alcanzar las capas internas. Dado que el tamaño del pad es de aproximadamente 8.3 mil, podemos usar vías ciegas/enterradas de 4 mil con pads de 8 mil. Para mantener una relación de aspecto de 1:2, necesitaríamos espesores de capa de 4 mil para nuestras capas exteriores con vías ciegas/enterradas. Esto daría un total de 6 capas como se muestra en el apilado a continuación.

Colocación de Componentes y Antena

Después de terminar el apilado y el despliegue, mi colocación inicial para esta placa se muestra a continuación. He incluido algunos polígonos para el enrutamiento de potencia antes de completar las conexiones restantes. La colocación inicial del encabezado de 6 pines se utilizó para la programación y la lectura de voltajes. El siguiente punto a considerar es la colocación de la antena, y finalmente, podemos concluir con las salidas de E/S hacia nuestros conectores.

En este diseño, utilizaremos una antena impresa para enviar y recibir señales inalámbricas. La mejor ubicación para colocar una antena impresa para el nRF52 está a lo largo del borde de la placa. Esto mantendrá la antena alejada de la sección digital. La antena se conecta al pin E1 en el nRF52840.

Si observas el diseño de referencia del nRF52, verás que proporcionan un ejemplo de antena impresa que puede incorporarse en otros diseños. Esta antena es una antena de cuarto de onda, y esto se puede verificar calculando la longitud de la antena y comparándola con la longitud de onda de la señal de 2.45 GHz en una configuración de microstrip sin tierra. La red de adaptación de impedancias mostrada en los esquemáticos arriba debería proporcionar una adaptación suficiente dadas las diferencias en el apilado para esta placa.

Encabezado de Programación SWD y Encabezado de E/S

Si decides producir esta placa, necesitarás programarla. La documentación del nRF52840 proporciona una guía para programar el dispositivo a través del protocolo SWDIO usando solo 4 pines:

- VDD (alimentación del sistema)

- SWDIO (J2)

- SWDCLK (H2)

- GND

Por lo tanto, he cambiado el encabezado de pines 1x6 por un encabezado SWD ya que este es un cable estándar utilizado para programar muchas placas de microcontroladores (también tengo algunos cables SWD en mi laboratorio). Note que el pin nReset (K6) es opcional para la programación, pero lo incluiré en el pinout del encabezado SWD junto con una conexión VBAT. El pinout finalizado en mi encabezado SWD se muestra a continuación.

El programador que prefiero usar para este tipo de dispositivo es el programador PRESTO, que está disponible en ASIX.net. Este programador soporta una larga lista de dispositivos, incluyendo el nRF52840 y algunos otros productos de Nordic. Tendrás que crear configuraciones de pines personalizadas para el cable en el PRESTO, pero esto es bastante sencillo de hacer con cables volantes.

Luego, decidí cambiar el encabezado inicialmente elegido de 1x6 por uno de 2x7 para poder sacar I/Os adicionales. El encabezado se colocó en la esquina superior izquierda de la placa. He añadido resistencias en serie de 22 Ohm en estos I/Os para ralentizar las señales que entran en la placa o salen de ella en caso de que la EMI se convierta en problemática en estos interconectores. Si resulta que no son necesarias, siempre puedo cambiarlas por resistencias de 0 Ohm.

Diseño Finalizado

El diseño finalizado del PCB se muestra en la imagen a continuación. He añadido algunos logotipos, establecido el número de parte en la parte inferior derecha de la placa y alineado las resistencias en las líneas de E/S a lo largo de la mitad inferior del conector de pines. También realicé una limpieza final en la serigrafía para que todos los designadores estén claros y no haya superposiciones. En este punto, el diseño ha pasado un DRC final y está listo para producirse.

Archivos Fuente y Revisiones Futuras

Aunque el enrutamiento podría mejorarse en algunos lugares solo para limpiar el acceso de E/S, la placa será funcional y estoy contento con el resultado. Algunas características adicionales que podrían añadirse incluyen un conector USB y un IC de gestión de carga USB para que el dispositivo pueda cargarse desde el bus estándar de 5V en un enchufe USB.

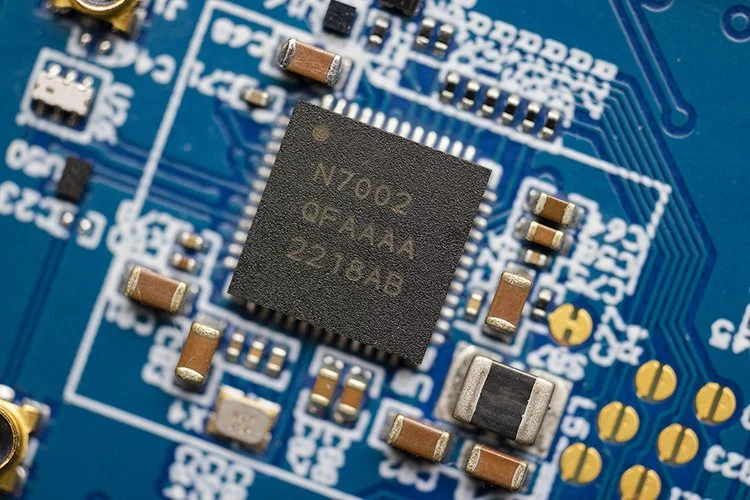

Otro componente que podría añadirse al diseño es un CI compañero de Nordic que proporciona acceso WiFi a los MCUs de la serie nRF52. El año pasado, en agosto de 2022, Nordic anunció el lanzamiento de su más reciente iteración de la serie nRF: el nRF7002. Este SoC ofrece soporte WiFi 6 de doble banda con un consumo de energía ultra bajo como compañero de los productos nRF52 o nRF53. Echaré un vistazo a este CI compañero en un proyecto y video próximos.

Por ahora, haz clic en este enlace para descargar un archivo ZIP con los archivos fuente del proyecto. También puedes usar el enlace de descarga en el embebido anterior para acceder a los archivos fuente.

Los componentes de alta densidad con secciones de RF son fáciles de colocar y trazar con el conjunto completo de utilidades CAD en Altium Designer®. Cuando hayas terminado tu diseño y quieras liberar los archivos a tu fabricante, la plataforma Altium 365™ facilita la colaboración y el compartir tus proyectos.

Solo hemos arañado la superficie de lo que es posible con Altium Designer en Altium 365. Comienza tu prueba gratuita de Altium Designer + Altium 365 hoy.