Einstieg in den nRF52 MCU auf einer Leiterplatte

Erfahren Sie, wie Sie mit dem nRF52 in einem PCB-Layout beginnen können. Wir zeigen, wie man die Version dieses Bauteils mit feinpoligem BGA-Gehäuse verwendet.

Klicken Sie hier, um zum eingebetteten Viewer zu springen und dieses Projekt zu durchsuchen

Die meisten Halbleiterhersteller haben ihre eigene Reihe von Mikrocontrollern entwickelt und auf den Markt gebracht, und Nordic Semiconductor bildet da keine Ausnahme. Eines ihrer bekanntesten Produkte ist der nRF52, ein RF-fähiger SoC mit integriertem Transceiver. Dieses Bauteil ist klein, bietet eine hohe Anzahl an I/Os und hat eine Teilenummer, die in einem Fine-Pitch-BGA-Gehäuse erhältlich ist.

In diesem Artikel werde ich ein PCB-Layout-Beispiel zeigen, das die Fine-Pitch-BGA-Paketversion des nRF52 verwendet. Am Ende des Artikels haben Sie die Möglichkeit, die Quelldateien für dieses Projekt herunterzuladen. Ohne weitere Verzögerung, lassen Sie uns mit einem Beispiel-PCB-Layout beginnen, das den nRF52 beinhaltet.

Für Zuschauer, die den gesamten Designprozess für dieses Bauteil verfolgen möchten, haben wir die folgende Playlist erstellt, die Benutzer durch den Prozess der Verwendung des nRF52 in einem PCB-Layout führt. Insbesondere behandeln wir, wie man die hochdichte (0,35 mm Ballabstand) Version dieses Bauteils in einem Design verwendet, das einige HDI-Design-Techniken erfordert. Wir werden auch die gesamte Ingenieurreise zeigen, die uns zur endgültigen Version unseres nRF52-Moduls geführt hat.

Front-End-Design

Der nRF52 ist in einigen verschiedenen Gehäusen mit kleinen Formfaktoren erhältlich. Dieser Chip ist als Bluetooth-fähiger Mikrocontroller mit moderater Pinanzahl und standardmäßigen digitalen Schnittstellen, einschließlich der Fähigkeit, USB im Gerät zu nutzen, beliebt geworden. Die Komponente zielt auf kleine eingebettete Geräte mit Bluetooth 5-Konnektivität ab.

In diesem Projekt werden wir die Komponente nRF52840-CKAA-R7 verwenden, ein 93-Pin-WLCSP mit einem BGA-Fußabdruck. Dieser Prozessor ist dafür bekannt, bei Nichtsendung mit geringer Leistung zu laufen, sodass es möglich ist, ihn mit einer kleinen Batterie zu verwenden. Wir werden einige Schaltungen für Batterieregelung und Polaritätsschutz für dieses System hinzufügen, damit es erfolgreich mit Batterieleistung betrieben werden kann.

nRF52840 WLCSP-Fußabdruck

Der Fußabdruck für den nRF52840-CKAA-R7 ist unten dargestellt. Die Messleiste zwischen den Bällen zeigt, dass der Pitch 0,35 mm beträgt. Dies ist ein sehr feiner Pitch und wird einige in HDI-Designs verwendete Entwurfstechniken erfordern.

Weitere wichtige Komponenten

Wir werden uns in einem der folgenden Abschnitte mit dem Pinout und dem Fanout für diese Komponente befassen. Für jetzt gibt es mehrere andere Komponenten, die im Design erscheinen werden:

- TPS70933DBVR - Niedrigstrom-Linearegler

- FR015L3EZ - Schutz gegen Verpolung für die Niedrigseite

- BD33HC0MEFJ-ME2 - 3V3/1A Regler für Logikschaltungen

- PCF8523TK - Echtzeituhr (RTC) mit I2C-Schnittstelle

- CAT24C512WI-GT3 - 512 KB EEPROM

Das Gerät muss zunächst über einen standardmäßigen 2-poligen Stecker an einen LiPo-Akku angeschlossen werden, und wir müssen mindestens einen Header vorsehen, um auf die I/Os zugreifen und das Board programmieren zu können. Die Anzahl der I/Os ist größer, als wir normalerweise auf einen einzelnen Header passen würden, daher ist es eine Ermessensfrage, ob wir nur für den Zugriff auf die I/Os einen zweiten Header hinzufügen sollen. Für den Moment werden wir mit dem Akkuanschluss und einem einzelnen I/O-Header fortfahren, und wir können später immer noch einen weiteren Anschluss hinzufügen.

Erste Schritte: Schaltpläne

Die Schaltpläne für dieses Gerät sind nicht allzu komplex und alle Schaltkreise passen auf eine einzige Seite. Ich werde verschiedene Bereiche der Schaltpläne einzeln zeigen, damit das gesamte Design klar und leicht zu lesen ist.

Zuerst werfen wir einen Blick auf den Leistungsbereich. In diesem Gerät wird die 3V3-Leistung durch einen rauscharmen, stromsparenden LDO mit einem Nennstromausgang von 150 mA bereitgestellt. Der LDO nimmt die Batterieleistung (VBAT) als Eingang und wandelt diese in den gewünschten 3V3-Ausgang um.

Basierend auf den Netzverbindungen für VBAT und VDD1 sehen wir, dass es zwei Möglichkeiten gibt, die Platine mit Strom zu versorgen:

- 3V3 direkt an VDD1 anlegen, beispielsweise über eine Stiftleiste

- Spannung direkt an das VBAT-Netz anlegen, ebenfalls über einen der Anschlüsse

Im ersteren Fall würden Sie nur den MCU und RTC mit Strom versorgen; es gäbe keine Leistung für die Peripheriegeräte. Im letzteren Fall würden Sie das gesamte System mit Strom versorgen, und nun wäre VDD1 ein Ausgang und nicht mehr ein Eingang.

Sie werden bemerken, dass ein zweiter Regler 3V3-Strom für das Netz VDD2 bereitstellt. Dieser Regler umfasst einen Enable-Pin, sodass das Gerät zunächst mit VDD1 hochfahren kann und dann die Peripheriegeräte (in diesem Fall das EEPROM) mit VDD2 eingeschaltet werden können. Dies gibt dem Gerät die Fähigkeit, seine Peripheriegeräte abzuschalten, wenn das Gerät nicht in Gebrauch ist, indem der VDD2_ENABLE-Pin umgeschaltet wird. Wenn wir irgendwelche anderen Peripheriegeräte hätten, die wir in dieses Design einbeziehen möchten, die aber nicht zentral für das Einschalten des Geräts sind, würden wir diese an VDD2 statt an VDD1 anschließen.

Als Nächstes werfen wir einen Blick auf die Verbindungen des nRF52840. Diese wurden vom Nordic-Entwicklungsboard übernommen, und der ursprüngliche Satz von Verbindungen auf ihren Komponenten kann in ihren Altium-Design-Dateien eingesehen werden.

Hier habe ich mehrere Schnittstellen herausgearbeitet, und die unterstützende Schaltung enthält hauptsächlich Referenzkristalle und einige Kondensatoren. Die Kondensatoren reichen von einem großen Gehäuse für die Bulk-Entkopplung bis hin zu einem kleinen Gehäuse (0201) für das Bypassing auf der VDD1-Schiene. In dieser Komponente sind immer noch viele Pins übrig, die für andere Peripheriegeräte verwendet werden könnten. Ich werde schließlich einige der zusätzlichen I/Os und die SPI-Schnittstelle, wie später in der Videoserie gezeigt, auf eine Stiftleiste herausführen.

Wenn Sie sich Pin E1 ansehen, werden Sie die Antennenverbindung erkennen. Ursprünglich, ausgehend von den originalen Schaltplänen und Layouts im Referenzdesign, verwendete dieses Impedanzanpassungsnetzwerk unterschiedliche Werte für die Ausgangskondensatoren. Das unten gezeigte Impedanzanpassungsnetzwerk wurde durch Reverse Engineering der Antennenimpedanz mit einem Online-Rechner bestimmt und das Anpassungsnetzwerk so modifiziert, dass es symmetrisch ist. Der Austausch des 0,8 pF Ausgangskondensators im Referenzdesign durch den unten gezeigten 1,2 pF Ausgangskondensator führt im Wesentlichen zur gleichen Leistung.

Damit ist der Teil der Schaltungserfassung im Wesentlichen abgeschlossen, und die verbleibenden Schaltkreise sind einfach zu implementieren. Wir können nun mit dem PCB-Layout fortfahren.

PCB-Layout

Einmal im PCB-Layout, haben wir einige wichtige Aufgaben zu erledigen, um den nRF52840 in WLCSP zu verwenden:

- Eine Stack-Up- und BGA-Fanout-Bestimmung

- Platzierung der Antenne als gedrucktes Element

- Platzierung und Verlegung der anderen ICs, sodass sie den HF-Bereich nicht stören

Stack-Up und Fanout

Der Haupttreiber der Stack-Up- und Fanout-Strategie ist der Ballabstand auf dem nRF52-Paket. Leser mögen oben bemerken, dass der Ballabstand 0,35 mm beträgt. Die Padgröße in meinem Footprint beträgt 0,212 mm, was angesichts der IPC-Standards für BGA-Footprints eine angemessene Größe ist. Der diagonale Abstand über die Pads beträgt 0,495 mm. Diese Messungen sind unten dargestellt.

Wenn wir versuchen würden, Dogbone-Fanout mit Durchgangsbohrungen zu verwenden, um zu den inneren Pins zu routen, blieben uns nur etwa 1-2 mils Platz zwischen den Vias und den benachbarten Pads. Das ist zu klein für die meisten Fertigungshäuser, um ordnungsgemäß zu ätzen. Es würde auch eine sehr kleine Bohrgröße von etwa 4 mil mit einem 8 bis 9 mil Durchmesser Pad erfordern. Diese Werte sind einfach zu klein, um innerhalb der Standardfertigung zu arbeiten.

Daher habe ich ein via-in-pad Fanout mit blinden und vergrabenen Vias verwendet, um die inneren Lagen zu erreichen. Da die Pad-Größe etwa 8,3 mil beträgt, können wir 4 mil blinde/vergrabene Vias mit 8 mil Pads verwenden. Um ein Aspektverhältnis von 1:2 zu halten, würden wir eine Schichtdicke von 4 mil für unsere äußeren Lagen mit blinden/vergrabenen Vias benötigen. Dies würde insgesamt 6 Lagen ergeben, wie im folgenden Stackup gezeigt.

Komponenten- und Antennenplatzierung

Nachdem der Stackup und das Fanout fertiggestellt wurden, ist meine anfängliche Platzierung für dieses Board unten gezeigt. Ich habe einige Polygone für das Power-Routing hinzugefügt, bevor ich die restlichen Verbindungen vervollständige. Die anfängliche Platzierung des 6-Pin-Headers wurde für die Programmierung und das Lesen von Spannungen verwendet. Der nächste Punkt, der zu berücksichtigen ist, ist die Platzierung der Antenne, und schließlich können wir mit den I/O-Breakouts in unsere Anschlüsse abschließen.

In diesem Design werden wir eine gedruckte Antenne verwenden, um drahtlose Signale zu senden und zu empfangen. Der beste Ort, um eine gedruckte Antenne für den nRF52 zu platzieren, ist am Rand des Boards. Dies wird die Antenne aus dem Weg des digitalen Abschnitts halten. Die Antenne verbindet sich mit Pin E1 am nRF52840.

Wenn Sie sich das nRF52-Referenzdesign ansehen, werden Sie feststellen, dass sie ein Beispiel für eine gedruckte Antenne bereitstellen, das in andere Designs integriert werden kann. Diese Antenne ist eine Viertelwellenantenne, und dies kann überprüft werden, indem man die Länge der Antenne berechnet und mit der Wellenlänge des 2,45 GHz Signals in einer grundlosen Mikrostreifenkonfiguration vergleicht. Das in den Schaltplänen oben gezeigte Impedanzanpassungsnetzwerk sollte eine ausreichende Anpassung bieten, angesichts der Unterschiede im Stackup für dieses Board.

SWD-Programmierkopf und I/O-Kopf

Wenn Sie sich entscheiden, dieses Board zu produzieren, müssen Sie es programmieren. Die nRF52840-Dokumentation bietet eine Anleitung zur Programmierung des Geräts über das SWDIO-Protokoll mit nur 4 Pins:

- VDD (Systemstrom)

- SWDIO (J2)

- SWDCLK (H2)

- GND

Daher habe ich den 1x6-Pin-Header gegen einen SWD-Header ausgetauscht, da dies ein Standardkabel ist, das zur Programmierung vieler Mikrocontroller-Boards verwendet wird (ich habe auch einige SWD-Kabel in meinem Labor). Beachten Sie, dass der nReset-Pin (K6) für die Programmierung optional ist, aber ich werde ihn im SWD-Header-Pinout zusammen mit einer VBAT-Verbindung einschließen. Das fertige Pinout auf meinem SWD-Header ist unten dargestellt.

Der Programmierer, den ich für diese Art von Gerät bevorzuge, ist der PRESTO Programmierer, der von ASIX.net erhältlich ist. Dieser Programmierer unterstützt eine lange Liste von Geräten, einschließlich des nRF52840 und einiger anderer Produkte von Nordic. Sie müssen benutzerdefinierte Pinbelegungen für das Kabel am PRESTO erstellen, aber das ist mit Flugleitungen einfach genug zu bewerkstelligen.

Als Nächstes entschied ich mich, den ursprünglich gewählten 1x6-Header gegen einen 2x7-Header auszutauschen, damit ich zusätzliche I/Os herausführen konnte. Der Header wurde in der oberen linken Ecke der Platine platziert. Ich habe 22-Ohm-Serienwiderstände an diesen I/Os hinzugefügt, um die Signale, die auf die Platine kommen oder sie verlassen, im Falle von EMI-Problemen in diesen Verbindungen zu verlangsamen. Falls sich herausstellt, dass diese nicht benötigt werden, kann ich sie immer gegen 0-Ohm-Widerstände austauschen.

Finalisiertes Layout

Das fertiggestellte PCB-Layout ist im Bild unten dargestellt. Ich habe einige Logos hinzugefügt, die Teilenummer im unteren rechten Bereich der Platine platziert und die Widerstände an den I/O-Leitungen entlang der unteren Hälfte des Stiftleistenheaders ausgerichtet. Außerdem habe ich eine abschließende Bereinigung auf dem Siebdruck vorgenommen, sodass alle Bezeichner klar sind und es keine Überlappungen gibt. An diesem Punkt hat das Design eine finale DRC-Prüfung bestanden und es ist bereit zur Produktion.

Quelldateien und zukünftige Revisionen

Obwohl die Verdrahtung an einigen Stellen verbessert werden könnte, um den Zugang zu den I/Os zu vereinfachen, wird die Platine funktionsfähig sein und ich bin zufrieden mit dem Ergebnis. Einige zusätzliche Funktionen, die hinzugefügt werden könnten, umfassen einen USB-Anschluss und einen USB-Ladeverwaltungs-IC, sodass das Gerät über den standardmäßigen 5V-Bus eines USB-Steckers geladen werden könnte.

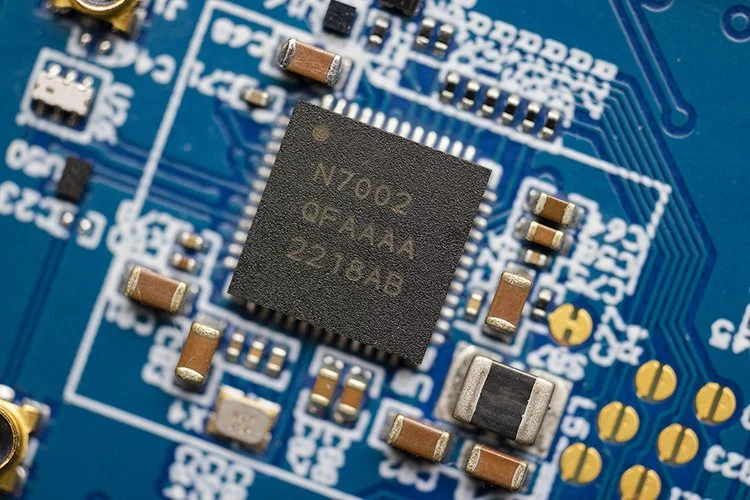

Ein weiteres Bauteil, das dem Design hinzugefügt werden könnte, ist ein Nordic-Begleit-IC, das den nRF52-Serien-MCUs WiFi-Zugang bietet. Letztes Jahr, im August 2022, kündigte Nordic die Veröffentlichung seiner neuesten Iteration der nRF-Serie an: den nRF7002. Dieser SoC bietet Dual-Band-WiFi-6-Unterstützung mit extrem niedrigem Energieverbrauch als Begleiter für die nRF52- oder nRF53-Produkte. Ich werde mir diesen Begleit-IC in einem kommenden Projekt und Video genauer ansehen.

Vorerst, klicken Sie auf diesen Link, um ein ZIP-Archiv mit den Projektquellendateien herunterzuladen. Sie können auch den Download-Link im obigen Einbettungsbereich nutzen, um auf die Quellendateien zuzugreifen.

Hochdichte Komponenten mit RF-Abschnitten lassen sich mit dem kompletten Satz an CAD-Werkzeugen in Altium Designer® leicht platzieren und verdrahten. Wenn Sie Ihr Design abgeschlossen haben und Dateien an Ihren Hersteller freigeben möchten, erleichtert die Plattform Altium 365™ die Zusammenarbeit und das Teilen Ihrer Projekte.

Wir haben nur an der Oberfläche dessen gekratzt, was mit Altium Designer auf Altium 365 möglich ist. Beginnen Sie noch heute Ihre kostenlose Testversion von Altium Designer + Altium 365.