Interfaz de memoria DDR con FPGAs AMD/Xilinx

Aprende cómo interconectar memoria DDR con FPGAs de AMD/Xilinx.

Introducción

Interfazar memoria volátil DDR a FPGA sin experiencia previa puede parecer bastante desalentador inicialmente. A pesar de la flexibilidad inherente de un FPGA, donde podríamos asumir que podemos conectar los I/O de la memoria DDR externa en cualquier lugar a cualquier pin libre, todavía necesitamos considerar muchas restricciones.

Por ejemplo, dónde colocar ciertos grupos de pines de memoria DDR, qué voltajes utilizar en los bancos, qué relojes necesitamos y dónde conectarlos, cómo evitar violaciones de tiempo, y así sucesivamente.

Además de la interfaz a nivel de esquemático, también debemos preocuparnos por la interfaz en el mundo real en la placa de circuito impreso, como suministros y entrega de energía, desacoplamiento, terminación, impedancia y longitud de traza, coincidencia de retrasos, y más.

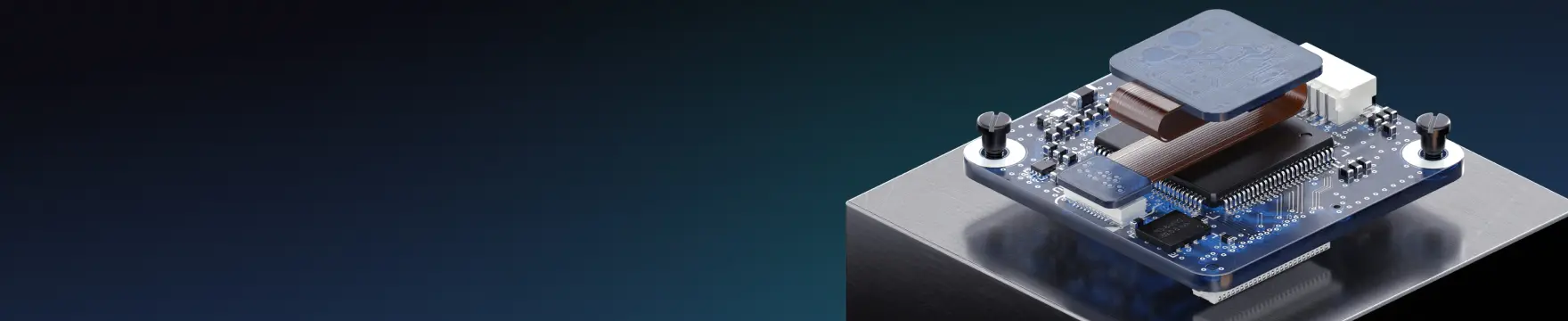

Este artículo examinará la interfaz de memoria DDR con FPGAs desde un punto de vista a nivel de sistema y esquemático. Como un ejemplo práctico, veremos un diseño de DSP de audio basado en AMD/Xilinx Spartan-7 (llamado ‘Xerxes’), que se interfaza con alguna memoria DDR2.

Hardware de DSP de audio Xerxes (FPGA AMD/Xilinx Spartan-7 con memoria DDR2)

Tipo de Memoria

El tipo de memoria que usamos depende del diseño. Depende de nuestras necesidades de capacidad de memoria y ancho de banda de memoria, así como de lo que nuestro FPGA elegido sea capaz de hacer.

En términos generales, la mayoría de los FPGAs modernos pueden interfazarse con memoria DDR2 y DDR3 (y sus variantes de bajo poder y bajo voltaje). Por supuesto, la memoria DDR4 más rápida y superior también es posible, pero usualmente solo para FPGAs más avanzados.

No solo es importante la tasa de datos máxima posible, sino también los requisitos de voltaje y energía, tipo de paquete, costo y disponibilidad. Todo esto necesita ser considerado temprano en la etapa de diseño.

Comparación de Memoria DDR (Fuente: synopsys.com)

Al elegir nuestro tipo de memoria, también necesitamos estar atentos a la calificación de velocidad del dispositivo de memoria y la calificación de velocidad del controlador de memoria dentro del FPGA. Podemos optar por ‘derating’ nuestra memoria o controlador, así no funcionando a todo el ancho de banda, lo que a su vez nos da más margen de tiempo.

Tabla Típica de Derating de Memoria (Fuente: AMD/Xilinx UG933)

Específicamente para FPGAs de AMD/Xilinx, sugeriría descargar su IDE Vivado y experimentar con el IP gratuito Memory Interface Generator (MIG).

Esto te mostrará rápidamente qué tipos de memoria, grados de velocidad y partes compatibles puedes usar.

Ejemplo de partes de memoria compatibles con Vivado MIG

Te podrías preguntar, ¿por qué elegí memoria DDR2 para la placa Xerxes?

Aunque es un estándar bastante antiguo, usar memoria DDR2 significó que podía usar el regulador de 1.8V ya disponible en la placa (esto alimenta otras partes del FPGA) y no tuve que agregar otro regulador separado.

Además, el diseño de Xerxes no tiene requisitos particularmente altos de ancho de banda de memoria, y por lo tanto, una interfaz DDR2 fue suficiente.

Además, tener una interfaz de menor ancho de banda facilita el PCB, la terminación y las restricciones de tiempo.

Memoria DDR e Interfaz FPGA

Después de haber elegido un dispositivo de memoria adecuado, es hora de conectar esto al FPGA en tu esquemático.

Primero, necesitamos elegir un banco adecuado. Si estás usando una interfaz de datos de 16 bits de ancho (o menos), para la mayoría de los FPGA esto generalmente puede caber en un banco. Si no, necesitamos dividir la interfaz de memoria en varios bancos.

Por simplicidad, optaremos por una interfaz de memoria de 16 bits de ancho, como es el caso de la placa Xerxes. Elige un banco libre que pueda funcionar con el mismo voltaje que la memoria DDR misma (en el caso de Xerxes, este es el banco 34 a 1.8V debido al uso de memoria DDR2).

Banco FPGA 34 con desacoplamiento apropiado funcionando desde el suministro de 1.8V

Para los FPGA de AMD/Xilinx, usando las herramientas Vivado y MIG, obtener el pin-out para nuestra memoria DDR es muy sencillo. La herramienta sugiere un pin-out adecuado para ese banco, o podemos asignar pines manualmente y verificar el pin-out.

Herramienta de Pin-Out de Vivado MIG

Si configuras manualmente el pin-out, asegúrate de que las líneas de bytes DDR individuales tengan el mismo número de byte de banco y que los strobes diferenciales estén en los pines DQS capaces de FPGA diferenciales.

Recuerda que el pin-out probablemente se ajustará durante la etapa de diseño y enrutamiento del PCB. Gracias a la flexibilidad del FPGA, intercambiar pines durante el proceso de diseño del PCB puede simplificar el enrutamiento y minimizar las transiciones de capa.

Para este ejemplo, como estamos funcionando desde un solo banco, debemos usar el VREF interno, limitando el ancho de banda máximo de la memoria.

Además, necesitamos estar atentos al reloj. Idealmente, la fuente del reloj debería estar en el mismo banco conectado a un pin (o pines si se usa una fuente de reloj diferencial) capaz de reloj.

Finalmente, asegúrate de utilizar las herramientas de los proveedores para verificar el diseño y el tiempo. Luego, con el diseño inicial de los pines en su lugar, en tu esquemático, define clases de red, pares diferenciales y reglas, y usa codificación de colores para facilitar tu vida en el diseño de PCBs.

Conexiones DDR2 y fuente de reloj del banco 34 de FPGA

Para un solo dispositivo, simplemente necesitamos hacer conexiones punto a punto en el componente de memoria DDR.

La terminación debe estar presente en las señales de dirección/comando/control (ACC); sin embargo, para tasas de datos más bajas, a menudo podemos prescindir de esto. Siempre agrego terminación en el par de reloj diferencial. Las líneas de datos de byte están terminadas internamente en ambos extremos.

Se recomienda colocar resistencias de pull-down de 4.7k en las líneas CKE, ODT y, opcionalmente, en las líneas CS#.

Conexiones de señal y alimentación del módulo de memoria DDR2

Finalmente, el módulo de memoria necesita ser alimentado, por supuesto. En el caso de la placa Xerxes, el módulo DDR2 está conectado al mismo regulador de 1.8V que nuestro banco de FPGA 34. Se requiere un desacoplamiento adecuado: como regla general, si no se especifica lo contrario en hojas de datos o notas de aplicación, se debe apuntar a usar un pequeño capacitor (~100nF) por cada dos pines VDD y un capacitor de mayor tamaño por cada diez pines VDD.

El voltaje del pin VREF se puede generar mediante un divisor de potencial simple con un capacitor de filtrado, como se muestra en la imagen anterior.

Conclusión

En este artículo, hemos delineado las estrategias básicas para incorporar memoria DDR no volátil externa en nuestros diseños basados en FPGA desde un punto de vista a nivel de sistema y esquemático.

Recuerda que estos son los conceptos básicos absolutos, y dependiendo de los requisitos de tu sistema, el diseño será mucho más complejo. Especialmente, si planeas usar partes de memoria e interfaces más rápidas, y múltiples módulos.

Cuando diseñes sistemas avanzados basados en FPGA y DDR, asegúrate de utilizar las herramientas y características contenidas en herramientas ECAD de clase mundial como Altium Designer. Asegúrate de obtener tu prueba gratuita de Altium Designer y Altium 365 aquí.