Proyecto Pi.MX8 - Diseño de Placa Parte 3

Capítulos

Board Layout Part 3

| Created: June 24, 2024PCB Assembly

| Coming soon¡Bienvenidos a una nueva entrega del proyecto del módulo de computadora de código abierto Pi.MX8! En esta serie, profundizamos en el diseño y las pruebas de un sistema en módulo basado en un procesador i.MX8M plus de NXP.

En la actualización anterior, completamos los preparativos del diseño. Esto incluyó la creación de los perfiles de impedancia, añadiendo las reglas de diseño según las especificaciones del fabricante de la placa y definiendo áreas donde deberían aplicarse reglas de diseño especiales. También hemos terminado de enrutar la interfaz LPDDR4 pero sin ajuste de longitud (por ahora).

Antes de comenzar con el ajuste de longitud de la interfaz DRAM, echaremos un vistazo al enrutamiento de las demás interfaces en el módulo Pi.MX8. Hay bastantes buses de alta y baja velocidad en la placa, algunos de los cuales son buses paralelos anchos que ocupan mucho espacio de enrutamiento. Para asignar suficiente espacio a cada interfaz, primero crearemos un plan de distribución aproximado para cada capa de enrutamiento en el módulo.

Planificación del enrutamiento

El plan de enrutamiento nos ayudará a determinar cómo distribuir todas las interfaces de alta y baja velocidad a través de las capas de señales disponibles. Al establecer una guía aproximada con anticipación, podemos asegurarnos de tener suficiente espacio de enrutamiento disponible en la capa en la que estamos trabajando actualmente. Esto también nos ayuda a minimizar las transiciones de capa y reducir la cantidad de retoques a realizar durante el proceso de enrutamiento.

Hay varias formas de configurar la planificación del diseño, principalmente dependiendo de las herramientas disponibles. Solo necesitamos una herramienta de dibujo básica que nos permita esbozar sobre una imagen existente. En este ejemplo, utilizaremos Inkscape.

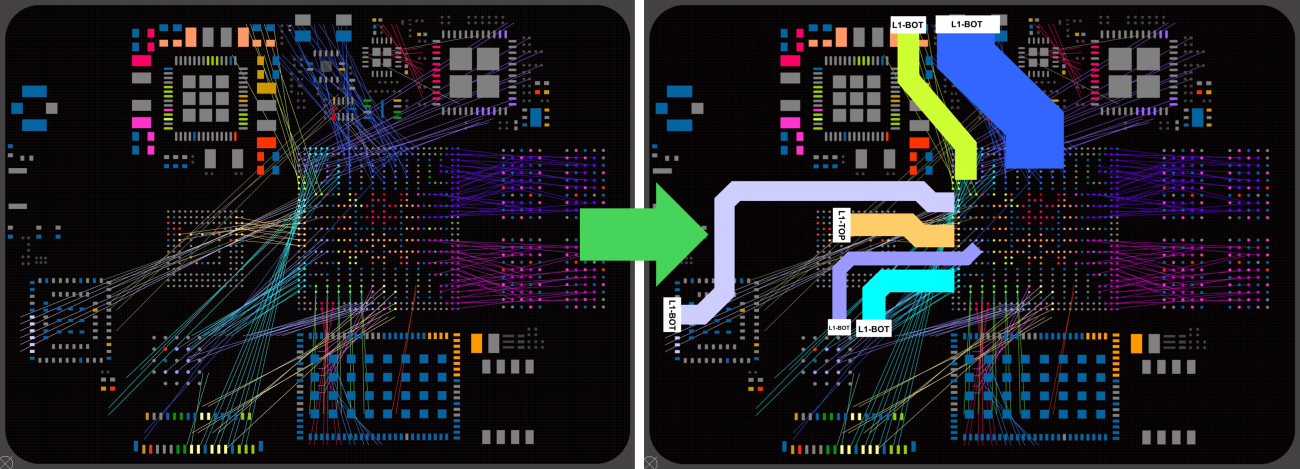

En Inkscape, podemos agregar una imagen de fondo que muestra la colocación de los componentes y las interfaces no enrutadas en forma de airwires de colores. Note que las redes de alimentación están ocultas en esta captura de pantalla, ya que solo nos centraremos en las redes que se enrutaran en las capas de señal. En el esquemático, hemos colocado una directiva de clase de red en cada red de alimentación, lo que facilita identificar qué redes se enrutaran en las capas de plano simplemente habilitando o ocultando la clase de red asociada en el editor de diseño.

Para el enrutamiento real, simplemente añadimos líneas en Inkscape para representar las interfaces que queremos enrutar en la capa correspondiente. Podemos ajustar el ancho de estas líneas para representar cuántas señales serán enrutadas en la interfaz. El color de la línea se puede elegir de la imagen de fondo para facilitar la identificación de qué interfaz se está representando.

Dado que las transiciones entre capas también necesitan espacio asignado en todas las capas, podemos añadir un bloque al final de cada línea detallando la transición de capa.

Planificación de diseño en Inkscape con una captura de pantalla de Altium Designer como imagen de fondo

Una vez que hemos repetido el proceso anterior para cada capa de enrutamiento, podemos proceder y comenzar con el proceso de enrutamiento real.

Enrutamiento de la capa superior

Con una estrategia de enrutamiento en su lugar, comencemos por enrutamiento las interfaces en la capa superior. Dado que ya hemos realizado el enrutamiento de fanout para los componentes en la capa superior, podemos usar todo el espacio restante para el enrutamiento de señales. No queda mucho espacio, pero lo que tenemos todavía puede utilizarse para facilitar el enrutamiento en las capas de señal internas colocando estratégicamente VIAs en regiones que no interferirán con el enrutamiento en las capas internas más adelante. Este es otro beneficio de planificar un diseño con anticipación, de lo contrario, estas regiones no estarían definidas en esta etapa.

Enrutamiento de la capa superior del módulo PiMX8

Cuando colocamos trazas en la capa superior, también deberíamos considerar que necesitamos algo de espacio para agregar características como fiduciales o etiquetas en la capa superior. Los códigos de matriz de datos grabados con láser también pueden requerir ya sea un área de cobre sólido o un área sin trazas para proporcionar un contraste homogéneo, lo que significa que estas áreas no pueden utilizarse para el enrutamiento.

Enrutamiento de Capa de Señal Interna

La mayoría de las conexiones se colocarán en las dos capas internas de señal que hemos definido en el administrador de pila de capas. Comencemos por enrutar todas las interfaces síncronas de alta velocidad. En nuestro caso, estas podrían ser las interfaces MIPI-CSI, MIPI-DSI y LVDS. Todas estas interfaces utilizan señalización diferencial de bajo voltaje y llevan una línea de reloj dedicada y al menos dos líneas de datos. Requieren mucho espacio de enrutamiento porque la longitud de cada línea de datos debe coincidir con la línea de reloj dentro de un cierto margen de tiempo. Hacer coincidir la longitud de varios pares diferenciales puede requerir mucho espacio, ya que es muy probable que uno o más pares dentro de la interfaz introduzcan un retraso significativo que debe tenerse en cuenta. Al enrutar estas interfaces primero, podemos asegurarnos de que habrá suficiente espacio disponible para la sintonización de longitud más tarde.

Colocar vías de retorno cerca de las transiciones de capa de estos pares diferenciales de alta velocidad también es importante para garantizar la integridad de la señal. Las vías de retorno pueden ocupar espacio en múltiples capas, por lo que estas vías deben colocarse tan pronto como se realice una transición de señal.

A continuación, podemos enrutar las otras interfaces de alta velocidad como PCIe, USB, HDMI y Ethernet. Estas interfaces tienen requisitos menos estrictos para el emparejamiento de longitud entre pares, por lo que no necesitamos dedicar tanto espacio al emparejamiento de longitud. Sin embargo, una gestión sólida del camino de retorno y enfoques básicos de diseño de alta velocidad en estas señales sigue siendo muy importante, aunque colocándolas en segundo lugar en la lista de prioridades de enrutamiento.

Por último, pero no menos importante, podemos enrutar las interfaces de menor velocidad restantes como SDIO, GPIO, RGMII y otros buses misceláneos como UART o I2C y SPI. Estas interfaces todavía operan a tasas de transición alta, lo que significa que todavía necesitamos tratarlas como señales de alta velocidad.

Enrutamiento de la capa de señal interna 1

Enrutamiento de la capa de señal interna 2

Enrutamiento de la capa inferior

En el caso de la placa PiMX8, podemos tratar la capa inferior como una capa de enrutamiento interna en términos de espacio disponible. La mayoría de los componentes activos están colocados en la capa superior del módulo, dejando solo algunos reguladores de voltaje y componentes pasivos como condensadores de desacoplamiento y resistencias de configuración en la capa inferior.

La prioridad de enrutamiento en la capa inferior es la misma que para las capas internas, por lo que comenzaremos con las interfaces MIPI-CSI, MIPI-DSI y LVDS. En el módulo PiMX8, un multiplexor de alta velocidad puede seleccionar entre los puertos DSI y LVDS. Este componente se coloca en la capa inferior cerca del conector de placa a placa. Debido al diseño de pines del multiplexor, hay un retraso significativo en una de las líneas de señal conectadas al mux. Tendremos que examinar esto más detenidamente durante el proceso de coincidencia de longitud, pero necesitamos reservar algo de espacio en la capa inferior para permitir un mayor retraso.

Disposición de pines del multiplexor con una línea larga en la interfaz

Enrutamiento de la capa inferior módulo PiMX8

Hay algunos escenarios en el módulo PiMX8 que requieren atención especial durante la sintonización de retrasos. Haremos uso extensivo de señales X para superar algunos de estos desafíos. Qué son exactamente estos desafíos, y cómo podemos implementar señales X para proporcionar una sintonización de retraso precisa sobre un componente compartido por múltiples interfaces, será parte de la próxima actualización. ¡Manténganse al tanto!