Projektowanie sprzętu w warunkach niedoboru pamięci: praktyczny przewodnik dla inżynierów i zespołów zakupowych

W pierwszej części tej serii, How AI Broke the Memory Market, przyjrzeliśmy się temu, jak popyt ze strony centrów danych AI uczynił pamięć wąskim gardłem i dlaczego ceny DRAM i NAND raczej nie wrócą szybko do normy. Teraz przyjrzymy się temu, jak działać w takim otoczeniu. Jeśli projektujesz sprzęt lub odpowiadasz za jego pozyskiwanie w 2026 roku, nadal musisz podejmować decyzje: jakie komponenty uwzględnić w specyfikacji, jak zaprojektować rozwiązania z myślą o elastyczności oraz jak zarządzać ryzykiem w łańcuchu dostaw.

Omówimy komponenty pamięci „następnej fali”, które są już w przygotowaniu, a następnie przejdziemy do sprawdzonych układów DRAM i pamięci flash. Potem przedstawimy praktyczne zestawy działań zarówno dla inżynierii, jak i zakupów.

Aby szerzej zapoznać się z komponentami pamięci, strony kategorii Octopart dotyczące układów pamięci i pamięci flash są dobrym punktem wyjścia do wyszukiwania według producentów, obudów i dostępności.

Najważniejsze wnioski

- Wiedz, co nadchodzi, a co jest dostępne już teraz. Komponenty nowej generacji, takie jak LPDDR6 i HBM4, pokazują kierunek rozwoju platform, ale Twoje projekty z 2026 roku będą trafiać na rynek z DDR5, LPDDR5X i dojrzałą pamięcią NAND, która jest dziś dostępna z magazynu.

- Projektuj z myślą o zamiennikach i elastyczności. Standaryzuj interfejsy głównego nurtu, kwalifikuj rodziny komponentów i obsługuj wiele pojemności w firmware. Tam, gdzie to możliwe, stosuj gniazda i moduły oraz planuj warianty pamięci o obniżonych parametrach, które nadal spełniają wymagania dotyczące UX.

- Traktuj ryzyko dostaw jak problem inżynierski. Buduj wieloźródłowe listy zatwierdzonych dostawców (AVL), zabezpieczaj przydziały dla krytycznych linii i śledź cykl życia oraz zamienniki za pomocą narzędzi takich jak Octopart.

Komponenty nowej fali wyznaczające kierunek

Mobilna pamięć DRAM LPDDR6 firmy Samsung

Zaprojektowana z myślą o AI działającej na urządzeniu, motoryzacji oraz platformach mobilnych i PC nowej generacji, Samsung’s LPDDR6 zapewnia istotny wzrost efektywności względem LPDDR5X, rozszerzoną architekturę I/O oraz początkową szybkość do 10,7 Gb/s, przy czym standard LPDDR6 został zaprojektowany tak, aby dalej się skalować wraz z dojrzewaniem ekosystemu. LPDDR6 nie zobaczysz jeszcze na półkach dystrybutorów, ale jeśli projektujesz w oparciu o wiodące SoC lub urządzenia flagowe, powinieneś spodziewać się kontaktu z tym standardem.

HBM4

Na szczycie stosu 16-warstwowe układy HBM4 o pojemności 48 GB firmy SK Hynix obiecują przepustowość przekraczającą 2 TB/s, a produkcja masowa planowana jest na okolice III kwartału 2026 roku. Samsung przyjmuje inne podejście, wykorzystując logikę 4 nm i DRAM 1c w celu poprawy parametrów termicznych. Inżynierowie pracujący nad sprzętem AI zwykle nie będą pozyskiwać tych układów od dystrybutorów katalogowych, ale HBM4 ma znaczenie dla wszystkich, ponieważ pochłania dużą część zaawansowanych mocy produkcyjnych DRAM, co jest jednym z powodów, dla których konwencjonalny DRAM pozostaje trudno dostępny.

10. generacja V-NAND firmy Samsung

Dzięki ponad 400 warstwom i interfejsowi 5,6 GT/s 10. generacja V-NAND firmy Samsung jest przeznaczona do dysków SSD PCIe 5.0 i przyszłych PCIe 6.0 dla centrów danych oraz obciążeń klasy AI. Można oczekiwać, że pamięć TLC o wysokiej gęstości oparta na tym krzemie będzie stanowić podstawę wielu dysków klasy enterprise i wysokowydajnych dysków klienckich w ciągu najbliższych kilku lat.

NAND BiCS10 firmy Kioxia/Sandisk

Ta 332-warstwowa pamięć BiCS10 z interfejsem Toggle DDR 6.0 zapewnia 4,8 Gb/s na pin i jest kierowana do zastosowań AI oraz pamięci masowej hyperscale. Według EE Times Kioxia poinformowała, że cała jej produkcja NAND na 2026 rok została już sprzedana do zastosowań związanych z AI, a zwiększanie produkcji BiCS10 przyspieszono z drugiej połowy 2027 roku na 2026 rok, aby sprostać popytowi.

Mniej ograniczone, sprawdzone produkty pamięciowe

Te komponenty były dostępne do zamówienia u głównych dystrybutorów na początku marca 2026 roku. Dostępność zmienia się szybko, dlatego przed zatwierdzeniem BOM sprawdź stan magazynowy i status cyklu życia w Octopart .

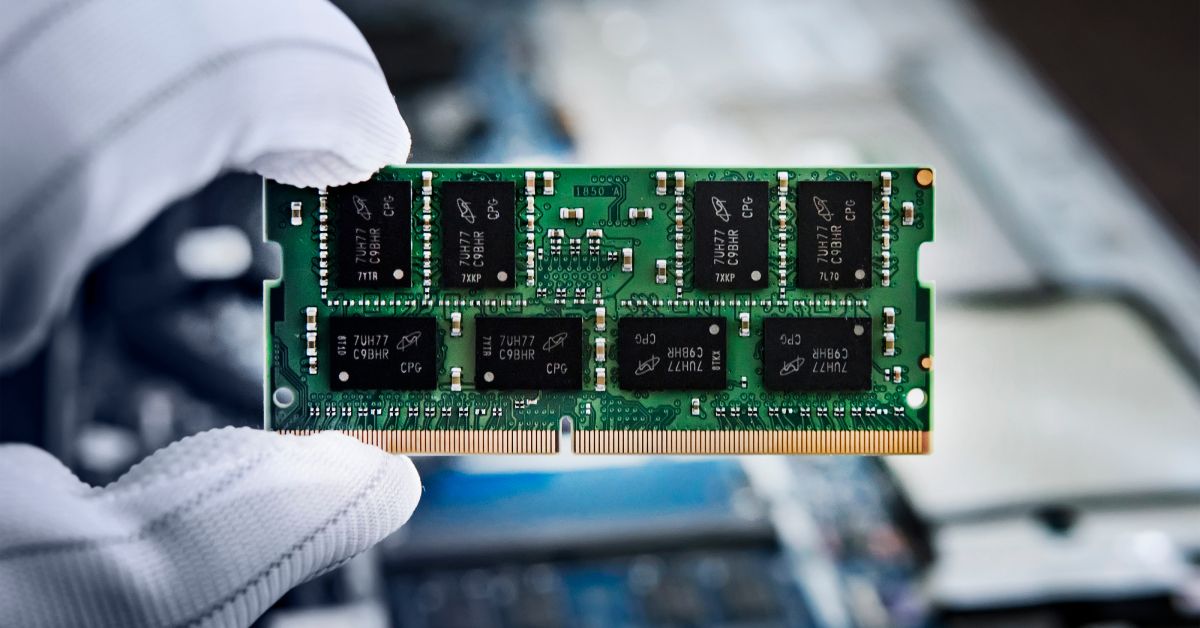

- Apacer D22.31491S.001, 8 GB DDR5-4800 SO-DIMM. Praktyczna opcja DRAM typu „late-bind” dla projektów, które mogą korzystać z modułu w gnieździe, co daje działowi zakupów większą swobodę przy stosowaniu zamienników.

- MT60B2G8RZ-56B IT:D, 16 Gbit DDR5 SDRAM (2G x 8), 78-ball VFBGA. Popularny układ DRAM DDR5 klasy x8 / DDR5-5600, odpowiedni do niestandardowych projektów pamięci na poziomie płytki i zapewniający bardziej praktyczną elastyczność w zakresie drugiego źródła niż pojedynczy, unikalny SKU modułu.

- Macronix MX30LF4G28AD-XKI-TR, 4 Gbit SLC NAND (VFBGA-63). Dobrze nadaje się do przemysłowych i wbudowanych projektów NAND, które wymagają trwałości i przewidywalnego działania w kompaktowej obudowie BGA.

- Macronix MX60LF8G28AD-TI-T, 8 Gbit SLC NAND (TSOP-48). Praktyczny wybór, gdy potrzebujesz szeroko wspieranego równoległego formatu NAND dla dojrzałych ekosystemów kontrolerów oraz łatwiejszych przeróbek płytki niż w przypadku BGA o drobnym rastrze.

- Macronix MX52LM04A11XSI, 4 GB eMMC 5.1 (BGA-153). Prosta opcja zarządzanej pamięci NAND, gdy chcesz ograniczyć zależności od kontrolera i uzyskać łatwiejszą zamienność niż w przypadku surowej pamięci NAND plus niestandardowego stosu flash.

- Macronix MX52LM08A11XVW, 8 GB eMMC 5.1 (BGA-153). Praktyczny poziom pojemności dla wielu systemów embedded Linux i urządzeń klasy HMI, z tymi samymi zaletami interfejsu i integracji co mniejsze układy eMMC.

- Micron MT40A2G8SA-062E:F, 16 Gbit DDR4 DRAM (2G x 8). Nadal jest to wysokowolumenowy, sprawdzony komponent dla wielu platform i pragmatyczna opcja „ship-now”, gdy DDR5 nie jest wymagane.

Zestaw działań projektowych: jak inżynierowie budują elastyczność

W takich realiach inżynierowie sprzętu nadal mogą podjąć wiele działań, aby zwiększyć odporność projektów.

- Standaryzuj interfejsy i rodziny komponentów głównego nurtu. DDR5, LPDDR5X, e.MMC, UFS oraz pamięci flash SPI/QSPI mają rozbudowane ekosystemy i wielu dostawców drugiego źródła. Pozostawanie przy typowych napięciach i obudowach maksymalizuje pulę kompatybilnych komponentów.

- Wbuduj elastyczność w firmware i mapy pamięci. Unikaj sztywnego zakodowania jednej pojemności DRAM lub jednego rozmiaru pamięci SPI flash. Obsługuj wiele geometrii w kodzie inicjalizacji, aby można było podmieniać zamienniki.

- Preferuj zarządzaną pamięć nieulotną tam, gdzie ma to sens. e.MMC i UFS ukrywają szczegóły zarządzania NAND za stabilnymi interfejsami i często oferują bardziej przejrzyste ścieżki zamienności niż surowa pamięć NAND powiązana z konkretnym kontrolerem.

- Planuj warianty o obniżonych parametrach. Projektuj oprogramowanie tak, aby konfiguracje z mniejszą ilością pamięci nadal zapewniały akceptowalne doświadczenie użytkownika, na przykład dzięki niższej domyślnej współbieżności, mniejszym zestawom zasobów lub warstwowaniu funkcji.

- Stosuj modułową pamięć i pamięć masową tam, gdzie to możliwe. Gniazda dla SO-DIMM, UDIMM i dysków SSD M.2 umożliwiają późny dobór konfiguracji i dają działowi zakupów większą swobodę. Pamięć lutowaną na stałe rezerwuj dla ograniczonych formatów, gdzie jest rzeczywiście konieczna.

Zestaw działań zakupowych: jak procurement może zarządzać ryzykiem

Sytuacja wymaga uwagi. Pod koniec lutego 2026 roku Lenovo ostrzegło partnerów kanałowych, aby składali zamówienia przed końcem miesiąca, by uniknąć marcowych podwyżek cen, podczas gdy TrendForce prognozował, że łączna cena PC DRAM (DDR4/DDR5) wzrośnie w samym I kwartale o 105–110% kwartał do kwartału. Poniższy zestaw działań odzwierciedla tę nową rzeczywistość.

- Zabezpieczaj przydziały i umowy długoterminowe dla krytycznych linii DRAM i NAND, szczególnie dla serwerów, urządzeń AI i notebooków z wyższej półki. Dane rynkowe od firm takich jak TrendForce mogą pomóc określić właściwy moment na zobowiązania zakupowe.

- Buduj listy zatwierdzonych dostawców wokół rodzin komponentów, a nie pojedynczych SKU. Zdefiniuj akceptowalne klasy modułów, NAND i e.MMC oraz współpracuj z inżynierami, aby z wyprzedzeniem zweryfikować kilka opcji.

- Segmentuj produkty według wrażliwości na pamięć. Kieruj rzadką i drogą pamięć do SKU, w których ma ona największy wpływ na wydajność i marżę; wobec urządzeń mniej wrażliwych na pamięć stosuj bardziej agresywną kontrolę kosztów.

- Wykorzystuj zapasy pamięci jako strategiczne zabezpieczenie dla produktów o długim cyklu życia. Utrzymywanie bufora kluczowych układów DRAM lub NAND może być tańsze niż przeprojektowywanie płytek lub przepisywanie firmware w połowie cyklu życia produktu, jeśli dany komponent stanie się trudno dostępny.

Elastyczność jest strategią

W pierwszej części tej serii omówiliśmy przyczyny kryzysu na rynku pamięci. Tutaj natomiast skupiliśmy się na tym, co robić teraz. Odpowiedź jest taka sama niezależnie od tego, czy jesteś inżynierem, czy pracujesz po stronie zakupów: najlepszym zabezpieczeniem jest elastyczność. Projektuj z myślą o zamiennikach, kwalifikuj szeroko i korzystaj z narzędzi takich jak Octopart, aby mieć swoje opcje stale widoczne i aktualne. Z tego cyklu w najlepszej kondycji wyjdą te zespoły, które wcześnie zbudowały opcjonalność w swoich projektach i łańcuchach dostaw oraz nadal dostosowują się do zmian podaży i cen.

Często zadawane pytania

Dlaczego DRAM i NAND nadal są trudne do pozyskania w 2026 roku?

Obecne niedobory wynikają z alokacji mocy produkcyjnych wafli, a nie z ograniczeń technologicznych. Dostawcy pamięci priorytetowo traktują wysokomarżowy popyt związany z AI, zwłaszcza HBM i DRAM dla centrów danych, realizowany w ramach wieloletnich kontraktów. Ponieważ HBM zużywa znacznie większą część mocy produkcyjnych wafli na bit niż konwencjonalny DRAM, mniej mocy pozostaje dla DDR5, LPDDR i NAND, co utrzymuje napiętą dostępność.

Czy inżynierowie powinni już dziś projektować z wykorzystaniem pamięci nowej generacji, takich jak LPDDR6 lub HBM4?

LPDDR6 i HBM4 pokazują kierunek rozwoju platform, ale większość produktów z 2026 roku będzie trafiać na rynek z DDR5, LPDDR5X i dojrzałą pamięcią NAND, która jest dostępna już teraz. Inżynierowie powinni projektować z myślą o przyszłej kompatybilności, jednocześnie wybierając komponenty, które można niezawodnie pozyskiwać w trakcie produkcji, zamiast stawiać na części, które nie są jeszcze dostępne w dystrybucji.

Jak można zwiększyć odporność projektów sprzętowych na niedobory pamięci?

Odporne projekty koncentrują się na elastyczności i zamienności. Obejmuje to standaryzację popularnych interfejsów, kwalifikację wielu pojemności i dostawców, unikanie sztywno zakodowanych założeń dotyczących pamięci w firmware oraz stosowanie gniazd lub modułów tam, gdzie to możliwe. Obsługa wariantów pamięci o obniżonych parametrach zapewnia, że produkty nadal mogą być dostarczane, gdy komponenty o większej pojemności są trudno dostępne.

Jaki jest najlepszy sposób, aby zespoły zakupowe mogły zarządzać ryzykiem dostaw pamięci?

Dział zakupów powinien traktować pamięć jako zasób strategiczny, a nie towar masowy. Do najlepszych praktyk należą: zabezpieczanie długoterminowych przydziałów dla krytycznych SKU, budowanie AVL w oparciu o rodziny komponentów zamiast pojedynczych części, monitorowanie cyklu życia i zamienników za pomocą narzędzi takich jak Octopart oraz selektywne utrzymywanie zapasów dla produktów o długim cyklu życia, aby uniknąć wymuszonych przeprojektowań.