Jak AI rozbiła rynek pamięci: kulisy kryzysu DRAM i NAND w latach 2024–2026

Najważniejsze wnioski

- Centra danych AI stały się głównym odbiorcą pamięci półprzewodnikowych, wymuszając zmiany w alokacji wafli jednocześnie między DRAM, HBM i NAND.

- Ten cykl podaży i popytu jest inny. Ograniczona rozbudowa fabryk, w dużej mierze wyprzedana produkcja NAND oraz wieloletnie kontrakty na HBM oznaczają, że niedobór prawdopodobnie utrzyma się do końca lat 2027–2028.

- Starsze i wbudowane projekty stają się ofiarami ubocznymi. DDR3, wczesne DDR4 i SLC NAND są narażone na rosnące ryzyko EOL, dłuższe terminy realizacji i nieprzewidywalne ceny, ponieważ dostawcy priorytetowo traktują wysokomarżowe pamięci dla AI.

Zwrot akcji na rynku pamięci: z elementu drugoplanowego do wąskiego gardła

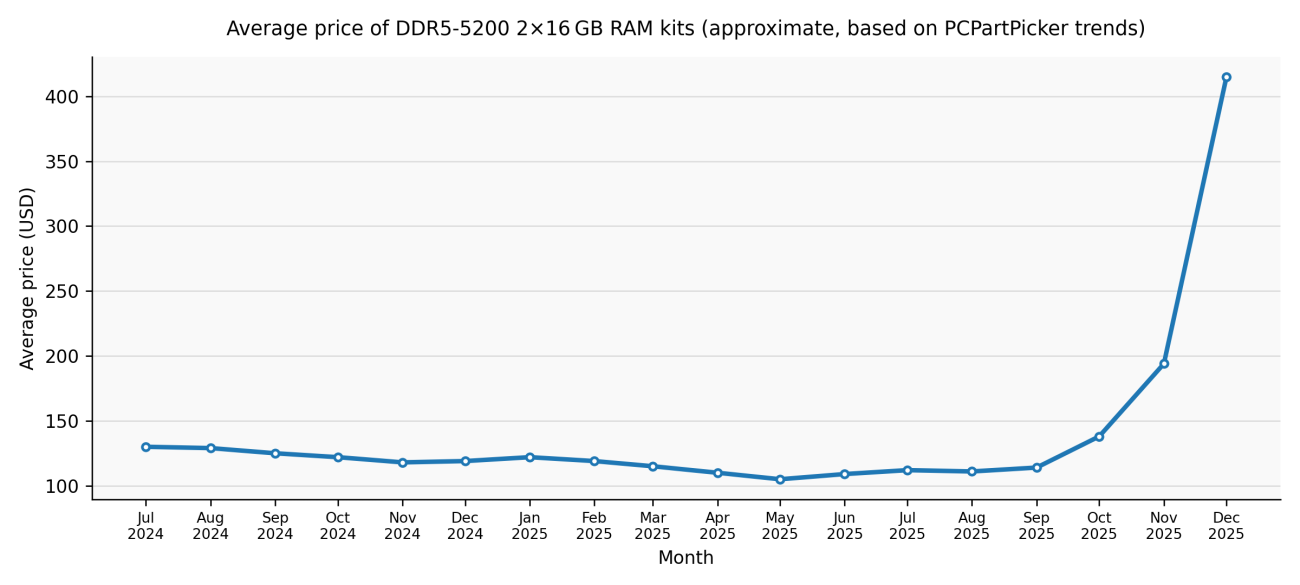

Przez większość ery PC pamięć pozostawała w tle. W latach 2024–2026 ta dynamika się odwróciła. Pamięć stała się głównym ograniczeniem w projektowaniu systemów, a koszt „po prostu dodania większej ilości RAM-u” gwałtownie wzrósł w ciągu zaledwie kilku kwartałów.

Ceny wzrosły, dostępność się pogorszyła, a produkty są coraz częściej dostarczane z absolutnym minimum pamięci zamiast z wygodnym zapasem, do którego byliśmy przyzwyczajeni. Trwa strukturalne przetasowanie dotyczące tego, kto otrzymuje wafle i dlaczego.

Co więc właściwie się zmieniło i dlaczego ten niedobór wydaje się inny niż poprzednie? Wyjaśniamy to tutaj, w pierwszej części dwuczęściowej serii opisującej siły zakłócające podaż pamięci — od serwerów chmurowych po systemy wbudowane. Część druga, Projektowanie sprzętu w warunkach niedoboru pamięci, rozwija ten temat, oferując szczegółowe omówienie komponentów pamięci nowej generacji, które właśnie trafiają na rynek, wiodących produktów roboczych, które można dziś zamówić u dystrybutora, wzorców projektowych oraz taktyk zakupowych.

Jak centra danych AI przekształcają krajobraz popytu

W poprzednich cyklach popyt na pamięć był szeroko rozłożony między komputery PC, telefony, serwery i elektronikę użytkową. Podaż i popyt traciły synchronizację, ceny rosły lub spadały, a potem sytuacja się normalizowała, gdy fabryki dostosowywały produkcję. Niedobór z lat 2024–2026 nie przebiega według tego scenariusza.

Różnica polega na tym, kto kupuje. Centra danych skoncentrowane na AI dominują dziś po stronie popytu, a ich klastry treningowe i farmy inferencyjne potrzebują ogromnych ilości pamięci o wysokiej przepustowości (HBM) oraz konwencjonalnej pamięci DRAM na każdy GPU lub akcelerator. HBM zużywa znacząco większą pojemność wafli na bit niż standardowy DRAM, co czyni ją wyjątkowo atrakcyjną dla producentów chcących zabezpieczyć wieloletnie, wysokomarżowe kontrakty z dostawcami infrastruktury AI.

Niektórzy analitycy szacują obecnie, że centra danych zużyją nawet 70% wszystkich wysokowydajnych układów pamięci wyprodukowanych w 2026 roku, co stanowi wyraźne odwrócenie sytuacji z czasów, gdy większość takich układów trafiała do urządzeń konsumenckich. W takim otoczeniu pamięć do PC i urządzeń mobilnych staje się działalnością poboczną, a centra danych AI — głównym polem gry.

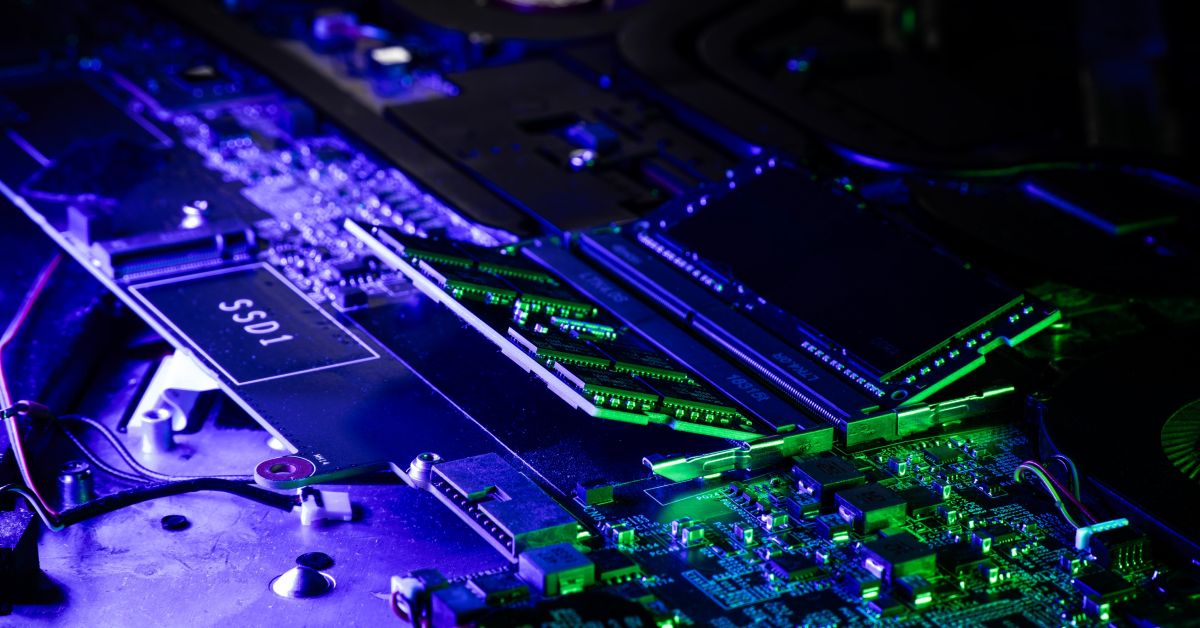

Generacja HBM4 zaprezentowana na CES 2026 pokazuje skalę tej zmiany. SK Hynix pokazał 16-warstwowy układ o pojemności 48 GB, zapewniający ponad 2 TB/s, co znacząco zwiększa wydajność względem wczesnych pamięci HBM3 stosowanych w pierwszej fali akceleratorów gen-AI. Każdy wafer przeznaczony na takie stosy nie produkuje DDR5 do kolejnego PC ani LPDDR5X do telefonu.

Systemy wbudowane i starsze projekty: ściskane z boku

Projekty wbudowane i przemysłowe, które często opierają się na starszych standardach DRAM lub dojrzałych pamięciach SLC NAND, również mierzą się z własnymi przeciwnościami. Wiele z tych produktów wykorzystuje DDR3 lub wczesne układy DDR4, a także równoległą pamięć flash NAND, które nie znajdują się już w centrum planów rozwojowych dostawców.

Gdy producenci nadają priorytet wysokomarżowym HBM i serwerowym odmianom DRAM, ograniczają lub wycofują starsze linie. To, co pozostaje, osiąga nieoczekiwanie wysokie ceny i dłuższe terminy realizacji, mimo że sama technologia jest dojrzała.

Ścisłe monitorowanie statusu cyklu życia komponentów za pomocą narzędzi takich jak Octopart pomaga zespołom wychwycić zapowiedzi EOL i pogarszającą się dostępność, zanim staną się sytuacją kryzysową.

Postęp pod presją: DDR5, LPDDR6, NAND i HBM4

Te same zmiany technologiczne, które odcinają starsze projekty od podaży, przynoszą też rzeczywiste przełomy inżynierskie. Zrozumienie obu stron tej dynamiki jest istotne, ponieważ postęp zmienia to, co jest dostępne do projektowania, podczas gdy stojąca za nim ekonomia wafli wyjaśnia, dlaczego pamięć masowa nie stanieje w najbliższym czasie.

DRAM

Samsung produkuje masowo najcieńszą pamięć LPDDR5X DRAM w klasie 12 nm dla urządzeń mobilnych nowej generacji, łącząc wysoką wydajność z efektywnością energetyczną i cienką obudową odpowiednią dla telefonów klasy premium oraz ultraprzenośnych urządzeń. Wczesne układy LPDDR6 jeszcze bardziej zwiększają przepustowość i efektywność energetyczną, celując w AI na urządzeniu oraz zastosowania motoryzacyjne. Implementacja LPDDR6 firmy Samsung zyskuje uznanie na wydarzeniach branżowych, sygnalizując kierunek rozwoju pamięci mobilnej z wyższej półki.

HBM

Na drugim końcu spektrum, jeśli chodzi o HBM, materiały z CES 2026 dotyczące HBM4 pokazują, że stosy pamięci stają się wysoce zintegrowanymi podsystemami. 16-warstwowe stosy SK Hynix wykorzystują MR-MUF i ultracienkie wafle DRAM, aby zmieścić się w limitach wysokości JEDEC, podczas gdy Samsung patrzy w stronę swojej logiki 4 nm (której produkcja masowa rozpoczęła się w lutym 2026 roku), aby poprawić parametry termiczne i efektywność energetyczną. Cały ten wysiłek inżynieryjny i cała ta pojemność wafli są jednoznacznie ukierunkowane na akceleratory AI.

NAND

Po stronie NAND dostawcy układają coraz więcej warstw. V-NAND 10. generacji z ponad 400 warstwami i interfejsami rzędu 5,6 GT/s jest projektowany do dysków SSD PCIe 5.0 i przyszłych PCIe 6.0 dla centrów danych i zastosowań AI. 332-warstwowa pamięć BiCS NAND 10. generacji firmy Kioxia i Sandisk, wykorzystująca interfejs Toggle DDR 6.0 z szybkością do 4,8 Gb/s na pin, pokazuje, jak daleko zaszły pamięci NAND o wysokiej przepustowości dla dysków SSD klasy data center i enterprise.

Technologia rozwija się, ale moce produkcyjne nie nadążają. Według EE Times Samsung i SK Hynix ograniczyły produkcję wafli NAND w latach 2024–2025, koncentrując się na HBM i DRAM, i nie ogłosiły nowej mocy produkcyjnej NAND, mimo że kontrolują ponad połowę rynku. Dane Omdia pokazują spadek liczby wafli NAND Samsunga z 4,9 mln (2024) do 4,68 mln (2025), a SK Hynix z 1,9 mln do 1,7 mln.

Jednocześnie NAND stał się kluczowy dla inferencji AI. W miarę jak AI przechodzi od treningu do obsługi modeli, dyski SSD oparte na pamięciach NAND o dużej liczbie warstw coraz częściej stają się głównym magazynem wag modeli i danych roboczych. Kierownictwo Kioxia stwierdziło, że cała produkcja NAND na 2026 rok jest już wyprzedana, że BiCS10 zostaje przyspieszone z drugiej połowy 2027 roku na 2026 rok oraz że w przyszłości niemal połowa popytu na ich NAND może pochodzić z zastosowań AI. Specjaliści od NAND, tacy jak Kioxia i nowo usamodzielniony biznes Sandisk, wcześniej postrzegani jako gracze drugiego planu na skomodytyzowanym rynku, nagle znajdują się w gronie beneficjentów boomu na SSD dla AI.

Dlaczego typowe odbicie nie nadejdzie

Analitycy branżowi wskazują na relatywnie umiarkowany wzrost podaży DRAM i NAND do 2026 roku w porównaniu z historycznymi normami. Tymczasem popyt nie słabnie. Nowe architektury modeli, obciążenia inferencyjne i wdrożenia edge AI stale zwiększają wymagania pamięciowe, zamiast pozwolić im się ustabilizować. Dostawcy HBM4 przeznaczają znaczną część pojemności wafli na potrzeby akceleratorów Nvidii i innych producentów, a jak wspomnieliśmy w poprzedniej sekcji, dostawcy NAND, tacy jak Kioxia, mają już wyprzedaną produkcję na 2026 rok.

W grudniu 2025 roku Micron pokazał strukturalny charakter tej zmiany, ogłaszając wyjście z konsumenckiego biznesu Crucial, aby lepiej obsługiwać „większych, strategicznych klientów”. Niektórzy dostawcy, w tym Micron, publicznie stwierdzili, że nie spodziewają się istotnej poprawy niedoboru RAM dla konsumentów przed około 2028 rokiem, kiedy nowa moc produkcyjna i zmiany procesowe mają osiągnąć pełną skalę. Ta sama logika coraz częściej dotyczy NAND: inferencja AI blokuje przyszłą podaż klasy SSD tak szybko, jak dostawcy są w stanie ją uruchamiać.

W grudniu 2025 roku IDC określiło ten niedobór jako „nie tylko cykliczny niedobór, ale potencjalnie trwałą, strategiczną realokację światowej zdolności produkcyjnej wafli krzemowych”. W lutym 2026 roku TrendForce gwałtownie podniosło prognozę cen kontraktowych konwencjonalnego DRAM na I kwartał 2026 roku — z wcześniejszego szacunku 55–60% do 90–95% kwartał do kwartału. W tym ujęciu przewidywano, że DRAM do PC (mieszanka DDR4/DDR5) wzrośnie o 105–110% kwartał do kwartału, ustanawiając nowy kwartalny rekord.

Co dalej: od zrozumienia do działania

W Projektowaniu sprzętu w warunkach niedoboru pamięci przyglądamy się siedmiu komponentom pamięci nowej fali, które trafiają do projektów OEM i centrów danych, ośmiu sprawdzonym produktom DRAM i flash łatwo dostępnym u głównych dystrybutorów oraz konkretnym scenariuszom działania w tych ograniczeniach.

Często zadawane pytania

Dlaczego występuje niedobór pamięci, skoro technologia DRAM i NAND stale się poprawia?

Obecny niedobór nie wynika z ograniczeń technologicznych, lecz z ekonomii alokacji wafli. Coraz większa część globalnych mocy produkcyjnych wafli pamięci jest przekierowywana na wysokomarżowe pamięci dla AI, zwłaszcza HBM dla akceleratorów w centrach danych. Ponieważ HBM zużywa znacząco większą powierzchnię wafla na użyteczny bit niż konwencjonalny DRAM, każdy wafer przeznaczony na produkcję HBM zmniejsza produkcję DDR4, DDR5, LPDDR i NAND. Przy ograniczonej rozbudowie fabryk i długoterminowych kontraktach AI blokujących moce produkcyjne poprawa gęstości pamięci nie przekłada się na większą dostępność dla rynków masowych ani systemów wbudowanych.

Dlaczego ten niedobór pamięci wydaje się inny niż w poprzednich cyklach?

W przeciwieństwie do wcześniejszych cykli boom–spadek, obecny niedobór wynika ze strukturalnej koncentracji popytu, a nie z tymczasowej nadkonsumpcji. Obciążenia związane z treningiem i inferencją AI nadal zwiększają wymagania pamięciowe, podczas gdy dostawcy celowo ograniczają wzrost mocy produkcyjnych. Wieloletnie kontrakty na HBM, wyprzedana produkcja NAND na 2026 rok oraz jednoznaczne komunikaty dostawców wskazujące na poprawę dopiero po latach 2027–2028 oznaczają, że mamy do czynienia z długotrwałą realokacją, a nie krótkoterminową nierównowagą, która skoryguje się sama wyłącznie poprzez ceny.

Jakie ryzyka stwarza to dla projektów wbudowanych i starszych konstrukcji wykorzystujących DDR3, wczesne DDR4 lub SLC NAND?

Produkty pamięci starszej generacji są coraz częściej traktowane przez głównych dostawców jako niestanowiące strategicznego priorytetu. Ponieważ producenci koncentrują się na zaawansowanych pamięciach DRAM i HBM, starsze węzły procesowe mierzą się z malejącymi seriami produkcyjnymi, rosnącymi minimalnymi wielkościami zamówień, dłuższymi terminami realizacji oraz wyższym ryzykiem wycofania z produkcji (EOL). Nawet gdy komponenty formalnie nadal „pozostają w produkcji”, ceny stają się niestabilne, a dostępność nieprzewidywalna. Dla zespołów projektujących systemy wbudowane oznacza to większe znaczenie monitorowania cyklu życia komponentów, dywersyfikacji źródeł dostaw oraz planowania przeprojektowania znacznie wcześniej w cyklu życia produktu niż miało to miejsce w poprzednich generacjach.

Kiedy inżynierowie mogą oczekiwać normalizacji cen i dostępności pamięci?

Na podstawie komunikatów dostawców i prognoz analityków znaczącej poprawy nie należy oczekiwać przed końcem 2027 roku lub rokiem 2028. Planowane są nowe moce produkcyjne, przejścia na nowe procesy oraz rozbudowa linii pakowania dla HBM i zaawansowanej pamięci NAND, jednak ich uruchomienie zajmie kilka lat. Jednocześnie obciążenia związane z wnioskowaniem AI zwiększają popyt zarówno na DRAM, jak i na pamięć NAND klasy SSD, pochłaniając znaczną część tej przyszłej mocy produkcyjnej. Inżynierowie powinni projektować przy założeniu, że pamięć pozostanie zasobem ograniczonym i istotnym kosztowo elementem systemu przez pozostałą część tej dekady.