Procesory RISC-V i SoC dla systemów wbudowanych

Każdy mikroprocesor jest zbudowany na architekturze zestawu instrukcji (ISA), która definiuje wysokopoziomowe funkcje używane do wykonywania operacji obliczeniowych z danymi cyfrowymi. ISA to jeden z podstawowych składników CPU, który definiuje, jak oprogramowanie będzie komunikować się z sprzętem. W zasadzie definiuje polecenia w sposób, który maszyna może zrozumieć i zwykle obejmuje instrukcje dotyczące operacji na pamięci, obsługi danych, operacji arytmetycznych, operacji logicznych i operacji sterowania przepływem. ISA definiuje również, jak instrukcje są przechowywane, kodowane i dostępne.

Dominujące ISA w ciągu ostatnich dwóch dekad to x86, x64 i ARM, które wszystkie napędzały przyjęcie komputingu osobistego i wbudowanego do poziomów, które obserwujemy dzisiaj. Chociaż ARM jest jedną z najczęściej używanych architektur procesorów, nowy konkurent typu open-source jest przyjmowany przez przemysł półprzewodnikowy. Tą alternatywną architekturą jest RISC-V (wymawiane „risk five”), i została przyjęta przez społeczność open-source i dostawców półprzewodników jako alternatywa dla architektur ARM i x86/x64.

Chociaż nie spodziewamy się, że architektury Intel x86/x64 czy ARM znikną w najbliższym czasie, RISC-V stanowi atrakcyjną alternatywę typu open-source. Teraz niektórzy dostawcy półprzewodników wspierają implementacje RISC-V w swoich FPGA, a społeczność open-source odpowiedziała falą IP dostawców i bibliotek, aby przyspieszyć rozwój. W tym artykule przyjrzymy się niektórym z najnowszych produktów opartych na RISC-V, które zostały wprowadzone na rynek przez dostawców półprzewodników.

Co to jest RISC-V?

ISA RISC-V to open-source'owa ISA, która może być używana do definiowania podstawowych manipulacji danymi cyfrowymi na niskim poziomie, które są implementowane w rdzeniu mikroprocesora. Specyfikacja używa zestawu 49 instrukcji, które są kompatybilne z implementacjami 32-bitowymi w sprzęcie. Szerokość słowa może być używana na 64 bity z zestawem 14 instrukcji rozszerzających, lub do 128 bitów (teoretycznie). Jako specyfikacja typu open-source, podstawowy zestaw instrukcji i opcjonalne rozszerzenia mogą być dostosowywane, usuwane lub całkowicie przepisywane, aby zapewnić dostosowaną lub wysoko sprecyzowaną architekturę procesora do użytku w nowych chipach.

Odkąd rozwój RISC-V rozpoczął się w 2010 roku (w Par Lab Berkeley), twórcy RISC-V założyli później SiFive, firmę IP rdzeni procesorów. Firma dostarczyła pierwszą w pełni open-source'ową architekturę rdzenia procesora zbudowaną na RISC-V. Architektura może być używana jako podstawowa specyfikacja do projektowania architektury logiki cyfrowej, która implementuje ISA RISC-V i wszelkie dodatkowe funkcje użytkownika.

Dlaczego budować na RISC-V?

Budowanie niestandardowego procesora aplikacyjnego na RISC-V daje programistom doskonałą ścieżkę do tworzenia nowego procesora na niestandardowym krzemie lub budowania rekonfigurowalnego procesora na FPGA. Rozwój logiki z RISC-V na FPGA przynosi własne korzyści dzięki możliwościom dostosowywania i rekonfiguracji platform FPGA, jak również ich wysokiej gęstości obliczeniowej. Dla aplikacji wbudowanych wymagających więcej niż RTOS, rdzenie RISC-V mogą być przenoszone, aby obsługiwać dystrybucje Linuxa.

Procesory RISC-V i IP

Rozwijający RISC-V mogą używać zestawu instrukcji i jego implementacji sprzętowej na dwa możliwe sposoby: do rozwijania niestandardowych projektów logicznych na nowym projekcie chipa lub do implementacji specjalistycznej logiki na FPGA. Branża dopiero zaczyna używać RISC-V jako podstawowej architektury dla projektów mikrokontrolerów, ale te komponenty nie są dostępne na dużą skalę.

Obecnie zakres komercyjnie dostępnych procesorów, które mogą obsługiwać RISC-V, ogranicza się do FPGA, gdzie RISC-V jest wspierany przez IP dostawcy. Na ten moment, budowanie na FPGA jest doskonałą opcją dla deweloperów systemów, zarówno z perspektywy prototypowania, jak i pod kątem projektowania niestandardowego sprzętu specyficznego dla aplikacji, który jest mocno zoptymalizowany pod kątem obciążeń obliczeniowych.

Microchip PolarFire

Platforma PolarFire od Microchip to flagowa platforma FPGA oparta na RISC-V tej firmy, gdzie gotowy procesor jest budowany bezpośrednio z tkaniny połączeniowej FPGA. Linia produktów PolarFire obejmuje wiele komponentów i numerów części, wszystkie mające na celu najniższe zużycie energii przy wysokiej gęstości obliczeniowej w aplikacjach wbudowanych. Ten SoC FPGA może być mocno dostosowany przy użyciu zestawu narzędzi Libero SoC Design Suite, a rdzenne IP jest dostępne do użytku na platformie PolarFire. Pod względem możliwości sprzętowych, system może obsługiwać transceivery 12,7 Gbps i PCIe 2 I/O.

Efinix Trion i Titanium

Efinix jest mniejszym dostawcą półprzewodników, ale przyjęli RISC-V w swoim IP dostawcy z dwoma produktami SoC dla produktów Trion i Titanium.

Sapphire SoC - Ta implementacja RISC-V jest konfigurowalną instancją użytkownika z opcjonalnym kontrolerem pamięci (DDR lub HyperRAM) i wieloma interfejsami (do 32 GPIO, 3 magistrale I2C, 3 magistrale SPI i 3 UARTy) wbudowanymi w rdzeń urządzenia.

Edge Vision SoC - Ta biblioteka jest przeznaczona dla aplikacji wizji wbudowanej i zawiera standardowe interfejsy dla systemów w tej dziedzinie aplikacji. Dodatkowe funkcje użytkownika, takie jak specjalistyczne bloki DSP lub manipulacja danymi, mogą być dodane do tego IP za pomocą narzędzi deweloperskich.

Produkty rozwojowe są dostępne dla obu linii produktów, aby pomóc użytkownikom rozpocząć pracę z nową platformą, taką jak Trion T20 MIPI D-PHY/CSI-2 Dev Kit dla aplikacji wizyjnych.

Xilinx i Bluespec

Bluespec Inc., oficjalny partner rozwojowy firmy Xilinx, obecnie wspiera implementacje 32-bitowych rdzeni RISC-V na układach FPGA firmy Xilinx. Ten SoC IP jest przeznaczony do aplikacji wymagających pojedynczego rdzenia procesora uruchamiającego Linux na FPGA. RISC-V RV32IMAC SCL wspiera podstawowe instrukcje RISC-V dotyczące Integer (I), mnożenia i dzielenia liczb całkowitych (M), Atomic (A) oraz skompresowane instrukcje (C), pojedyncze i podwójne instrukcje zmiennoprzecinkowe (FD). Użytkownicy mogą implementować rdzeń IP Bluespec RISC-V 32IM na układach FPGA firmy Xilinx korzystając ze standardowego zestawu narzędzi deweloperskich w środowisku Vivado IDE.

Korzyścią z używania sprzętu od głównego dostawcy jak Xilinx jest poziom wsparcia open-source i dostępnych produktów rozwojowych do budowy aplikacji wbudowanych. Szerokie portfolio IP firmy Xilinx może być używane razem z zdefiniowaną w RSIC-V architekturą logiki rdzenia do budowy spersonalizowanej implementacji sprzętowej. Jako przykład, rdzeń IP Freedom E310 od SiFive może być zaprogramowany na platformie rozwojowej Arty A7 od Digitlent za pomocą środowiska Arduino IDE.

Inne produkty wchodzące na rynek

Inne firmy ogłosiły niedawno wprowadzenie na rynek produktów wykorzystujących rdzenie RISC-V w nowych produktach półprzewodnikowych. Te produkty mają być czymś bliższym procesorom aplikacyjnym, które nadal oferują pewną ogólną programowalność za pośrednictwem wbudowanej aplikacji. Do niedawnych ogłoszeń produktów należą:

-

Renesas Application Specific Standard Products (ASSPs), linia produktów opartych na RISC-V, mająca na celu połączenie ogólnego przetwarzania z specyfiką aplikacji.

-

Picocom PC802 5G NR SoC, procesor specyficzny dla aplikacji dla małych komórek 5G NR łączący się z jednostkami radiowymi za pośrednictwem O-RAN Open Fronthaul eCPRI lub JESD204B.

-

Intel teraz będzie wspierać RISC-V poprzez swoją nową dywizję usług odlewniczych, pozwalając firmom bez własnych fabryk na tworzenie projektów kompatybilnych z możliwościami przetwarzania krzemowego Intela.

-

Nadchodzący chip akceleratora AI oparty na RISC-V od Kneron ma na celu wprowadzenie autonomii do samochodów bez kierowcy poprzez wsparcie systemów ADAS poziomu 1 i 2 ADAS systems.

Więcej zasobów do rozwoju RISC-V

Projektowanie układów scalonych to trudna dyscyplina, ale używanie otwartego zestawu instrukcji takiego jak RISC-V jako ramy rozwojowej to świetny sposób na przyspieszenie projektowania architektury chipa. Wyzwaniem dla projektanta logiki jest stworzenie obwodów logicznych, które reprezentują instrukcje zdefiniowane w specyfikacji RISC-V. Dla mikrokontrolera lub MPU jest to duże wyzwanie i wymaga dużej wiedzy; nie jest to coś, co projektant zwykle robi sam.

Jednak w przypadku FPGA istnieje wiele implementacji RISC-V, które mogą być wykorzystane do szybkiego budowania wysoce rozszerzalnej architektury, która zawiera niestandardowe funkcje użytkownika. Jest to coś, nad czym narzędzia dostawców i społeczność open-source spędziły znaczną ilość czasu, i teraz istnieje wiele rdzeni RISC-V, które mogą być wykorzystane w rozwoju FPGA. Aby zacząć, przyjrzyj się niektórym z tych repozytoriów GitHub:

To tylko mały przekrój tego, co jest dostępne, na GitHubie znajdziesz wiele innych repozytoriów open-source, które są przydatne przy różnych FPGA. Dodatkowo, dla wszystkich deweloperów FPGA zainteresowanych budowaniem na ISA, RISC-V International uruchomiło Program Partnerski Szkoleniowy RISC-V. Deweloperzy mogą lepiej zrozumieć korzyści z otwartej współpracy i poszerzyć swoją wiedzę na temat RISC-V.

Wspaniałą cechą architektury RISC-V jest to, że może być modyfikowana i sprzedawana na otwartym rynku. Fabless semiconductor startups teraz oferują swoje podstawowe IP oparte na ISA RISC-V na licencji dla innych firm, na podobnym modelu biznesowym co ARM. Podobnie, firmy udostępniają swoje IP dostawcy do zakupu i użytku w FPGA od głównych producentów półprzewodników. Gdy te komponenty oparte na RISC-V wejdą na rynek, możemy oczekiwać, że zaoferują wysoki poziom specyficzności dla zaawansowanych aplikacji.

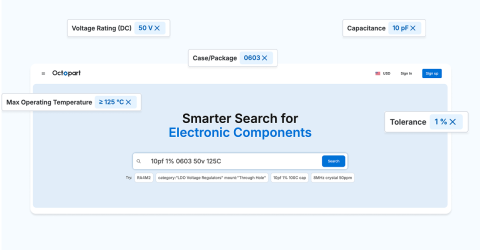

Gdy będziesz gotowy do wyboru swojego FPGA, programowalnego SoC i innych komponentów dla twojego nowego systemu, upewnij się, że używasz zaawansowanych funkcji wyszukiwania i filtracji w Octopart, aby znaleźć wszystkie zaawansowane komponenty potrzebne do zaawansowanych projektów. Korzystając z wyszukiwarki elektroniki Octopart, będziesz miał dostęp do aktualnych danych o cenach dystrybutorów, zapasach części i specyfikacjach części, i wszystko to jest swobodnie dostępne w przyjaznym dla użytkownika interfejsie. Zapoznaj się z naszą stroną układów scalonych, aby znaleźć potrzebne komponenty.

Zostań na bieżąco z naszymi najnowszymi artykułami, zapisując się do naszego newslettera.