Interligação de Memória DDR com FPGAs AMD/Xilinx

Aprenda a interligar memória DDR com FPGAs AMD/Xilinx.

Introdução

Interligar memória volátil DDR a FPGA sem experiência prévia pode parecer bastante intimidador inicialmente. Apesar da flexibilidade inerente de um FPGA, onde poderíamos assumir que podemos conectar a I/O da memória DDR externa em qualquer lugar a quaisquer pinos livres, ainda precisamos considerar muitas restrições.

Por exemplo, onde colocar certos grupos de pinos de memória DDR, quais tensões usar nos bancos, quais relógios precisamos e onde conectá-los, como evitar violações de tempo, e assim por diante.

Além da interligação no nível de esquemático, também precisamos nos preocupar com a interface 'no mundo real' na placa de circuito impresso, como fornecimento e entrega de energia, desacoplamento, terminação, impedância e comprimento de trilha, correspondência de atraso, e mais.

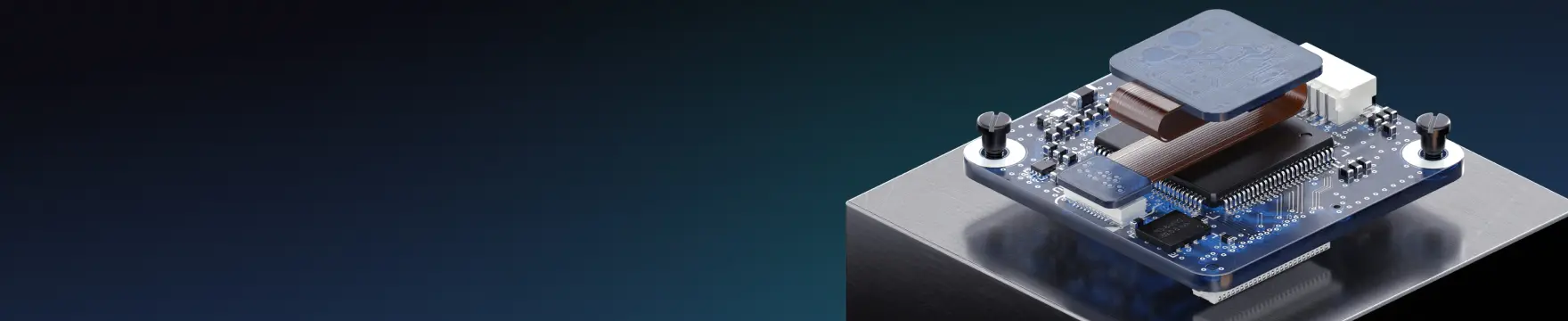

Este artigo examinará a interligação de memória DDR com FPGAs do ponto de vista do sistema e do esquemático. Como um exemplo prático, vamos olhar para um design de DSP de áudio baseado em AMD/Xilinx Spartan-7 (chamado ‘Xerxes’), que interage com alguma memória DDR2.

Hardware do DSP de áudio Xerxes (FPGA AMD/Xilinx Spartan-7 com memória DDR2)

Tipo de Memória

O tipo de memória que usamos depende do design. Depende das nossas necessidades de capacidade e largura de banda de memória, bem como do que nosso FPGA escolhido é capaz.

De modo geral, a maioria dos FPGAs modernos pode interagir com memória DDR2 e DDR3 (e suas variantes de baixa potência, baixa tensão). Claro, memória DDR4 mais rápida e acima também é possível, mas geralmente apenas para FPGAs mais avançados.

Não apenas a taxa de dados máxima possível é importante, mas também os requisitos de tensão e potência, tipo de pacote, custo e disponibilidade são importantes. Tudo isso precisa ser considerado no início da fase de design.

Comparação de Memória DDR (Fonte: synopsys.com)

Ao escolher nosso tipo de memória, também precisamos estar atentos à classificação de velocidade do dispositivo de memória e à classificação de velocidade do controlador de memória dentro do FPGA. Podemos optar por ‘derating’ nossa memória ou controlador, assim não operando na largura de banda total, o que por sua vez nos dá mais folga de tempo.

Tabela Típica de Derating de Memória (Fonte: AMD/Xilinx UG933)

Especificamente para FPGAs AMD/Xilinx, eu sugeriria baixar o IDE Vivado deles e brincar com o IP gratuito Memory Interface Generator (MIG).

Isso mostrará rapidamente quais tipos de memória, graus de velocidade e peças compatíveis você pode usar.

Exemplo de Peças de Memória Compatíveis com Vivado MIG

Você pode perguntar, por que eu escolhi a memória DDR2 para a placa Xerxes?

Embora seja um padrão bastante antigo, usar memória DDR2 significou que eu poderia usar o regulador de 1.8V já disponível na placa (que alimenta outras partes do FPGA) e não precisava adicionar outro regulador separado.

Além disso, o design do Xerxes não tem requisitos particularmente altos de largura de banda de memória, e assim uma interface DDR2 foi suficiente.

Ademais, ter uma interface de largura de banda mais baixa facilita as restrições de PCB, terminação e temporização.

Memória DDR e Interface FPGA

Depois de escolher um dispositivo de memória adequado, é hora de conectá-lo ao FPGA no seu esquemático.

Primeiro, precisamos escolher um banco adequado. Se você está usando uma interface de dados de 16 bits (ou inferior), para a maioria dos FPGAs isso geralmente pode caber em um banco. Se não, precisamos dividir a interface de memória em vários bancos.

Para simplificar, vamos optar por uma interface de memória de 16 bits, como é o caso da placa Xerxes. Escolha um banco livre que possa funcionar com a mesma voltagem da própria memória DDR (no caso do Xerxes, este é o banco 34 a 1.8V devido ao uso de memória DDR2).

Banco FPGA 34 Com Decoupling Apropriado Funcionando a Partir da Fonte de 1.8V

Para FPGAs da AMD/Xilinx, usando as ferramentas Vivado e MIG, obter o pin-out para nossa memória DDR é muito direto. A ferramenta sugere um pin-out adequado para aquele banco, ou podemos atribuir os pinos manualmente e verificar o pin-out.

Ferramenta de Pin-Out Vivado MIG

Se você configurar o pin-out manualmente, garanta que as linhas de bytes DDR individuais tenham o mesmo número de byte do banco e que os strobes diferenciais estejam nos pinos DQS capazes de FPGA diferenciais.

Lembre-se de que o pin-out provavelmente será ajustado durante a etapa de layout e roteamento do PCB. Graças à flexibilidade do FPGA, trocar pinos durante o processo de design do PCB pode simplificar o roteamento e minimizar as transições de camadas.

Para este exemplo, como estamos operando a partir de um único banco, devemos usar o VREF interno, limitando a largura de banda máxima da memória.

Além disso, precisamos estar atentos ao clocking. Idealmente, a fonte de clock deve estar no mesmo banco anexado a um pino (ou pinos, se usando uma fonte de clock diferencial) capaz de clocking.

Finalmente, certifique-se de usar as ferramentas dos fornecedores para verificar o design e o tempo. Então, com o pin-out inicial no lugar, no seu esquemático, defina classes de rede, pares diferenciais e regras, e use codificação por cores para facilitar a sua vida no design de PCBs.

Conexões DDR2 e Fonte de Clock do Banco 34 FPGA

Para um único dispositivo, simplesmente precisamos fazer conexões ponto a ponto no componente de memória DDR.

A terminação deve estar presente nos sinais de endereço/comando/controle (ACC); no entanto, para taxas de dados mais baixas, muitas vezes podemos dispensar isso. Eu sempre adiciono terminação no par de clock diferencial. As vias de dados são terminadas internamente em ambas as extremidades.

Recomenda-se a colocação de resistores de pull-down de 4,7k nos pinos CKE, ODT e, opcionalmente, nos pinos CS#.

Conexões de Sinal e Alimentação do Módulo de Memória DDR2

Finalmente, o módulo de memória precisa ser alimentado, claro. No caso da placa Xerxes, o módulo DDR2 está conectado ao mesmo regulador de 1,8V que o nosso banco FPGA 34. É necessário um desacoplamento apropriado – como regra geral, se não especificado de outra forma em datasheets ou notas de aplicação, vise usar um capacitor pequeno (~100nF) por dois pinos VDD e um capacitor de maior capacidade por dez pinos VDD.

A tensão do pino VREF pode ser gerada por meio de um divisor de potencial simples com um capacitor de filtragem, conforme mostrado na imagem acima.

Conclusão

Neste artigo, delineamos as estratégias básicas para incorporar memória DDR externa, não volátil, em nossos designs baseados em FPGA de um ponto de vista de sistema e esquemático.

Lembre-se de que estes são os conceitos básicos, e dependendo dos requisitos do seu sistema, o design será muito mais envolvido. Especialmente, se você planeja usar partes de memória e interfaces mais rápidas, e múltiplos módulos.

Ao projetar sistemas avançados baseados em FPGA e DDR, certifique-se de que está utilizando as ferramentas e recursos contidos em ferramentas ECAD de classe mundial como o Altium Designer. Certifique-se de garantir seu teste gratuito do Altium Designer e do Altium 365 aqui.