Интерфейсинг DDR-памяти с FPGA от AMD/Xilinx

Узнайте, как осуществить интерфейсинг памяти DDR с FPGA от AMD/Xilinx.

Введение

Подключение волатильной памяти DDR к FPGA без предварительного опыта изначально может показаться довольно сложным. Несмотря на врожденную гибкость FPGA, когда мы могли бы предположить, что мы можем подключить входы/выходы внешней памяти DDR практически к любым свободным контактам, нам все же нужно учитывать множество ограничений.

Например, где разместить определенные группы контактов памяти DDR, какие напряжения использовать для банков, какие тактовые сигналы нам нужны и куда их подключать, как избежать нарушений временных параметров и так далее.

Помимо простого «схематического» подключения, нам также нужно беспокоиться о «реальном» интерфейсе на печатной плате, таком как источники питания и их подача, развязка, терминирование, импеданс и длина трасс, согласование задержек и многое другое.

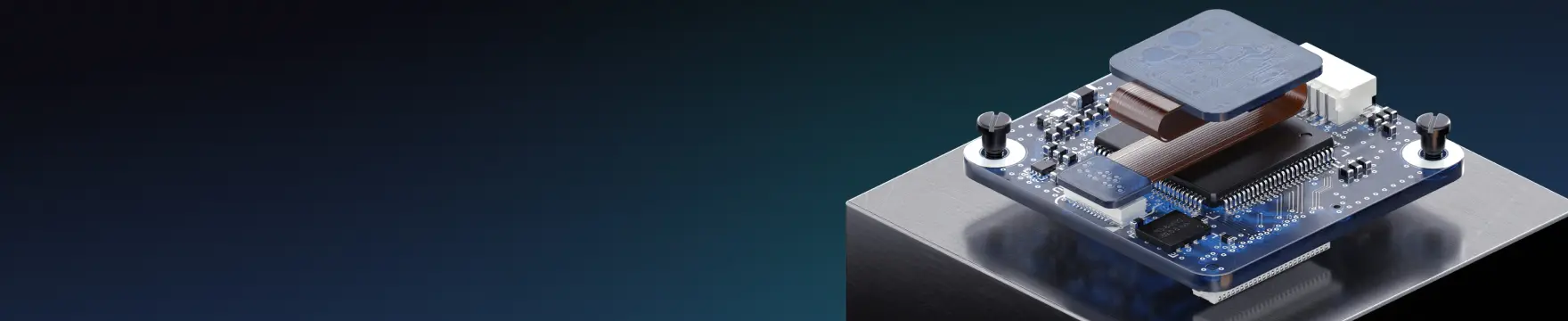

В этой статье мы рассмотрим подключение памяти DDR к FPGA с точки зрения системного уровня и схемотехники. В качестве практического примера мы рассмотрим аудио DSP-дизайн на базе AMD/Xilinx Spartan-7 (названный «Xerxes»), который подключается к некоторой памяти DDR2.

Аппаратное обеспечение аудио DSP Xerxes (AMD/Xilinx Spartan-7 FPGA с памятью DDR2)

Тип памяти

Выбор типа памяти зависит от дизайна. Это зависит от наших требований к емкости памяти и пропускной способности памяти, а также от того, на что способен наш выбранный FPGA.

Как правило, большинство современных FPGA могут работать с памятью DDR2 и DDR3 (и их вариантами с низким энергопотреблением и низким напряжением). Конечно, более быстрая память DDR4 и выше также возможна, но обычно только для более продвинутых FPGA.

Важны не только максимально возможная скорость передачи данных, но и требования к напряжению и мощности, тип корпуса, стоимость и доступность. Все это необходимо учитывать на раннем этапе проектирования.

Сравнение памяти DDR (Источник: synopsys.com)

Выбирая тип нашей памяти, мы также должны обратить внимание на класс скорости памяти и рейтинг скорости контроллера памяти внутри FPGA. Мы можем выбрать «понижение» нашей памяти или контроллера, тем самым не работая на полной пропускной способности, что в свою очередь дает нам больше времени на настройку.

Типичная таблица понижения памяти (Источник: AMD/Xilinx UG933)

Специально для FPGA AMD/Xilinx я бы предложил скачать их среду разработки Vivado и поиграть с бесплатным IP Memory Interface Generator (MIG).

Это быстро покажет вам, какие типы памяти, классы скорости и совместимые компоненты вы можете использовать.

Пример совместимых компонентов памяти Vivado MIG

Вы можете спросить, почему я выбрал память DDR2 для платы Xerxes?

Несмотря на то, что это довольно старый стандарт, использование памяти DDR2 позволило мне использовать уже имеющийся на плате регулятор 1.8V (он питает другие части FPGA) и не требовало добавления еще одного отдельного регулятора.

Кроме того, дизайн Xerxes не имеет особо высоких требований к пропускной способности памяти, и поэтому интерфейс DDR2 был достаточен.

Более того, наличие интерфейса с более низкой пропускной способностью упрощает требования к печатной плате, терминированию и временным параметрам.

Память DDR и интерфейс FPGA

После выбора подходящего устройства памяти пришло время подключить его к FPGA в вашей схеме.

Сначала нам нужно выбрать подходящий банк. Если вы используете 16-битный (или меньший) интерфейс данных, для большинства FPGA это обычно может поместиться в одном банке. Если нет, нам нужно разделить интерфейс памяти на несколько банков.

Для простоты мы выберем 16-битный интерфейс памяти, как это сделано на плате Xerxes. Выберите свободный банк, который может работать от того же напряжения, что и сама память DDR (в случае Xerxes это банк 34 на 1.8V из-за использования памяти DDR2).

Банк FPGA 34 с подходящей развязкой, работающей от источника 1.8V

Для FPGA AMD/Xilinx, используя инструменты Vivado и MIG, получение распиновки для нашей памяти DDR очень просто. Инструмент либо предлагает подходящую распиновку для этого банка, либо мы можем вручную назначить контакты и проверить распиновку.

Инструмент распиновки Vivado MIG

Если вы настраиваете распиновку вручную, убедитесь, что отдельные линии байтов DDR имеют одинаковый номер байта банка, а дифференциальные стробы находятся на дифференциальных способных к DQS контактах FPGA.

Помните, что распиновка, вероятно, будет скорректирована на этапе размещения и трассировки печатной платы. Благодаря гибкости FPGA, изменение контактов в процессе проектирования печатной платы может упростить трассировку и минимизировать переходы между слоями.

В этом примере, поскольку мы работаем с одним банком, мы должны использовать внутренний VREF, что ограничивает максимальную пропускную способность памяти.

Кроме того, следует обратить внимание на тактирование. В идеале источник тактового сигнала должен находиться в том же банке, что и подходящий для тактирования контакт (или контакты, если используется дифференциальный источник тактового сигнала).

В конце концов, убедитесь, что вы используете инструменты поставщика для проверки дизайна и временных параметров. Затем, имея начальное расположение выводов, в вашей схеме определите классы сетей, дифференциальные пары и правила, а также используйте цветовую кодировку, чтобы упростить вашу работу с дизайном печатной платы.

Соединения DDR2 и источник тактового сигнала в банке 34 FPGA

Для одного устройства нам просто нужно выполнить точечные соединения на компоненте памяти DDR component.

Терминирование должно присутствовать на сигналах адреса/команды/управления (ACC); однако, для более низких скоростей передачи данных мы часто можем обойтись без этого. Я всегда добавляю терминирование на дифференциальную пару тактового сигнала. Линии данных байтов терминируются внутренне с обеих сторон.

Рекомендуется установить подтягивающие резисторы на 4.7 кОм на линии CKE, ODT и, по желанию, на линии CS#.

Сигнальные и питающие соединения модуля памяти DDR2

В конце концов, модуль памяти, конечно, нужно питать. В случае с платой Xerxes модуль DDR2 подключается к тому же регулятору 1.8В, что и наш банк 34 FPGA. Требуется соответствующее развязывание – как правило, если в технических описаниях или прикладных заметках не указано иное, целесообразно использовать один маленький (~100нФ) конденсатор на каждые два контакта VDD и один, больший объемный конденсатор на каждые десять контактов VDD.

Напряжение на контакте VREF может быть сформировано с помощью простого делителя напряжения с фильтрующим конденсатором, как показано на изображении выше.

Заключение

В этой статье мы описали основные стратегии включения внешней, нелетучей памяти DDR в наши FPGA-базированные проекты с точки зрения системного и схемотехнического уровня.

Помните, что это лишь азы, и в зависимости от требований вашей системы, проект будет гораздо более сложным. Особенно, если вы планируете использовать более быстрые компоненты памяти и интерфейсы, а также несколько модулей.

При проектировании продвинутых систем на основе FPGA и DDR убедитесь, что вы используете инструменты и функции, содержащиеся в мирового класса инструментах ECAD, таких как Altium Designer. Не забудьте получить бесплатную пробную версию Altium Designer и Altium 365 здесь.