Đồ thị Điện áp và Dòng điện trên Đường truyền có Điện trở Kết thúc Chuỗi

Trong cả hai cuốn sách của chúng tôi, Right the First Time, A Practical Handbook on High Speed PCB and System Design, Tập 1 và 2, cũng như trong các khóa học tại chỗ và công cộng của chúng tôi, chúng tôi đã nói về giá trị của đường truyền có kết thúc chuỗi. Với loại đường truyền này, không có sự tiêu thụ năng lượng nào trừ khi đường truyền đang được sạc. Điều này cho phép thực hiện nhiều tính toán với lượng năng lượng tối thiểu. Nhưng việc hiểu rõ cách thức hoạt động của loại đường truyền này có thể gây nhầm lẫn và hơi đáng sợ. Cụ thể, việc hình dung cách thức hoạt động này có thể là một thách thức. Mục đích của bài viết này là làm rõ cách thức hoạt động của đường truyền này và cung cấp các hình ảnh minh họa.

Cơ bản

Đường truyền có kết thúc chuỗi là phương pháp chính để kết nối thiết bị CMOS với trở kháng đầu ra không khớp. Trong phần thảo luận sau đây, tất cả các thiết bị được đề cập đều là thiết bị CMOS. Thiết bị CMOS thực sự đã dẫn đến sự suy tàn của công nghệ ECL bởi vì với ECL, bất kể làm gì, đường truyền luôn tiêu thụ năng lượng và gây ra vấn đề làm mát nghiêm trọng với các máy móc lớn.

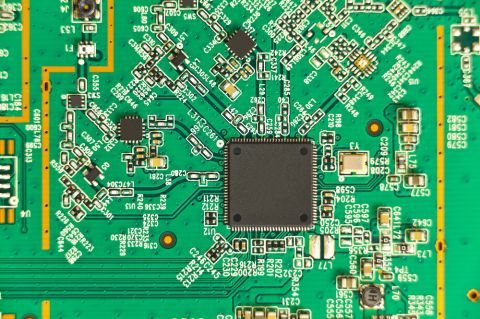

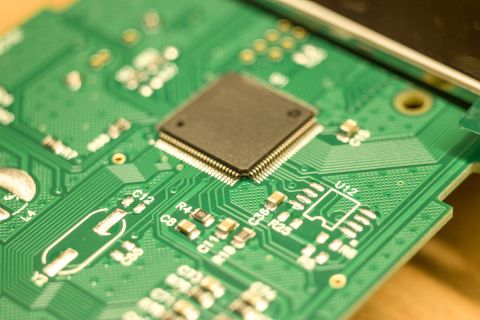

Hình 1 là một trình điều khiển CMOS 5V tiêu biểu với một đường truyền 50 Ohm được kết nối với một bộ thu CMOS thụ động.

Một bộ thu thụ động có nghĩa là nó chỉ đơn giản phản ứng với dạng sóng điện áp được trình bày tại đầu vào của nó. Đối với mục đích của lời giải thích này, các bộ thu CMOS trông giống như những tụ điện rất nhỏ được coi là mạch mở. Ở đây, đường dây dài khoảng 12 inch (30 cm). Năng lượng trong một PCB di chuyển xấp xỉ sáu inch mỗi nanogiây. Vì vậy, đường dây này dài khoảng hai nanogiây.

Sơ đồ biểu diễn của đường truyền trong Hình 1 được hiển thị trong Hình 2.

Như có thể thấy, có điện dung, điện trở, và cảm kháng phân bố dọc theo chiều dài của đường truyền. Như đã được ghi chú trong các bài viết trước, những yếu tố này được gọi là các yếu tố nhiễu, và chúng thiết lập hành vi của một đường truyền với tỷ lệ của cảm kháng trên mỗi đơn vị chiều dài so với tụ điện trên mỗi đơn vị chiều dài. Lưu ý rằng, dẫn kháng nhiễu của lớp nền và góc mất mát đã được bỏ qua trong lúc này vì chúng không quá quan trọng để hiểu rõ hình dạng cơ bản của dạng sóng điện áp và dòng điện. Ở tần số đủ cao, nhưng không quá cao đến mức chúng ta quan tâm đến hiệu ứng bề mặt hoặc độ nhám của đồng, cảm kháng và điện dung xác định trở kháng của đường dây, như được hiển thị trong Phương trình 1.

Lưu ý: Khi chọn driver cho đường truyền có kết thúc chuỗi, trở kháng đầu ra của driver phải bằng hoặc nhỏ hơn trở kháng của đường truyền.

Trong Phương trình 1, độ tự cảm trên mỗi đơn vị chiều dài được biểu thị là Lo, và điện dung trên mỗi đơn vị chiều dài được biểu thị là Co. (Hai biến số này có thể được xác định cho một loại đường truyền cụ thể sử dụng công cụ như một trình giải 2D). Mạch tương đương tại T0 là nguồn điện áp, và Hình 3 là mạch tương đương khi quá trình chuyển từ logic 0 sang logic 1 bắt đầu.

Bộ chia điện áp được hình thành bởi sự kết hợp của trở kháng đầu ra của driver và kết thúc chuỗi ở phần trên và trở kháng của đường truyền ở phần dưới. Khi kết thúc chuỗi được chọn đúng cách, sự kết hợp của Zout và Zst sẽ giống như Zo. Trong ví dụ này, cả hai đều là 50 ohm.

Hình 4 cho thấy các dạng sóng điện áp và dòng điện cho đường truyền có kết thúc chuỗi trong Hình 1 khi driver chuyển từ logic 0 sang logic 1.

Dạng sóng điện áp bắt đầu đi xuống đường truyền có điện trở kết thúc là V/2, đại diện cho một nửa điện áp nguồn. Vì vậy, khi đi ra ngoài, điện dung được sạc lên V/2. Điều này được thể hiện qua dạng sóng dòng điện hiển thị ở phần dưới của Hình 4 và có thể được chứng minh bằng cách tính V dễ dàng qua hai điện trở mắc nối tiếp.

Lưu ý: Định luật Ohm mô tả mối quan hệ giữa dòng điện qua một điện trở và điện áp qua nó. Cơ bản, định luật này nói rằng dòng điện tính bằng ampe bằng với điện áp tính bằng volt qua một điện trở chia cho điện trở tính bằng ôm.

Khi dòng điện đến cuối của đường truyền, nơi là một mạch mở với tụ điện song song, điện áp tăng gấp đôi lên giá trị toàn phần của V. Trường EM phản xạ trở lại từ đầu mở của đường truyền, và nó sạc điện dung lên phần còn lại đến V. Khi trường EM trở lại điểm bắt đầu của đường dây, điện dung được sạc đầy, và dòng điện giảm xuống còn không. Điều này được thấy ở phần dưới của Hình 4.

Những điều quan trọng cần nhớ về hoạt động được mô tả trong Hình 4 bao gồm:

- Dạng sóng dòng điện ở phía dưới của đồ họa kéo dài gấp đôi chiều dài điện của đường truyền.

- Dòng điện tối đa rút từ hệ thống nguồn được thiết lập bởi Zo của đường truyền và điện áp cung cấp.

- Tích của dạng sóng dòng điện và dạng sóng điện áp tại đầu vào của đường truyền là công suất phải được cung cấp bởi hệ thống nguồn.

- Nội dung tần số của dạng sóng không được thiết lập bởi tần số đồng hồ.

Tóm tắt

Phương pháp tiêu thụ công suất thấp nhất cho tín hiệu logic tốc độ cao bao gồm việc sử dụng đường truyền có kết thúc dạng chuỗi. Đây là phương pháp tiêu thụ công suất thấp nhất vì năng lượng chỉ được tiêu thụ trong mạch khi một dòng logic được chuyển từ logic 0 sang logic 1.

Bạn có muốn tìm hiểu thêm về cách Altium có thể giúp bạn với thiết kế PCB tiếp theo của mình không? Hãy nói chuyện với một chuyên gia tại Altium và tìm hiểu thêm về việc đưa ra quyết định thiết kế một cách dễ dàng và tự tin.