Có Chuyện Gì Với Tất Cả Các Lớp Trong Dấu Chân PCB?

Các footprint PCB của bạn bao gồm nhiều lớp. Lớp nào trong số này là quan trọng nhất và chúng nên chứa những gì? Chúng ta sẽ khám phá trong bài viết này.

Mọi PCB đều cần có linh kiện, kể cả khi những linh kiện đó được đánh dấu là DNI và không bao giờ được lắp vào bộ phận cuối cùng. Mỗi linh kiện có một dấu chân trên PCB, và mỗi dấu chân trên PCB chứa thông tin trên các lớp khác nhau. Các lớp trong dấu chân PCB đại diện cho thông tin quan trọng về linh kiện thực tế, nhưng không phải tất cả chúng đều được người dùng định nghĩa.

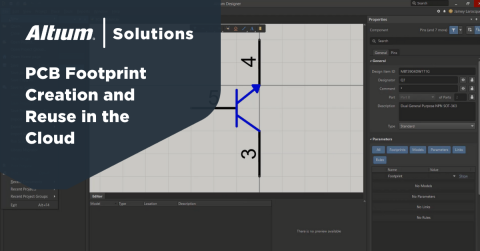

Vì chúng tôi gần đây đã nhận được một số câu hỏi từ người xem trên kênh Altium Academy về dấu chân PCB và các lớp thiết yếu mà chúng nên chứa, bài viết này sẽ tập trung vào thông tin nào được chứa trong mỗi dấu chân. Từ thông tin này, bạn nên có thể nhận ra các lớp dấu chân quan trọng nhất và thông tin mà chúng nên chứa.

Các Lớp Quan Trọng trong Dấu Chân PCB

Nếu bạn là người mới sử dụng phần mềm thiết kế PCB, và bạn đang dành thời gian để tạo dấu chân tùy chỉnh đầu tiên của mình, bạn sẽ nhận thấy nhiều lớp trong trình chỉnh sửa dấu chân của mình. Những lớp này tương ứng với các lớp cơ bản được sử dụng để tạo bố cục PCB của bạn, nhưng các lớp trong dấu chân của bạn cần bao gồm thông tin cụ thể. Một số thông tin này phải được tạo ra thủ công khi xây dựng dấu chân linh kiện, và một số thông tin được tự động tạo ra trong trình chỉnh sửa PCB.

Bảng dưới đây mô tả đầy đủ danh sách các lớp cần thiết để tạo một footprint. Tên của các lớp có dấu sao (*) là bắt buộc để tạo một footprint cơ bản, tuy nhiên, thông tin bổ sung sẽ cần thiết để tạo một footprint cho PCB.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Như bạn có thể thấy, hầu hết các lớp trong một dấu chân PCB cần được tạo ra một cách thủ công, nhưng hầu hết các lớp cần thiết tuyệt đối lại được tự động tạo ra. Vậy tất nhiên, điều này đặt ra câu hỏi, bạn nên tạo những lớp nào một cách thủ công, mặc dù không phải tất cả các lớp này đều cần thiết cho việc sử dụng trong bố trí PCB?

Khi bạn thấy “tự động tạo” trong bảng này, nó có nghĩa là các lớp được tạo ra bởi bộ máy quy tắc thiết kế PCB, và bạn không được yêu cầu hoặc không thể tạo thông tin này một cách thủ công trong các dấu chân PCB của mình. Trong Altium Designer, những điều này được quản lý bên trong bố trí PCB trong PCB Rules and Constraints Editor.

Keepouts

Một ví dụ khác khá quan trọng cả cho việc sản xuất, lắp ráp và EMI/EMC là keepouts. Một lớp keepout được sử dụng để đảm bảo rằng mọi thứ khác trong bố trí PCB được giữ cách xa phần đó của dấu chân PCB, bao gồm mọi thứ từ đồng đến các thành phần khác trong bố trí PCB. Hầu hết các thành phần sẽ không cần một lớp keepout.

Một ví dụ về lớp keepout trên một thành phần PCB được hiển thị dưới đây. Mục đích của lớp này là để ngăn chặn việc đặt thành phần và định tuyến trong khu vực keepout. Bởi vì thành phần này là một kết nối, nhưng loại thành phần có thể không rõ ràng chỉ bằng cách nhìn vào dấu chân, nên việc định nghĩa giới hạn đặt và định tuyến bằng cách sử dụng keepouts là hợp lý.

Sân

Một lớp sân được sử dụng để vẽ khoảng cách yêu cầu xung quanh dấu chân PCB như được quy định trong tiêu chuẩn IPC-7351. Tiêu chuẩn đưa ra khuyến nghị khoảng cách sân dựa trên ba mức độ mật độ:

- Nhiều nhất (mật độ thấp nhất):

- Thành phần Gắn bề mặt: Khoảng cách sân tối thiểu 0.25 mm (0.01 inches).

- Thành phần Xuyên lỗ: Khoảng cách sân tối thiểu 0.5 mm (0.02 inches).

- Trung bình (mật độ vừa phải):

- Thành phần Gắn bề mặt: Khoảng cách sân tối thiểu 0.15 mm (0.006 inches).

- Thành phần Xuyên lỗ: Khoảng cách sân tối thiểu 0.25 mm (0.01 inches).

- Ít nhất (mật độ cao nhất):

- Thành phần Gắn bề mặt: Khoảng cách sân tối thiểu 0.1 mm (0.004 inches).

- Các thành phần qua lỗ: Khoảng trống tối thiểu 0,15 mm (0,006 inch).

Một ví dụ về đường viền sân chơi cho thấy sự cho phép về sự dư thừa của sân chơi được hiển thị dưới đây:

Đường viền này chỉ là một công cụ được nhà thiết kế PCB sử dụng để đảm bảo họ không đặt các thành phần quá gần nhau. Rõ ràng, nó nên được hiểu rằng các mức độ mật độ chấp nhận được khác nhau sẽ yêu cầu các bản vẽ sân chơi khác nhau, và bạn có thể thấy rằng một sân chơi đã bị bỏ qua trong một thành phần trong khi thay vào đó một đường viền khoảng trống được đặt trong lớp mực in để xác định giới hạn khoảng trống. Thật không may, điều này có thể dẫn đến việc đoán mò trong quá trình sắp xếp, và có thể yêu cầu một số sự điều chỉnh thành phần trước khi một bảng mạch có thể được chuyển vào dây chuyền SMT nếu các dấu hiệu mực in không chỉ ra khoảng trống không đủ.

Thân 3D

Các hệ thống CAD hỗ trợ xem 3D của PCB cũng sẽ cho phép bạn gán một mô hình 3D cho một thành phần. Điều này có thể được gán như một mô hình STEP hoặc dưới dạng một định dạng mô hình rắn khác. Trong dấu chân thành phần, lớp mô hình 3D hiển thị phạm vi của mô hình 3D được chiếu vào một mặt phẳng 2D từ quan điểm nhìn từ trên xuống (đây là khu vực màu tím ở trên). Các chi tiết của gói chỉ có thể được nhìn thấy trong chế độ xem 3D, chúng sẽ không được hiển thị trong lớp tương ứng trong dấu chân PCB.

Đường Viền Lắp Ráp

Đường viền lắp ráp cho một linh kiện chỉ cần thiết để tạo bản vẽ lắp ráp, mà người lắp ráp của bạn có thể sử dụng để kiểm tra xem các linh kiện có được đặt đúng vị trí hay không. Xưởng sản xuất của bạn không cần xuất các lớp lắp ráp dưới dạng Gerber. Người lắp ráp của bạn có thể sử dụng chúng nội bộ để tạo bản vẽ lắp ráp riêng của họ, hoặc bạn có thể sử dụng các đường viền này để tạo bản vẽ lắp ráp của riêng mình, hoặc trong một công cụ vẽ kỹ thuật hoặc trong công cụ Draftsman trong Altium Designer.

Điều đặc biệt về Draftsman trong Altium Designer là mặt trên của thân 3D cũng có thể được chiếu vào bản vẽ lắp ráp, như được hiển thị trong ví dụ dưới đây. Bình thường, nếu bạn muốn tạo chi tiết này trong một ứng dụng vẽ kỹ thuật, bạn sẽ cần phải thủ công chiếu tất cả mô hình thân 3D của mình vào các tệp DXF, sau đó biên soạn những tệp DXF đó thành một lớp duy nhất trong bản vẽ lắp ráp. Draftsman làm điều này cho bạn và ngay lập tức tạo ra các bản vẽ chi tiết cao như ví dụ được hiển thị dưới đây.

Khi bạn cần tạo các footprint tùy chỉnh hoặc truy cập vào các footprint đã được nhà sản xuất xác nhận, hãy chắc chắn sử dụng bộ công cụ thiết kế PCB hàng đầu ngành trong Altium Designer®. Để thực hiện sự hợp tác trong môi trường đa ngành nghề ngày nay, các công ty đổi mới đang sử dụng nền tảng Altium 365™ để dễ dàng chia sẻ dữ liệu thiết kế và đưa dự án vào sản xuất.

Chúng ta mới chỉ khám phá bề mặt của những gì có thể thực hiện với Altium Designer trên Altium 365. Bắt đầu dùng thử miễn phí Altium Designer + Altium 365 ngay hôm nay.