Retroexcavado y Relleno para Vías Ciegas y Enterradas en PCBs

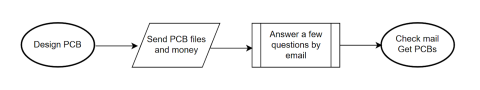

Las vías ciegas no son solo para PCBs HDI, también se utilizan en construcciones estándar con perforación mecánica y sin capas exteriores delgadas o capas de película de construcción. Estos diseños encuentran su lugar en muchos sistemas diferentes, y para mí esto es más común en diseños de alta velocidad o diseños RF que requieren agujeros terminados para pines de ajuste a presión o pines roscados. No importa cuál sea la aplicación, la presencia de estos agujeros conduce a un proceso de laminación múltiple para perforar, platear y prensar las capas en el apilado de la PCB.

El número de laminaciones requeridas para construir una PCB es un buen indicador del precio asumiendo un proceso tradicional de grabado y perforación mecánica. Dependiendo de cómo se utilicen las vías ciegas/enterradas en una PCB, el número de laminaciones puede no coincidir con tu cuenta inicial. Por lo tanto, antes de comenzar a colocar vías ciegas y enterradas en tu apilado de PCB, ten en cuenta que tu fabricante podría tomar un enfoque alternativo para construir tu PCB, lo cual podría impactar en los costos totales y el área de enrutamiento. Examinaré cómo la colocación de vías ciegas y enterradas impacta en el número de ciclos de laminación y, en última instancia, en el número de pasos de procesamiento y los costos asociados con la construcción.

El Costo de los Ciclos de Laminación

Cada ciclo de laminación en la fabricación de PCB implica un paso de perforación y chapado, y así es como podemos formar vías ciegas/enterradas en un apilado de PCB. Cuando hay vías ciegas/enterradas presentes en un diseño, se utilizan múltiples pasos de laminación para unir cada grupo de capas grabadas y crear el apilado final. Cada ciclo de laminación añade pasos de procesamiento y, por lo tanto, añade costo al diseño. Aunque las vías ciegas son absolutamente necesarias en muchos productos, algunas consideraciones simples sobre el orden de los pasos de procesamiento pueden compensar parte del costo adicional y ayudar a mantener su producto competitivo.

Normalmente, contaríamos el número de tramos de capas que requieren vías ciegas/enterradas, añadiríamos 1 ciclo para el núcleo central o las capas de sellado en el exterior del apilado, y obtendríamos el número total de laminaciones requeridas. Por ejemplo, considera el apilado a continuación con una vía pasante y una vía enterrada para circuitos impresos RF embebidos, lo cual discuto con más detalle en otro artículo.

En este ejemplo, tenemos un apilado simétrico que requiere dos ciclos de laminación: uno para la vía enterrada embebida, y otro ciclo para las dos capas exteriores. Este es un ejemplo simple que ilustra el proceso de multi-laminación estándar requerido para formar vías ciegas/enterradas.

Existen casos en los que el uso de vías ciegas/enterradas puede permitir menos ciclos de laminación o un enfoque de procesamiento diferente al de la laminación secuencial que podríamos encontrar en uno de los apilamientos HDI estándar. Algunos de estos casos incluyen:

- Vías ciegas que comienzan desde una capa superficial o vías enterradas desplazadas (construcciones no híbridas)

- Apilamientos con vías ciegas/enterradas cruzadas

- Apilamientos híbridos con vías ciegas/enterradas

- Apilamientos inversos (o apilamientos cap-core)

Perforación inversa y relleno

Un proceso alternativo que se puede utilizar en lugar de la laminación secuencial es perforar inversamente y rellenar en capas específicas, ya que esto podría eliminar uno o más pasos de laminación. En la perforación inversa y relleno, se forma una vía ciega o enterrada más allá del tramo de capa donde se necesita, pero luego el fabricante perfora inversamente la vía ciega/enterrada hasta la longitud deseada. Esto termina la vía en la capa deseada, y el espacio sobrante en el dieléctrico perforado se llena con epoxi no conductor. El área rellenada puede luego ser plateada, como en los casos en que la capa perforada es una capa de plano de cobre.

En algunos de los ejemplos dados anteriormente, esta puede ser una forma preferida de fabricar algunos de los apilamientos, ya que podría eliminar uno o más ciclos de laminación. Un poco de anticipación de los pasos de procesamiento en estos ejemplos te ayudará a planificar mejor tu uso de vías ciegas/enterradas, y posiblemente eliminar algunos pasos de laminación en la fabricación de PCB.

Vías Ciegas/Enterradas Asimétricas

La fabricación de PCB generalmente asume y procede con simetría en la disposición de capas, y por lo tanto, en la laminación. Sin embargo, los apilamientos de PCB con vías ciegas/enterradas pueden no utilizar una colocación simétrica en el apilado. Por ejemplo, con una vía enterrada como el caso a continuación, este será un caso clásico donde la perforación inversa y el relleno se evalúan como la solución de fabricación en lugar de usar una laminación adicional.

En este ejemplo, mantener el apilado de capas simétrico durante la fabricación causaría dos posibles procesos:

- Fabricar primero L3-L6, seguido por los pares de capas L2/L7 y L1/L8 (3 laminaciones en total)

- Fabricar primero L2-L7, perforación inversa y relleno, y terminar con el par de capas L1/L8 (2 laminaciones en total)

En el proceso de taladrado y relleno de L6-L7, el taladrado posterior tiene el potencial de romper pistas en la vecindad de los taladros. Obviamente, esto elimina la principal ventaja de usar vías ciegas/enterradas, que es permitir algo de espacio de enrutamiento manteniendo el barril de la vía y las almohadillas alejadas de las pistas fuera del alcance de las capas. Por lo tanto, esto funciona mejor si la parte taladrada posteriormente solo implica taladrar a través de un vertido de cobre o una capa de plano. Con una capa de plano, el taladrado posterior cortará a través del cobre, pero el replacado de cobre requerido será el mismo en todas partes y, por lo tanto, se puede usar un enchapado estándar para reformar el cobre.

Cruzando Vías Ciegas/Enterradas

Ahora examinemos el caso de vías ciegas/enterradas que se cruzan entre sí en diferentes alcances de capas. Este caso es el más interesante ya que también puede involucrar disposiciones desplazadas (asimétricas) de vías, que luego también se cruzan entre sí en el apilado de PCB. Aunque hay algunas razones eléctricas por las que podrías necesitar estas vías ciegas/enterradas cruzadas, asignaciones creativas de capas podrían permitir un proceso de taladrado posterior y relleno en algunos alcances de capas.

Por ejemplo, considera el siguiente apilado. Esto puede involucrar múltiples vías ciegas cruzándose entre sí en el apilado, lo que lleva a múltiples rondas de taladrado posterior y relleno durante la fabricación.

En un proceso de fabricación de taladro y relleno para este apilado, la visión típica sería que el diseño toma tres laminaciones con taladro y chapado, seguido por el taladrado y chapado de los vías pasantes. Sin embargo, el via más grande mixto y el via enterrado podrían proceder de la siguiente manera:

- La sección de L3 a L8 se fabrica primero con taladrado y chapado completos de vías pasantes en este intervalo de capas

- Los vías ciegos más largos en el intervalo de capas L3-L8 se taladran hacia atrás primero, mientras que los vías restantes formarán los vías enterrados en un paso posterior

- Los agujeros taladrados hacia atrás se rellenan con epoxi no conductor y se chapados en cualquier capa de plano de cobre

- Los intervalos de capas exteriores se taladran, laminan y chapados

- Los vías pasantes de L1-L10 se taladran y chapados para completar el apilado

Podría haber razones por las que se necesita un via ciego dedicado con un alcance de capa específico, incluso si su alcance cruza otro alcance de capa diferente. Un caso de uso que mencioné anteriormente es el caso de circuitos RF integrados, otro es el caso de pines de ajuste a presión con un apilado de PCB grueso. Otro caso de uso es eliminar un retroceso en la inserción de un pin para una transición de conector de alta velocidad. Sea cual sea el caso de uso, cada via ciego/enterrado que cruce creará más costos, así que concéntrate en qué cruces puedes consolidar y planifica la distribución de señales importantes alrededor de estas transiciones.

Apilados Híbridos Con Vias Ciegas

Los apilados híbridos son diseños donde el apilado de PCB utiliza una mezcla de conjuntos de materiales. Lo más común es que esto involucre el uso de materiales PTFE y FR4 estándar para diseños RF+digital (lo cual he hablado extensamente en otros artículos), pero por supuesto también se pueden mezclar otros conjuntos de materiales. Cuando estos apilados incluyen vias ciegas/enterradas, también requerirán múltiples laminaciones, como se esperaría.

La pregunta con un apilado híbrido es si laminar primero las laminaciones híbridas individuales y apilar/plaquear estas para formar los agujeros pasantes, o si colocar cada capa híbrida individualmente y perforar/plaquear para formar las vías finales. Por ejemplo, echa un vistazo al agrupamiento de materiales para un apilado híbrido mostrado a continuación.

De esto, podemos ver dos áreas potenciales donde se podría aplicar taladro-retroceso y relleno:

- De L1 a L2 en la vía enterrada 2:3

- De L5 a L6 en la vía ciega 6:10

En el conjunto de materiales híbridos exteriores, no tiene mucho sentido realizar taladro-retroceso y relleno para formar la pequeña vía enterrada exterior. Para las vías internas, podría tener más sentido dado que las vías ciegas superpuestas solo se pierden entre sí por una capa. En este caso, siempre que el tramo de capa taladrada hacia atrás involucre una capa de plano o esté despejado y no tenga trazas, el taladro-retroceso y relleno eliminaría una de las laminaciones.

Apilado Inverso (también conocido como Apilados Cap-Core)

Los apilamientos cap-core colocan efectivamente planos en las capas exteriores y utilizan vías enterradas en las capas internas de señal para enrutar las pistas de señal. Se utilizan agujeros pasantes para alcanzar componentes en las otras capas y para unir los planos externos. El ejemplo más simple es con un PCB de 4 capas, donde las dos capas internas se utilizan para señal y se enrutan con vías enterradas. Con un mayor número de capas, las capas externas de tapa aún requerirán las laminaciones finales antes de perforar y platear los agujeros pasantes, pero las capas internas podrían utilizar un proceso de retroperforado y relleno en lugar de una laminación secuencial. Esto se muestra en el apilamiento cap-core a continuación.

Existen múltiples opciones donde se podría aplicar el taladrado y relleno posterior: en la región entre las vías enterradas largas/cortas (L3-L4 y L7-L8), fuera del intervalo de capas L4-L7, o en los intervalos de capas superficiales (L1-L2 y L9-L10). Los intervalos de capas superficiales tienen más sentido en un apilado núcleo-tapa debido al uso de planos en la capa exterior, pero solo mientras el taladrado posterior no atraviese los pads de los componentes, por lo que solo podría usarse en un PCB de un solo lado. Los intervalos de capas internas también son candidatos, particularmente en este apilado de 10 capas núcleo-tapa que podría contener capas de plano adicionales en el interior del apilado.

Resumen

Cuando se utiliza el chapado después del taladrado posterior, podría haber un pequeño hundimiento en el área del chapado en la capa rechapada. Este hundimiento normalmente será tan pequeño como ~1 mil. Cuando se aplica el taladrado y relleno posterior, normalmente es en vías ciegas/enterradas taladradas mecánicamente, las cuales ocuparán dieléctricos más gruesos. Por lo tanto, en la mayoría de los casos prácticos, el hundimiento restante no impactará la variación natural del grosor de la capa dieléctrica.

Aunque pueda parecer paradójico incorporar el taladrado posterior en un diseño de vía de PCB que tiene como objetivo eliminar el taladrado posterior, esto demuestra que el uso juicioso y dirigido del taladrado posterior termina siendo un gran ahorro de costos. Un poco de anticipación podría permitirte aprovechar este proceso e incluso especificarlo para la fabricación.

Ya sea que necesites construir electrónica de potencia confiable o sistemas digitales avanzados, utiliza el conjunto completo de características de diseño de PCB y herramientas CAD de clase mundial en Altium Designer®. Para implementar la colaboración en el entorno interdisciplinario de hoy, las empresas innovadoras están utilizando la plataforma Altium 365™ para compartir fácilmente datos de diseño y poner proyectos en fabricación.

Solo hemos arañado la superficie de lo que es posible con Altium Designer en Altium 365. Comienza tu prueba gratuita de Altium Designer + Altium 365 hoy.