Enrutado de memorias DDR SDRAM: un caso real

Uno de los escenarios más comunes en el diseño de hardware es la inclusión de capacidad de almacenamiento en forma de memorias DDR SDRAM para acompañar a un procesador, FPGA o elemento inteligente. Hay ciertas pautas que es necesario seguir para lograr un enrutado adecuado, no sólo que funcione, sino que, además, presente un buen comportamiento en cuanto a emisiones electromagnéticas y a calidad de la señal. Analizaremos en este artículo dicho tema mediante un caso real.

La interfaz DDR

Conviene empezar aclarando el significado de las siglas DDR: es el acrónimo en lengua inglesa para Double Data Rate. Hace referencia al hecho de que la transferencia de datos hacia y desde la memoria se realiza tanto en flanco de subida como de bajada de reloj. Es decir, si tenemos un reloj de frecuencia X, la tasa de datos será de 2X.

Existen varias generaciones de DDR, algunas ya obsoletas, según la velocidad a la que se pueden transmitir los datos. Actualmente la versión DDR4 está en uso y se prevé que la version DDR5 lo esté en poco tiempo.

La interfaz creada a tal efecto se compone esencialmente de 4 grupos diferentes de señales:

- Reloj(es): se transmiten en modo diferencial (para ser más robustos en la recepción) y marcan los momentos en los que el resto de señales son muestreadas. Es el corazón del sistema.

- Datos: varias señales, a su vez, componen este subgrupo:

- Bus de datos: son las líneas por las que se transmiten los bits propiamente dichos en forma de señal digital. Son siempre un número múltiplo de 8 (recordemos que 8 bits conforman 1 byte).

- Mascara(s) de datos: se usan para enmascarar los datos en el ciclo de escritura, de tal manera que podamos usar ambos flancos de reloj en la transmisión. Por cada byte en el bus de datos, hay una línea de máscara.

- Activación de datos (Data strobe): es el reloj para el bus de datos. Al igual que el reloj general, se transmite en modo diferencial. Habrá tantos en la interfaz como canales de datos (generalmente, un canal de datos por cada byte).

- Dirección / comandos:

- Bus de direcciones: es el índice que nos permite acceder a una determinada posición de la memoria (o del conjunto de memorias). A diferencia del bus de datos (que es dedicado), el bus de direcciones es común a todos los chips de memoria que componen el sistema. Por ejemplo: 10 líneas de dirección nos permitirán acceder a 1024 posiciones distintas.

- Banco de direcciones: las memorias dividen su espacio en diferentes bancos. A efectos prácticos, pueden considerarse estas líneas como parte del bus de direcciones.

- Activación de fila (RAS): las memorias están organizadas físicamente en filas y columnas. Cuando la señal RAS se activa, el controlador puede acceder a la parte alta de un byte.

- Activación de columna (CAS): de modo análogo a la señal RAS, en este caso el controlador podría acceder a la parte baja de un byte determinado.

- Activación de escritura (Write enable): como su propio nombre indica, se aserta esta señal antes de producir un ciclo de escritura.

- Control:

- Activación de reloj (Clock enable): el reloj será válido sólo cuando esta señal se aserte. Habrá tantas como relojes en el sistema de memorias.

- Selección de chip (Chip select): el nombre de la señal explica perfectamente su función. Habrá tantas como chips en el sistema, lógicamente.

Chip frente a módulo

Las memorias DDR SDRAM se encuentran en el mercado en dos formas: directamente como chips (circuito integrado), o en módulos compuestos por varios chips que son insertables a través de una interfaz. En este último caso, se trata de una pequeña PCB ya diseñada y fabricada para su uso en una placa base, por ejemplo.

Ambos tienen sus ventajas y desventajas a la hora de diseñar una tarjeta de circuito impreso. En el caso de usar chips, tenemos mayor flexibilidad a la hora de configurar el sistema de memorias. Sin embargo, el enrutado será más complicado y deberemos prestarle más atención. En el caso del módulo, se invierten los papeles.

Topologías de enrutado

Refiriéndonos en este caso al uso de varios chips de memoria en nuestra PCB, podemos afrontar el problema desde dos perspectivas en lo que toca a las líneas comunes a todos las memorias:

- Fly-by: enrutamos las señales comunes a todos las memorias llevándolas sucesivamente y en orden al primer, segundo, enésimo chip. Desde el punto de vista de la integridad de la señal, esta es, sin duda, la topología adecuada. Se reduce al mínimo el número de stubs (derivaciones en las pistas) que afectan negativamente a la impedancia. Como contrapartida, se requiere de más espacio en la tarjeta para realizar el enrutado.

- T-branch (o bifurcación en T): en este caso, se bifurcan las señales comunes hasta alcanzar todos los chips. Esta topología implica necesariamente la creación de stubs y sus correspondientes discontinuidades en la impedancia de las pistas. El uso de terminaciones en las líneas es recomendable para paliar el efecto negativo de los stubs. Requiere, sin embargo, menos espacio en el PCB.

Caso real

Recientemente recibimos una petición de soporte por parte de otro grupo de trabajo dentro del Politécnico de Zurich. Se trataba de un diseño de una FPGA con procesador que precisaba de dos chips de memoria DDR3. El PCB ya había sido diseñado y fabricado, con múltiples errores en la parte concerniente a las memorias. Estando en fase de prototipado, se mandaron fabricar sólo 3 unidades, de las cuales se sospechan errores de soldadura bajo los BGAs (array de bolas) en dos de ellas. En la tercera, simplemente la tarjeta no superaba el test de diagrama de ojo.

En esta situación, resultaba imposible determinar si el error era exclusivamente de soldadura o de diseño (o ambos), ya que no teníamos prototipos suficientes para reproducirlo de forma idéntica en al menos dos tarjetas.

La topología elegida por el diseñador en este caso fue T-branch y el PCB constaba de 6 capas que hacían el enrutado bastante cómodo.

Tras un primer vistazo al diseño no se detectaron errores graves: cada señal estaba correctamente referenciada a un plano continuo de tierra y las longitudes de las mismas, en apariencia, eran correctas (quizás un poco más largas de lo estrictamente necesario). No se usaban terminaciones, pero, dada la relativa sencillez del sistema, no se consideran necesarias (bastaba con la terminación integrada en el chip). Entonces, ¿dónde residía el error? Veamos.

Reglas de diseño

Antes de continuar, resumamos brevemente qué reglas de diseño debemos respetar en lo que refiere a tiempos (longitudes) de propagación de las señales. Vaya por delante que siempre es necesario estudiar las recomendaciones del fabricante. A grandes rasgos, serían:

- Las señales deben ser lo más cortas posible. Una longitud aceptable sería de 5mm.

- El grupo más largo de la interfaz es el de los relojes. La razón es que éstos muestrean el resto de señales en sus flancos. Es decir, todas las señales a muestrear tienen que ser ya estables cuando el flanco de reloj suceda. La diferencia de longitud dentro de cada par diferencial debería estar en el margen de +-0.125mm.

- Podemos dividir el grupo de datos en tantos subgrupos como bytes tengamos. Ninguna señal dentro de este grupo debera superar la longitud mínima de los relojes. Las longitudes de cada subgrupo pueden ser distintas, siempre que dentro de cada uno de ellos, consigamos una ecualización de +-0.250mm para el par diferencial de activación de datos (Data strobe) y de +-0.635mm para el resto de señales del subgrupo.

- Los grupos de dirección / comandos y control no deben superar la longitud mínima de los relojes. Las señales dentro de estos tres grupos deben estar ecualizadas entre ellas en un margen de +-0.635mm (este dato puede variar dependiendo del tipo de DDR. Consultar siempre la hoja de datos del fabricante). Recordemos que estas señales son comunes a todos los chips. Por tanto, es vital que tomemos las longitudes de origen a destino, no el total de la línea. Por ejemplo, la señal de A0 parte de un pin del procesador y, por medio de una bifurcación, llega a los dos chips de memoria. La distancia desde el procesador a cada uno de los chips es la que tenemos que ecualizar. Es decir: tenemos una única señal pero dos ecualizaciones que realizar.

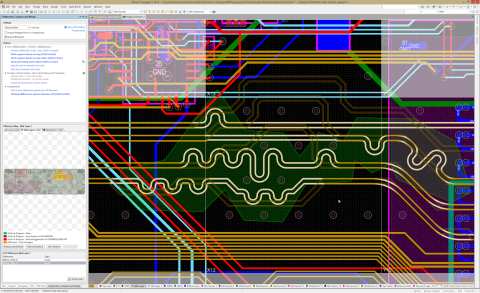

El error

Un segundo análisis más en profundidad del layout en cuestión nos revela el error de diseño: analizando las longitudes de los grupos de dirección / comandos y control a través del panel PCB de Altium, no se aprecia, a priori, ningún error. Sin embargo, las longitudes que estamos observando son las de la pista completa cuando lo que deberíamos analizar es las longitudes reales de emisor a receptor de cada chip. Por tanto, las ecualizaciones de las líneas de dirección / comandos y control eran completamente erróneas en realidad.

Por desgracia, la solución pasa por un rediseño de la tarjeta. La palabra clave es Xsignal.

Xsignals

Altium nos permite definir una señal de punto a punto. El nombre técnico es Xsignal. Deberemos primero definirlas de manera muy sencilla: seleccionamos los dos pads de origen y destino (pueden ser de Nets diferentes) y hacemos click con el botón derecho. Obtenemos esto:

Podemos acceder a todas las Xsignals mediante el panel PCB:

Las Xsignals pueden ser usadas en el mismo modo que cualquier otra Net dentro de las reglas de diseño (creando clases, por ejemplo) y así conseguir nuestro objetivo de líneas perfectamente ecualizadas de extremo a extremo. Es una herramienta potentísima y tremendamente útil.